# COIMBRA

## Martin Estorninho Blocher

## Solid-State Transformer Application For a Grid-Connected Energy Storage System

#### VOLUME 1

Dissertation in the context of the Master in Electrical and Computer Engineering, Specialization in Energy, advised by Professor Doctor André Mendes and presented to the Department of Electrical and Computer Engineering at the Faculty of Sciences and Technology of the University of Coimbra.

September 2022

# UNIVERSIDADE Ð COIMBRA

Martin Estorninho Blocher

### SOLID-STATE TRANSFORMER APPLICATION FOR A GRID-CONNECTED ENERGY STORAGE SYSTEM

Dissertation in the context of the Master in Electrical and Computer Engineering, Specialization in Energy, and presented to the Department of Electrical and Computer Engineering at the Faculty of Sciences and Technology of the University of Coimbra.

Supervisors: Prof. Doutor André Manuel dos Santos Mendes

Jury: Prof. Doutor Sérgio Manuel Ângelo da Cruz Prof. Doutor Luís Miguel Pires Neves

Coimbra, 2022

Esta dissertação foi realizada no Laboratório de Sistemas de Energia do Instituto de Telecomunicações - Coimbra, tendo sido financiado em parte pela FCT-OE através do projeto UID/EEA/50008/2020.

## Agradecimentos

Em primeiro lugar gostaria de agradecer ao meu orientador, Professor Doutor André Mendes, pelo acompanhamento, paciência e dedicação, sobretudo na reta final, tornando possível a conclusão desta dissertação e consequentemente da minha formação. Uma palavra de agradecimento aos membros do IT pelo contributo, em especial João Duarte, Luís Caseiro e Tiago Oliveira. E aproveito ainda para deixar o meu reconhecimento a toda a comunidade do DEEC, colegas e funcionários, em especial ao Sr. Vítor por acompanhar os momentos de pausa sempre com boa disposição e prazer em servir.

Gostaria também de deixar uma palavra especial de agradecimento a todos os professores que de alguma maneira contribuíram para a minha formação, estimulando ainda mais o meu gosto pela engenharia, em particular os professores do ramo de Energia. Todos em conjunto reforçaram a convicção em mim de que fiz a escolha acertada em ingressar neste curso. Obrigado.

Aos meus amigos de Faculdade, que me acompanharam desde o primeiro dia que pisei o chão deste Departamento, por me acompanharem nos bons e maus momentos desta caminhada, suavizando-a, sem dúvida; aos meus amigos de secundário e longa data, por manterem sempre um olho em mim apesar dos rumos de vida tomados, completamente distintos e por fim, um abraço grato e especial à minha explicadora de básico/secundário por incutir métodos de estudo que foram essenciais para o meu sucesso académico. Espero que estejam todos orgulhosos.

Por último, mas seguramente mais importante, à minha família, por me terem proporcionado tudo o que um rapaz com aspirações fortes pode almejar: o meu pai, que me incutiu um lado mais sério, responsável e ambicioso; o meu avô e mãe, por terem formado a parte mais humana de mim, através d'um trato cheio de amor e valores fortes que levarei para o resto da minha vida. A vós, em particular, dedico-vos estas palavras carregadas de agradecimento e carinho e dedico-vos este percurso. Eternamente grato.

Martin Estorninho Blocher

## Abstract

The energy sector is undergoing a major change as global warming urges governments to react. This implies shifting the existing electrical infrastructure toward decentralized power generation while increasing the share of Renewable Energy Sources (RES). This transition requires the implementation and development of new technologies capable of integrating Distrusted Energy Sources (DES), while maintaining the overall Power Quality (PQ) of the system. The Solid-State Transformer (SST) is an emerging technology that will gradually replace the classical Low-Frequency Transformer (LFT) once it can integrate DES and provide needed ancillary services to the electrical grid. This dissertation presents the study of a bidirectional SST application to integrate a Battery Storage System (BSS) into the high voltage electrical grid. For this a two-stage conversion SST was developed. The Modular Multilevel Converter (MMC) with a Model Predictive Control (MPC) algorithm was selected for the first stage's design due to its modularity and scalability while maintaining the system's PQ. The Dual Active Bridge (DAB) converter with Phase Shift Modulation Control was elected for the second stage, connecting the BSS to the first conversion stage while providing galvanic isolation to the system. The MMC characteristics were the primary focus of this research. These characteristics included several control objectives, such as circulating current minimization and submodule voltage balancing, as well as the converter's ability to cope with system fluctuations such as grid voltage disturbances or component parameter variations. In this work, a brief State of the Art of SST technology is presented, followed by the system's complete configuration, modelling, and control system. Finally, a simulation in a Matlab/Simulink environment is undertaken to validate the research made. The results reveal that the system is capable of charging and discharging the BSS at varying rates while maintaining an adequate overall system PQ.

*Keywords*— Power Distribution, Solid-State Transformer, Power Electronics, Modular Multilevel Converter, Energy Storage Systems.

## Resumo

O setor energético está a sofrer uma mudança significativa à medida que o aquecimento global pressiona os governos a atuarem. Em consequência, na infraestrutura da rede elétrica existente, observa-se uma transição para uma geração mais descentralizada aumentando assim a percentagem de fontes de energia renováveis. Esta requer a implementação e desenvolvimento de novas tecnologias capazes de integrar fontes de energia distribuídas, mantendo em simultâneo a qualidade de potência na rede. O transformador de estado sólido é uma tecnologia emergente que irá gradualmente substituir o transformador de baixa frequência, já que consegue integrar este tipo de fontes de energia e fornecer serviços auxiliares à rede necessários para manter a sua qualidade de potência. Esta dissertação apresenta o estudo de um transformador de estado sólido bidirecional para a integração de um sistema de baterias à rede elétrica. Assim, desenvolveu-se um transformador de estado sólido com dois estágios de conversão e foi eleito o conversor multinível modular com uma estratégia de controlo de modelo preditivo para o primeiro estágio, devido à sua modularidade e escalabilidade, garantindo a qualidade de potência do sistema. Para a ligação do sistema de baterias ao primeiro estágio optou-se pelo conversor DC-DC de dupla ponte ativa, já que este fornece isolamento galvânico ao sistema. O conversor modular de multinível foi o principal foco deste estudo com uma análise profunda sobre as suas características. Vários objetivos de controlo como a minimização das correntes circulantes e o equilíbrio das tensões dos seus submódulos foram analisados, bem como a capacidade do conversor em lidar com flutuações, tais como perturbações nas tensões da rede ou variações dos parâmetros dos seus componentes. Esta dissertação inicia-se com um breve estado da arte deste tipo de transformadores, seguida da configuração, modelização e estratégia de controlo para o sistema desenvolvido. Finalmente, os resultados obtidos através de uma simulação em ambiente Matlab/Simulink são discutidos, de forma a validar este estudo. Estes vão demonstrar que o sistema é capaz de carregar e descarregar o sistema de baterias a vários níveis, não afetando a qualidade de potência ao longo do sistema.

*Palavras-Chave*— Distribuição de Potência, Transformador de Estado Sólido, Eletrónica de Potência, Conversor Modular de Multinível, Sistemas de Armazenamento de Energia.

## **List of Figures**

| 1.1 | Basic Structure of the SST based on [36].                                                                                 | 3  |

|-----|---------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | SST configurations: a) Single-stage, b) Two-stage with MVDC-link, c) Two-stage                                            |    |

|     | with LVDC-link, d) Three-stage. Image taken from [33]                                                                     | 4  |

| 1.3 | SST modular-multilevel configurations in HV and high-power systems: a) ISOP,                                              |    |

|     | b) ISOS, c) ISOS. Image taken from [36].                                                                                  | 4  |

| 1.4 | Circuit schemactic of AC-DC converters: a) NPC; b) CHB; c) MMC. Taken from [23].                                          | 8  |

| 1.5 | Circuit schemactic of DC-DC converters: a) DAB [23]; b) DAB with SRC [23];<br>c) DHB [21].                                | 10 |

| 1.6 | Circuit schemactic of DC-AC converters: a) HB [31]; b) H-Bridge [31]; c) NPC                                              |    |

|     | [19]                                                                                                                      | 11 |

| 1.7 | HFT equivalent circuit schematic referred to primary. Taken from [22]                                                     | 12 |

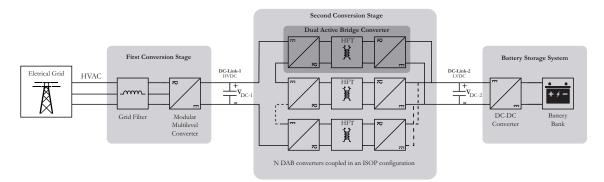

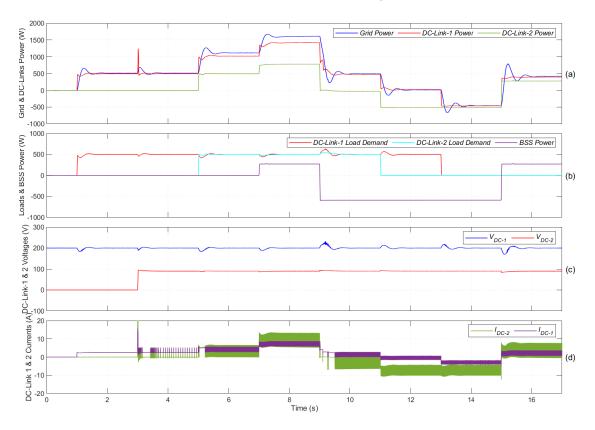

| 2.1 | Proposed system to integrate the BSS to the HVAC electrical grid.                                                         | 15 |

| 2.2 | MMC & SM configuration.                                                                                                   | 17 |

| 2.3 | Dual active bridge topology.                                                                                              | 19 |

| 2.4 | BSS configuration.                                                                                                        | 20 |

| 3.1 | Equivalent model of MMC.                                                                                                  | 22 |

| 3.2 | Equivalent model of HB-SM.                                                                                                | 25 |

| 3.3 | Lossless model of the DAB converter.                                                                                      | 26 |

| 4.1 | Block diagram of MPC.                                                                                                     | 31 |

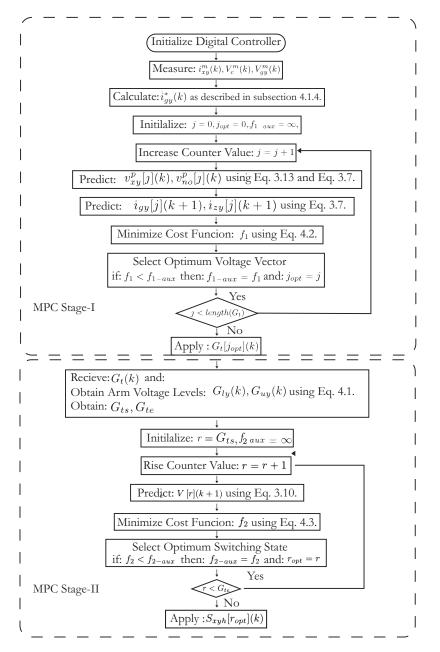

| 4.2 | Flowchart of the dual-stage MPC.                                                                                          | 34 |

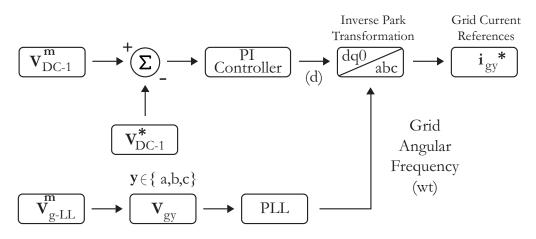

| 4.3 | Representative diagram of the grid current references calculation.                                                        | 36 |

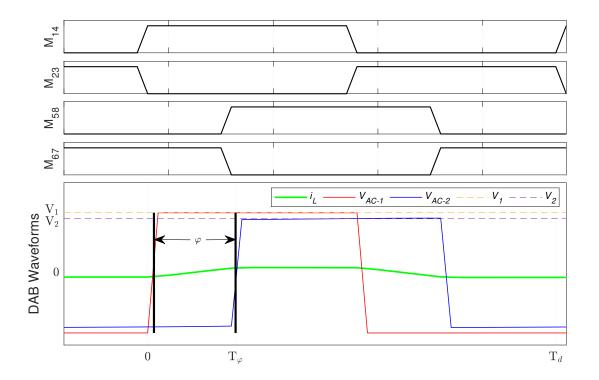

| 4.4 | Drive signal and corresponding current and voltage waveforms in the DAB with                                              |    |

|     | the SPS control.                                                                                                          | 37 |

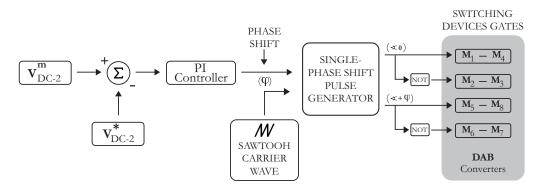

| 4.5 | Representative diagram of DC-Link-2 voltage loop for DAB converter control.                                               | 40 |

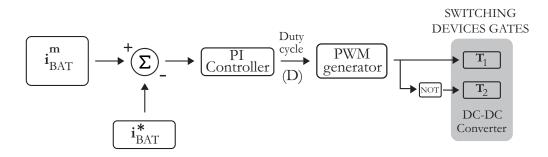

| 4.6 | Representative diagram of battery pack current loop for DC-DC converter control.                                          | 40 |

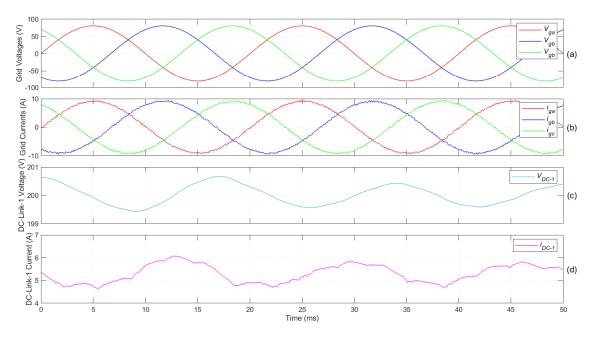

| 5.1 | First stage steady-state performance: (a) Grid voltages. (b) Grid currents. (c) DC-Link-1 Voltage. (d) DC-Link-1 Current. | 42 |

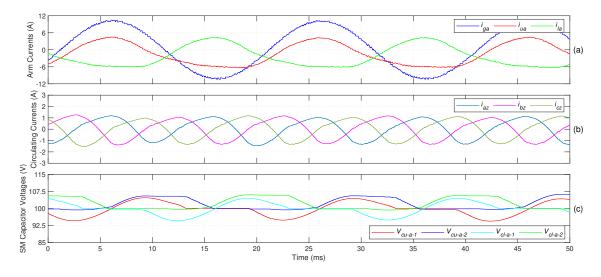

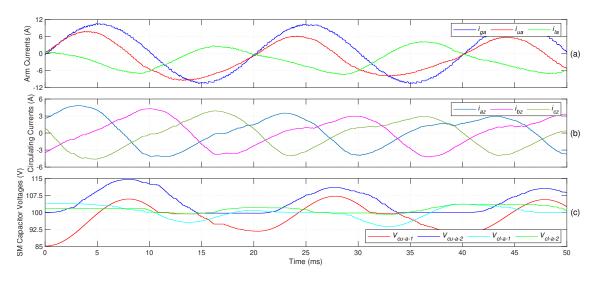

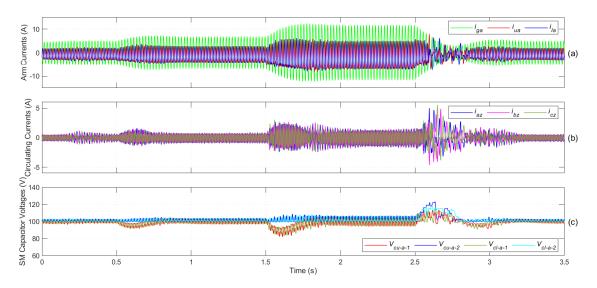

| 5.2  | MMC steady-state performance: (a) Arm Currents phase-a. (b) Circulating cur-              |    |

|------|-------------------------------------------------------------------------------------------|----|

|      | rents all phases. (c) SMs Capacitor voltages, phase-a.                                    | 43 |

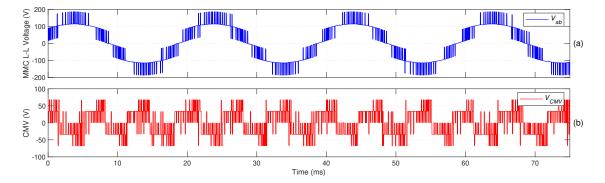

| 5.3  | MMC steady-state performance: (a) Line-to-line voltage. (b) Common-mode volt-             |    |

|      | age                                                                                       | 43 |

| 5.4  | MMC steady-state performance (with $\lambda_1 = 0$ ): (a) Arm Currents phase-a. (b)       |    |

|      | Circulating currents all phases. (c) SMs Capacitor voltages, phase-a.                     | 44 |

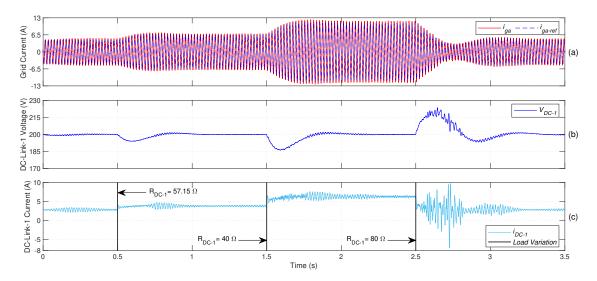

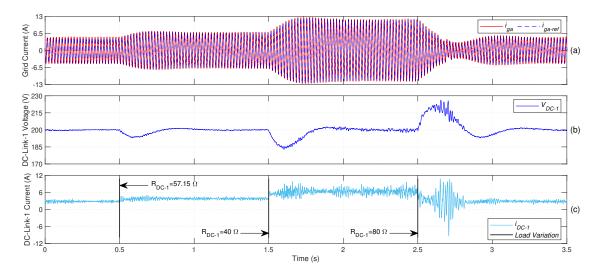

| 5.5  | First stage dynamic performance: (a) Grid currents. (b) DC-Link-1 Voltage. (c)            |    |

|      | DC-Link-1 Current.                                                                        | 45 |

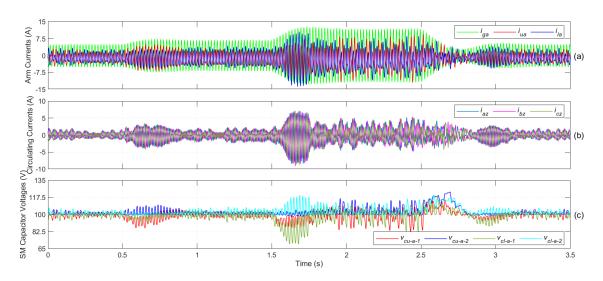

| 5.6  | MMC dynamic performance: (a) Arm Currents phase-a. (b) Circulating currents               |    |

|      | all phases. (c) SMs Capacitor voltages, phase-a.                                          | 46 |

| 5.7  | First stage dynamic performance (with $\lambda_1 = 0$ ): (a) Grid currents. (b) DC-Link-1 |    |

|      | Voltage. (c) DC-Link-1 Current.                                                           | 47 |

| 5.8  | MMC dynamic performance (with $\lambda_1 = 0$ ): (a) Arm Currents, phase-a. (b) Circu-    |    |

|      | lating currents. (c) SMs Capacitor voltages, phase-a.                                     | 48 |

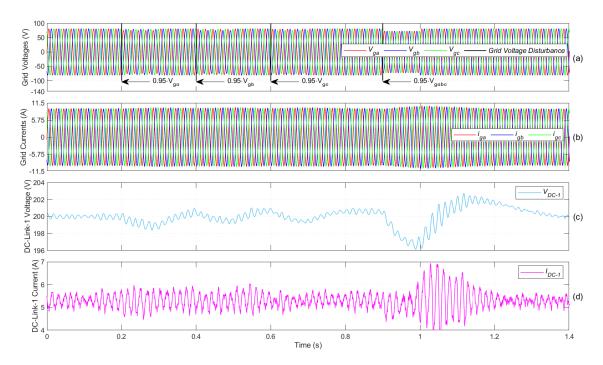

| 5.9  | First stage performance under grid voltage disturbances: (a) Grid Voltages. (b)           |    |

|      | Grid Currents. (c) DC-Link-1 Voltage. (d) DC-Link-1 Current.                              | 49 |

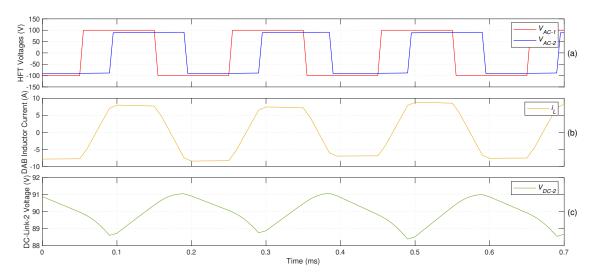

| 5.10 | Second stage steady-state performance: (a) HFT's Winding Voltages. (b) DAB                |    |

|      | Inductor Current. (c) DC-Link-2 Voltage.                                                  | 52 |

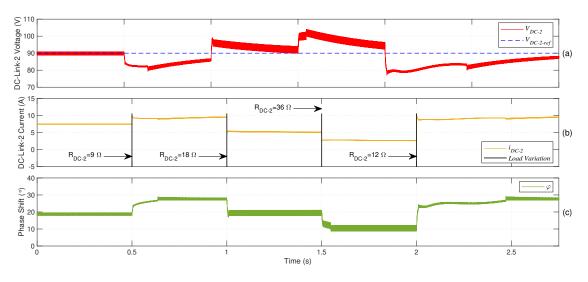

| 5.11 | Second stage dynamic performance: (a) DC-Link-2 Voltage. (b) DC-Link-2 Cur-               |    |

|      | rent. (c) DAB's phase shift.                                                              | 52 |

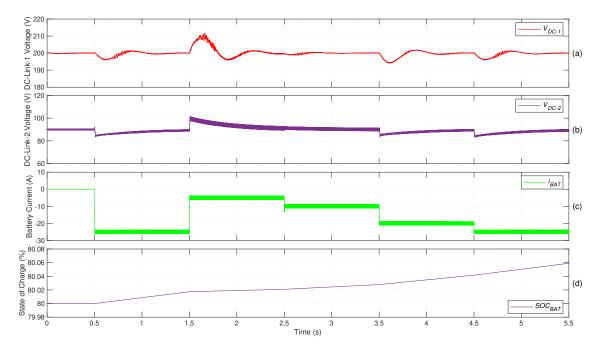

| 5.12 | BSS charging at different rates:(a) DC-link-1 Voltage. (b) DC-link-2 Voltage. (c)         |    |

|      | Battery Pack Current. (d) Battery Pack SOC.                                               | 53 |

| 5.13 | BSS discharging at different rates:(a) DC-link-1 Voltage. (b) DC-link-2 Voltage.          |    |

|      | (c) Battery Pack Current. (d) Battery Pack SOC.                                           | 54 |

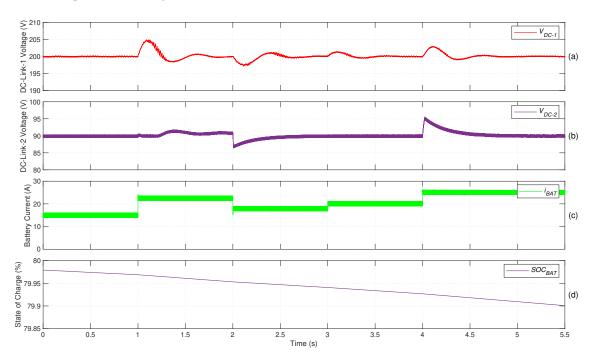

| 5.14 | Power-flow analysis: (a) Grid Power. (b) Battery Pack Power. (c) DC-Link 1 & 2            |    |

|      | Voltages. (d) DC-Link 1 & 2 Currents.                                                     | 55 |

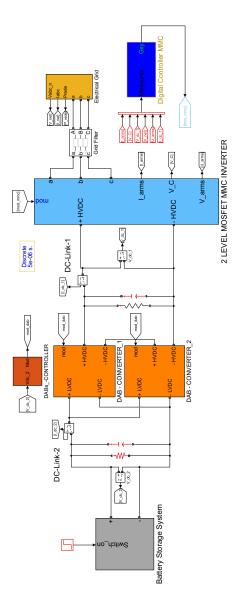

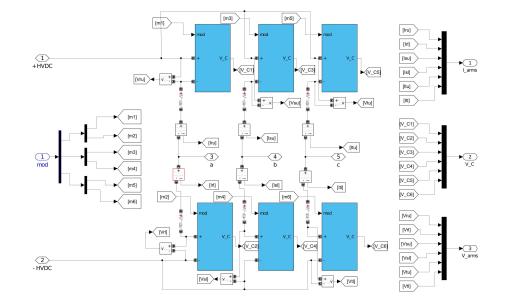

| 7.1  | SST simulation model.                                                                     | 62 |

| 7.2  | MMC simulation model.                                                                     | 63 |

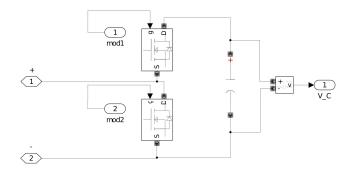

| 7.3  | HB-SM simulation model.                                                                   | 63 |

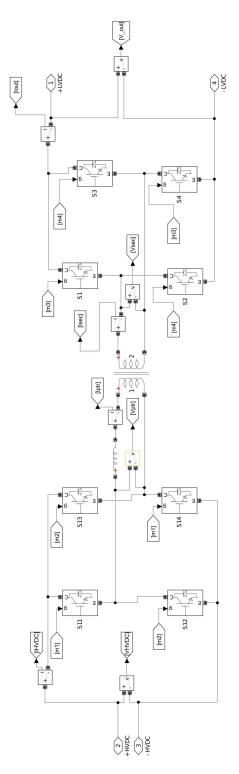

| 7.4  | DAB simulation model.                                                                     | 64 |

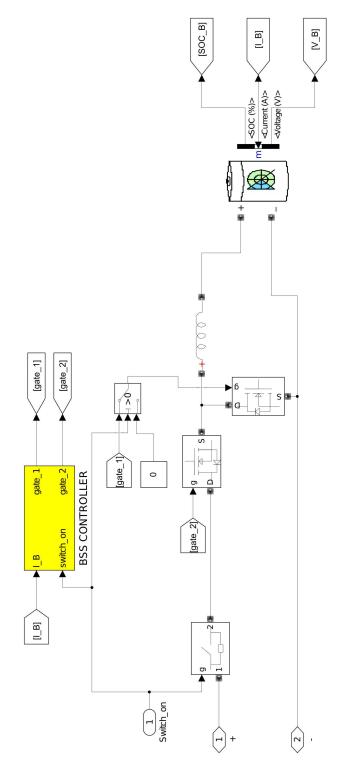

| 7.5  | BSS simulation model.                                                                     | 65 |

## **List of Tables**

| 1.1 | SSTs' topologies capabilities comparison [18] [23] [14] [34]                         | 7  |

|-----|--------------------------------------------------------------------------------------|----|

| 1.2 | Comparison between the different AC-DC converters [18] [14] [23] [31].               | 8  |

| 1.3 | Comparison between the different DC-DC converters [18] [31] [23] [26] [38]           | 9  |

| 1.4 | Comparison between the different DC-AC converters[18] [31] [23] [26] [37] [14].      | 10 |

| 3.1 | Full bridge switching states.                                                        | 27 |

| 5.1 | First stage performance values with and without CC control.                          | 44 |

| 5.2 | First stage performance values with grid filter inductance variations in phase a.    | 49 |

| 5.3 | First stage performance values with grid filter inductance variations in all phases. | 50 |

| 5.4 | First stage performance values with MMC arm inductance variations in phase a         | 50 |

| 5.5 | First stage performance values with MMC arm inductance variations in all phases.     | 51 |

| 7.1 | System parameters.                                                                   | 66 |

## **List of Abbreviations**

| AC Alternating Current.                             |

|-----------------------------------------------------|

| BSS Battery Storage System.                         |

| CC Circulating Current.                             |

| CMV Common-Mode Voltage.                            |

| DAB Dual-Active Bridge.                             |

| DC Direct Current.                                  |

| <b>DES</b> Distributed Energy Sources.              |

| ESS Energy Storage Systems.                         |

| HB-SM Half-Bridge Submodule.                        |

| HF High-Frequency.                                  |

| HFT High-Frequency Transformer.                     |

| HV High-Voltage.                                    |

| <b>IPOP</b> Input Parallel Output Parallel.         |

| <b>IRENA</b> International Renewable Energy Agency. |

| <b>ISOP</b> Input Series Output Parallel.           |

| <b>ISOS</b> Input Series Output Series.             |

| LFT Low-Frequency Transformer.                      |

| LV Low-Voltage.                                     |

| MMC Modular Multilevel Converter.                   |

| MPC Model Predictive Control.                       |

| MV Medium-Voltage.                                  |

| <b>OSS</b> Optimal Switching State.                 |

- **OSV** Optimal Switching Vector.

- **OVL** Optimal Voltage Level.

- **PI** Proportional-Integral.

- PLL Phase-Locked-Loop.

- **PQ** Power Quality.

- **PWM** Pulse-Width Modulation.

- **RES** Renewable Energy Sources.

- SiC Silicon Carbide.

- SM Submodule.

- SOC State of Charge.

- SPS Single-Phase Shift.

- SST Solid-State Transformer.

- **THD** Total Harmonic Distortion.

- ZVS Zero Voltage Switching.

#### Nomenclature

| $V_g$      | Rated grid phase voltage           |

|------------|------------------------------------|

| $V_{ll}$   | Rated grid line-to-line voltage    |

| $V_{DC-1}$ | DC-Link-1 voltage                  |

| $V_{DC-2}$ | DC-Link-2 voltage                  |

| $i_{DC-1}$ | DC-Link-1 current                  |

| $i_{DC-2}$ | DC-Link-2 current                  |

| N          | Number of SMs used in all MMC arms |

| n          | Grid source common point           |

| 0          | DC-Link-1 midpoint                 |

| $L_m$      | MMC arm inductor                   |

| $r_m$      | MMC arm inductor resistance        |

| $L_d$      | DC-Link-1 cable inductance         |

| $L_r$             | DC-Link-1 cable resistance                           |

|-------------------|------------------------------------------------------|

| $L_f$             | Grid filter inductor                                 |

| $r_f$             | Grid filter inductor resistance                      |

| $quantity^m$      | Measured quantity                                    |

| $quantity^p$      | Predicted quantity                                   |

| $T_{sc}$          | MMC controller sampling time                         |

| r                 | Control Variable                                     |

| $r^*$             | Control Variable Reference                           |

| $x \in \{u,l\}$   | MMC upper( <i>u</i> )/lower( <i>l</i> ) arm          |

| $y \in \{a,b,c\}$ | MMC/Grid phase                                       |

| $h \in \{1N\}$    | Number of SMs in one MMC arm                         |

| $V_{xy}$          | MMC arm voltages                                     |

| $i_{xy}$          | MMC arm currents                                     |

| $i_{zy}$          | MMC circulating currents                             |

| $i_{gy}$          | Grid Phase currents                                  |

| $V_{no}$          | MMC CMV term                                         |

| $V_{cxyh}$        | HB-SM capacitor voltage                              |

| $i_{cxyh}$        | HB-SM capacitor current                              |

| $V_{SM}$          | SM capacitor voltage                                 |

| $S_{xyh}$         | MMC HB-SM optimal switching state                    |

| $G_{xy}$          | MMC Arm voltage level                                |

| $G_t$             | MMC voltage vector                                   |

| $f_1$             | MPC Stage-I cost function                            |

| $\lambda_0$       | Grid current weighting factor used in $f_1$          |

| $\lambda_1$       | Circulating currents weighting factor used in $f_1$  |

| $f_2$             | MPC Stage-II cost function                           |

| $\lambda_v$       | SM capacitors voltage weighting factor used in $f_2$ |

| $M_{1-8}$    | DAB converter MOSFETS                              |

|--------------|----------------------------------------------------|

| $N_{DAB}$    | Number of DABs used in the second conversion stage |

| $L_{DAB}$    | DAB external energy transfer inductor              |

| $L_k$        | DAB equivalent inductance                          |

| $V_1$        | DAB HVDC-Link rated voltage                        |

| $V_2$        | DAB LVDC-Link rated voltage                        |

| $V_{AC-1/2}$ | Squarewave voltages applied to the HFT's terminals |

| $f_d$        | DAB switching frequency                            |

| $T_d$        | DAB switching cycle                                |

| $V_l$        | Voltage across $L_k$                               |

| $i_l$        | Current flowing through $L_k$                      |

| arphi        | Phase Shift between $V_{AC-1}$ and $V_{AC-1}$      |

| $T_{1-2}$    | BSS DC-DC converter MOSFETS                        |

| $V_{BAT}$    | Battery Pack voltage                               |

| $i_{BAT}$    | Battery Pack current                               |

| $L_{BAT}$    | Battery Pack filter inductor                       |

## Contents

| Li | st of l | Figures       |                                           | ix   |

|----|---------|---------------|-------------------------------------------|------|

| Li | st of [ | <b>Fables</b> |                                           | xi   |

| Li |         | Abbrevi       |                                           | xii  |

|    | Non     | nenclatu      | re                                        | xiii |

| 1  | Intr    | oductio       | n                                         | 1    |

|    | 1.1     | Contex        | xt and Motivation                         | 1    |

|    | 1.2     | State c       | of the Art                                | 3    |

|    |         | 1.2.1         | Solid-State Transformer                   | 3    |

|    |         | 1.2.2         | Overview of SST architectures             | 4    |

|    |         | 1.2.3         | Single-Stage Topology                     | 4    |

|    |         | 1.2.4         | Two-Stage Topology                        | 5    |

|    |         |               | 1.2.4.1 Two-Stage Topology with LVDC-link | 5    |

|    |         |               | 1.2.4.2 Two-Stage Topology with MVDC-link | 6    |

|    |         | 1.2.5         | Three-Stage Topology                      | 6    |

|    |         | 1.2.6         | SST Topology Comparison                   | 7    |

|    |         | 1.2.7         | Overview of the Connection Stages         | 8    |

|    |         |               | 1.2.7.1 MVAC - MVDC connection stage      | 8    |

|    |         |               | 1.2.7.2 MVDC-LVDC connection stage        | 9    |

|    |         |               | 1.2.7.3 LVDC-LVAC connection stage        | 10   |

|    |         | 1.2.8         | High-frequency transformer                | 11   |

|    |         | 1.2.9         | SST Applications                          | 12   |

|    | 1.3     | Disser        | tation Objectives and Structure           | 13   |

| 2  | Proj    | posed S       | ystem                                     | 15   |

|    | 2.1     |               | Conversion Stage                          | 16   |

|    |         | 2.1.1         | MMC Configuration                         | 16   |

|    |         | 2.1.2         | Configuration of SMs                      | 17   |

|    |         | 2.1.3         | Grid Filter                               | 17   |

|    | 2.2     | Secon         | d Conversion Stage                        | 18   |

|   |            | 2.2.1     | Dual-Active Bridge                             |

|---|------------|-----------|------------------------------------------------|

|   | 2.3        | Battery   | Storage System                                 |

| • | <b>a</b> . |           |                                                |

| 3 | ·          | em Mod    | 6                                              |

|   | 3.1        |           | e-time model of the MMC converter              |

|   |            | 3.1.1     | Modelling of the Converter                     |

|   |            | 3.1.2     | Modelling of the HB-SM and Arm Voltage         |

|   | 3.2        |           | Converter                                      |

|   |            | 3.2.1     | Steady-State Analysis                          |

| 4 | Syst       | em Con    | trol 29                                        |

|   | 4.1        | Control   | l of the MMC                                   |

|   |            | 4.1.1     | Control objectives                             |

|   |            | 4.1.2     | Model Predictive Control of MMC                |

|   |            |           | 4.1.2.1 Model Predictive Control Methodologies |

|   |            | 4.1.3     | Dual-Stage MPC   33                            |

|   |            | 4.1.4     | Reference Current Generation                   |

|   | 4.2        | Control   | l of DAB                                       |

|   |            | 4.2.1     | Phase Shift Modulation                         |

|   |            | 4.2.2     | Phase Shift Voltage Loop                       |

|   | 4.3        | Control   | l of DC-DC converter                           |

| _ | ~.         |           |                                                |

| 5 |            | ulation I |                                                |

|   | 5.1        |           | onversion Stage                                |

|   |            | 5.1.1     | Steady-State Performance Analysis              |

|   |            |           | 5.1.1.1 Circulating Current Control Turned Off |

|   |            | 5.1.2     | Dynamic Performance Analysis                   |

|   |            |           | 5.1.2.1 Circulating Current Control Turned Off |

|   |            | 5.1.3     | Grid Voltage Disturbance Analysis              |

|   |            | 5.1.4     | MPC Parameter Variation Robustness Analysis    |

|   |            |           | 5.1.4.1 Grid Filter Inductance Variation       |

|   |            |           | 5.1.4.2 MMC Arm Inductance Variation           |

|   | 5.2        |           | Conversion Stage                               |

|   |            | 5.2.1     | Steady-State Performance Analysis              |

|   |            | 5.2.2     | Dynamic Performance Analysis                   |

|   | 5.3        | Battery   | Storage System                                 |

|   |            | 5.3.1     | Control Analysis                               |

|   |            |           | 5.3.1.1 Battery Charging                       |

|   |            |           | 5.3.1.2 Battery Discharging                    |

|   | 5.4        | Power-    | flow Analysis                                  |

|   |            |           |                                                |

| 6 | Conclusion | and | Future  | Work     |

|---|------------|-----|---------|----------|

| • | conclusion |     | I uturt | ,, , , , |

| 6.1<br>6.2 | Conclusions                                    |    |

|------------|------------------------------------------------|----|

| Bibliog    | raphy                                          | 58 |

| Append     | lixes                                          | 62 |

| 7.1        | Overall SST Simulation Model                   | 62 |

| 7.2        | MMC & HB-SM Simulation Model                   | 63 |

| 7.3        | DAB Simulation Model                           | 64 |

| 7.4        | BSS Simulation Model                           | 65 |

| 7.5        | System Parameters used in the Simulation Model | 66 |

| 7.6        | MPC Stage-I Algorithm Implementation           | 67 |

| 7.7        | MPC Stage-II Algorithm Implementation          | 71 |

### **Chapter 1**

## Introduction

#### **1.1** Context and Motivation

Power generation, distribution and transmission are the three main stages of the power system in which transformers play an essential role. The traditional Low-Frequency Transformer (LFT) is a rigid, reliable and long-life expectancy (more than 35 years [25]) machine that can handle harsh environmental conditions and still work with high efficiency (up to 99.5%) [34]. The LFT main function consists in regulating the voltage to the desired level through a tap changer. For instance, the voltage must be increased at the generation stage so the power can be fed into a High-Voltage (HV) transmission line. This lines may be up to hundreds of kilometres in length, which would translate to an extremely significant energy loss were they not working at HV. The LFT is also implemented at the distribution stage, usually in substations near the power demand. The HV is then stepped down to the desired level to be fed to distribution lines, which supply industrial, commercial and residential users.

Although the electrical power system has been highly reliable, it is undergoing a transition. As society struggles with ever-increasing challenges due to global warming, environmental agreements, such as the Kyoto and Paris Agreements, were implemented in several world nations. Thus, governments are pushing for Renewable Energy Sources (RES) (*e.g.*, photovoltaics, wind turbines, etc.) to be incorporated in our traditional fossil fuel-based power system. Moreover, the decentralization of power generation, known as *microgeneration*, incentivizes the creation of new enterprises within the energy sector. In Europe, this was mainly possible through the market liberalization [34].

Nonetheless, these developments cause the network layout and operation to become more complex. According to the International Renewable Energy Agency (IRENA), such a transition should address four major challenges [1]:

- Enabling bidirectional energy flow;

- Improving grid interconnection namely, integration of Distributed Energy Sources (DES)

and communication systems within the network (Smart Grids);

- Adopting enhanced technologies mainly those of considerable electrical loads, for instance, the electric vehicle in the transport sector or the heat pump in the heating sector [23];

- Increasing Energy Storage Systems (ESS) crucial for peak demand response in a decentralized scenario.

Moreover, DES integration also results in Power Quality (PQ) issues, particularly, power flow control or the injection of overvoltages to the end-user. The latter usually occurs during off-peak regimes and may be mitigated through a decrease in the output energy or, in extreme cases, by disconnecting them from the grid. However, these solutions translate into less rentability for the exploring enterprises, since they extend the return on investment, disincentivizing the exploration of RES [27]. To simultaneously address IRENA's four challenges and solve DES integration issues in future smart grids, the LFT must be replaced by the Solid-State Transformer (SST).

The main discrepancy in these two technologies comes down to their volumes. The LFT is known for its bulky size, limiting its implementation in certain critical size applications. The SST is equipped with a High-Frequency Transformer (HFT), which allows for a quicker and more dynamical voltage control while also providing galvanic isolation. This contrasts with LFTs, which depend on mechanical tap changers and have limited voltage control (*e.g.*, switching between applications with considerable differences in voltage needs would require a completely new tap changer). Moreover, the High-Frequency (HF) is responsible for the SST's major size reduction, up to 80% [18]. Naturally, its reduced size translates into higher portability, lower installation costs, and easiness in the assembly process, specifically in certain areas such as in offshore applications [18]. Although the first generation of SSTs comes at a higher cost, the decreasing price in semiconductors and control circuitry will gradually allow for SSTs' overall price decrease [34]. Arguably, the SST structure has a higher degree of complexity due to the high number of switching devices, resulting in less reliability and efficiency (up to 98% [34]. Nevertheless, the LFT does not provide a large part of the ancillary services<sup>1</sup> and features that the SST does, which vastly increase the PQ and are crucial for the transition mentioned above.

Some of the SSTs' characteristics absent in LFTs include disturbances blocking, such as harmonics or voltage sag, and power flow control, either active or reactive. Reactive power control allows the regulation of the power factor, independently of load characteristics. Additionally, SSTs may be equipped with a Direct Current (DC) Link allowing for DC applications' integration, such as RES, ESS, or, more recently, DC transmission lines. For such purposes, the LFT would first have to be connected to additional converters, resulting in larger sizes, higher costs and lower efficiency and reliability.

The sections that follow provide an overview of the state of the art in SSTs. Various topologies of this developing technology will be demonstrated, along with its auxiliary services (*e.g.*, power

<sup>&</sup>lt;sup>1</sup>Ancillary services - necessary services to support electric power transmission from generators to consumers, considering the control area obligations (*e.g.*, line frequency) and transmitting infrastructure requirements. These are key to maintain the system's operation reliability [30]

output control, voltage regulation). The fundamental component of the SST, the HFT, is also discussed, as well as the major design issues it faces. The dissertation objectives are presented after an examination of current SST applications.

#### **1.2** State of the Art

#### 1.2.1 Solid-State Transformer

The concept of a "solid-state transformer" was first discussed in 1968 by W. McMurray, when he introduced a device based on solid-state switches. He introduced an Alternating Current (AC) converter with HF isolation that behaved like a traditional transformer [31]. The first real application for the SST appeared later, in the 1990s, in traction systems, where the traditional LFTs provided a bulky, heavy, and space inefficient solution. Engineers found solutions for these issues in the development of SST applications [23].

Considering the development of power electronic circuits and devices (*e.g.*, Silicon Carbide (SiC) MOSFETs), the SST becomes a viable option to replace the LFT in the power distribution system. Moreover, they bring several other ancillary services which provide the system with better PQ.

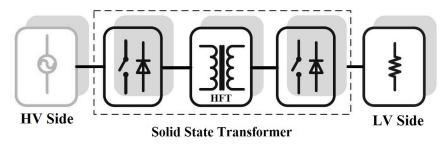

Depending on the application, a SST has different configurations, having several power conversion steps. Most topologies use an HFT that provides galvanic isolation to the system and is responsible for most of the size reduction compared to an LFT [29] [27]. The SST base functioning consists of converting a low-frequency voltage input, usually grid supplied (50-60 Hz), into a HF voltage. This process happens through switching circuits equipped with semiconductor devices. Alternatively, the voltage may also be first rectified and supplied to a HVDC-link and be later converted into HF. This HF alternating voltage is then applied to the HFT's primary side so the system can bring the voltage to the desired level. The induced voltage on the HFT's secondary side is then rectified to supply a DC-link. At this point, the DC-link power can either supply DC loads or integrate DC-DES (*e.g.*, photovoltaics) or connect with an AC-link through another converter for load or generation purposes. For DES integration bidirectional power flow must be enabled. A basic structure of the SST is represented in Fig.1.1.

Figure 1.1: Basic Structure of the SST based on [36].

Considering possible applications on which the SST can link DC and AC systems running at medium and low voltage levels, several combinations are possible. For instance, the device can be

used to link Medium-Voltage (MV) and MV, MV and Low-Voltage (LV), or LV and LV, DC and/or AC systems. It is noteworthy that AC systems can be multi-phase, which increases the complexity of the design [13].

#### **1.2.2** Overview of SST architectures

Selecting the appropriate topology is crucial when it comes to SST implementation. To tackle this issue, engineers should consider the application's needs to minimize cost, maximize efficiency, and make the system more flexible to future changes. Such topologies can be classified according to the number of conversion stages to be installed: Single-stage, Two-stage with LVDC or MVDC-link, and Three-stage. Their basic scheme is represented in Fig.1.2.

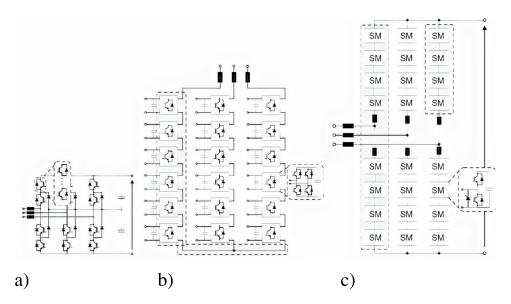

Figure 1.2: SST configurations: a) Single-stage, b) Two-stage with MVDC-link, c) Two-stage with LVDC-link, d) Three-stage. Image taken from [33]

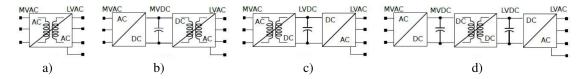

If HV functioning is considered (*e.g.*, power distribution), the device switches would not be compatible due to the high blocking voltage applied, exceeding their nominal rating. Also, high power applications test the boundaries of the components. The solution consists of a modular multilevel configuration to share the electrical quantities between the modules. These can either be based on Input Series Output Parallel (ISOP), Input Parallel Output Parallel (IPOP), or Input Series Output Series (ISOS). These are illustrated in Fig.1.3. Regarding the conversion stages, it is worth noting that these SST configurations still fall into the four categories mentioned above.

Figure 1.3: SST modular-multilevel configurations in HV and high-power systems: a) ISOP, b) ISOS, c) ISOS. Image taken from [36].

Each topology will be briefly reviewed in the following sections, including their base configurations, applications, advantages and disadvantages.

#### **1.2.3** Single-Stage Topology

Single-stage is the simplest SST topology. It comprises one power conversion through an HFT, which connects the MV to LV, allowing for bidirectional power flow and providing galvanic

isolation to the system. The single conversion device can operate in direct DC-DC or AC-AC conversion. A basic schematic of this topology is represented in Fig.1.2 a).

Due to fewer switching devices, which result in lower conduction and switching losses and a considerably cheaper cost [26], this topology has higher efficiency and reliability than the Three-stage topology [18]. The control system uses the shift angle to control the direction and magnitude of the power flow. Moreover, in bidirectional power flow, four-quadrant switches are necessary, which improve control strategy and Total Harmonic Distortion (THD) [18].

Regarding AC-AC converters, such as the full-bridge converter, these are characterized by high switching frequency which allows for a smaller sized HFTs. Additionally, there is no need for an electrolyte capacitor, making this setup more suitable for critical size applications. Soft switching is also achieved only for limited bandwidth around the rated load, making this application more suitable for constant load situations [2].

Due to the lack of a DC-link, AC-AC converters are unable to connect with the DC grid, DC transmission and DC local storage. As a result, the integration of RES is limited in this topology. Furthermore, without a DC bus, some auxiliary services like as reactive power regulation and disturbance blocking (*e.g.*, voltage sag and harmonics) are lost. [26][14].

Furthermore, the majority of SSTs are built for MV operation (*e.g.*, 7.2 kV AC). In a Singlestage structure, however, this causes voltage stress on switches. This requires modular multilevel designs, such as the ones described in the previous subsection, in which the voltage and power are shared in series. Nonetheless, because power and voltage must be balanced throughout the setup, this solution demands complex control. Two-stage and Three-stage topologies are required to overcome such problems [18].

#### 1.2.4 Two-Stage Topology

A DC-link is introduced on either the MV or LV side of the Two-stage topology, which distinguishes it from the Single-stage architecture. Although this setup allows for bidirectional power flow, it may simply be switched to unidirectional by using an unregulated rectifier on the AC-DC converter's LV side [18]. A fairly complex switching approach and a large number of switching devices usually come with a double staged topology. Nonetheless, such complexity results in additional useful auxiliary services like reactive power compensation [14].

#### 1.2.4.1 Two-Stage Topology with LVDC-link

As its name suggests, the Two-stage topology with an LVDC-link comprises of two conversion stages. First, the supply AC voltage is converted to a higher frequency so that the HFT can regulate the power to the desired voltage. Then, the output voltage from the LVAC side of the HFT gets rectified and supplies the LVDC bus. This constitutes the first conversion stage. In the second stage, the DC voltage in the DC-Link is inverted by the DC-AC converter [14]. A basic schematic of this topology is represented in Fig.1.2 c). This architecture provides reactive power compensation, good output voltage and input-current regulation [14]. Moreover, due to the presence of a DC-Link at the LV side, this topology allows for the interaction with DES, RES (*e.g.*, photovoltaic and wind plants), ESS and DC loads capable of bidirectional power flow [14] [18].

Like the Single-stage topology, this Two-stage architecture is not suitable for HV operation, considering that it is hard to achieve the necessary Zero Voltage Switching (ZVS) in the inversion process in such an extensive input range. Furthermore, well-established multilevel topologies cannot be easily applied to the HV side. Thus, high switching losses may not be avoided without sacrificing frequency, leading to lower efficiency and difficult thermal management [36]. However, removing the LVDC-link is counter-productive as it would translate into poor RES integration, as discussed in the Single-stage section. The HVDC from end-applications may present HV issues. These can be addressed by converting the current to LVDC, instead of LVAC, and connecting it directly to the DC-link [18]. Furthermore, high complex control systems are necessary to control the bidirectional flow, and a high ripple current in the DC-link is usually present [14].

#### 1.2.4.2 Two-Stage Topology with MVDC-link

This topology shares most of the previously mentioned architecture benefits, as it also contains a Two-stage conversion system and a DC-Link. However, the DC-Link is now on the MV side. Thus, galvanic isolation and voltage step-down are preformed at the DC-AC conversion stage. Therefore, the LVDC link is no longer available [36]. A basic schematic of this topology is represented in Fig.1.2 b). Such configuration is not so suitable for integration of the DES, RES and ESS. Instead, thanks to the MVDC link, it is suitable for applications in the distribution grid, such as in the integration of MVDC grid transmission lines [14].

#### 1.2.5 Three-Stage Topology

Due to its several ancillary services and features, this topology is the most popular amongst SST architectures. Not only does it have a significantly lower weight and size than the traditional LFT, but it can also optimize its performance in distribution and transmission grids [18]. In similarity to the two topologies previously mentioned, the Three-stage design also allows for bidirectional power flow. This architecture incorporates an AC-DC conversion stage, a DC-DC conversion stage with an HFT, which provides galvanic isolation, and a DC-AC conversion stage [26].

Two DC links are connected to each side of the DC-DC conversion stage. These decouple the MV side from the LV side, avoiding propagating disturbances from the grid to the end-application or vice versa. A basic schematic of this topology is represented in Fig.1.2 d). Moreover, this design can address power PQ issues, such as reactive power compensation and voltage sag compensation. It also allows for voltage regulation, current limiting, and load protection. The DC-Link in the MV side makes the application suitable for integration in distribution and transmission grids. On the other hand, the DC-Link in the LV side allows for integrating DES, RES and ESS applications.

Thus, this topology is considered the most versatile [36] [14] [18]. However, due to the higher number of switching devices, it has a higher cost and lower efficiency [18].

#### 1.2.6 SST Topology Comparison

Given the three architectures' essential descriptions, they may be compared by evaluating the available functionalities, limitations, and feasible applications of each one.

The Single-Stage topology allows bidirectional power flow, but its application on RES and DES is minimal due to the lack of a DC-link. This also translates into a lack of functionalities, such as reactive power compensation. Nevertheless, its low number of switching devices allows for size reduction and provides high efficiency and reliability.

The Two-Stage topology describes an intermediate topology between the Single-Stage and the Three-Stage ones. The additional DC-link placed at MV or LV allows for many functionalities, such as the reactive power compensation, limitation of disturbances propagation, etc. The control scheme becomes more complex than in Single-stage SST since the stages operate at different frequencies.

Lastly, Three-Stage topology is the most versatile in terms of applicability and functionality. However, the higher number of switching devices directly translates into lower efficiency due to switching losses and lower system reliability. Despite its higher cost, this topology has broader applicability, making it most suitable for DES and RES integration. Table 1.1 presents a summary of the three architectures' functionalities and applications.

| Capability                          | Single-Stage | Two-Stage | Three-Stage |

|-------------------------------------|--------------|-----------|-------------|

| Bidirectional power flow            | Yes          | Yes       | Yes         |

| Reactive power compensation         | No           | Yes       | Yes         |

| Independent power factor            | No           | Yes       | Yes         |

| Independent frequency               | No           | Yes       | Yes         |

| Input current limiting              | No           | Yes       | Yes         |

| Output current limiting             | No           | Yes       | Yes         |

| Input current regulation            | No           | Good      | Very Good   |

| Output voltage regulation           | Poor         | Good      | Good        |

| Harmonic and voltage sag limitation | No           | Good      | Very Good   |

| Modularity implementation           | Simple       | Hard      | Simple      |

| DES applications (such as RES)      | Not suitable | Suitable  | Suitable    |

| Grid applications                   | Suitable     | Suitable  | Suitable    |

Table 1.1: SSTs' topologies capabilities comparison [18] [23] [14] [34].

#### 1.2.7 Overview of the Connection Stages

#### 1.2.7.1 MVAC - MVDC connection stage

This stage connects the MVAC side (usually grid line, 50/60 Hz) with the MVDC link through the active rectifying process, which allows for bidirectional power flow. Also known as the medium voltage stage, this stage enables the SST to filter out reactive power in the MV grid, using only active power and feeding it on to the next stage.

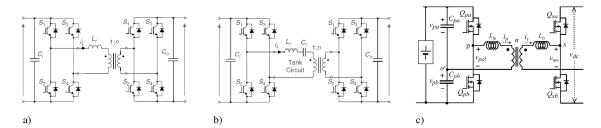

Multilevel converters stand out as a solution for this phase due to their high power ratings, lower Common-Mode Voltage (CMV), reduced harmonic content, near sinusoidal currents, small input and output filters (if necessary), increased efficiency and possible fault operation [31]. Regarding existing multilevel converter topologies, Table 1.2 provides a comparative overview of the most relevant for SST applications. Furthermore, their circuit schematics are presented in Fig.1.4.

| C DC Convertor | Advantages                       | Disadvantagas                       | Annlighti |

|----------------|----------------------------------|-------------------------------------|-----------|

| Table 1.2      | : Comparison between the differe | ent AC-DC converters [18] [14] [23] | [31].     |

| AC-DC Converter                          | Advantages                                                                                                                              | Disadvantages                                                                                                                                                                       | Application       |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Neutral-Point<br>Clamped<br>(NPC)        | <ul> <li>Simple control;</li> <li>Presence of a DC-link;</li> <li>High power density;</li> <li>Lower cost.</li> </ul>                   | <ul> <li>Larger AC filter;</li> <li>Lower PQ;</li> <li>Higher switching voltage;</li> <li>Energy inefficiency;</li> <li>Voltage unbalance issues for more than 3 levels.</li> </ul> | Medium<br>Voltage |

| Cascaded<br>Half-Bridge<br>(CHB)         | <ul> <li>Simple control;</li> <li>Low-frequency operation for each cell;</li> <li>Good control functionality at medium cost.</li> </ul> | <ul> <li>Need for isolated supply for each cell;</li> <li>Absence of a DC-link.</li> </ul>                                                                                          | Medium<br>Voltage |

| Modular Multilevel<br>Converter<br>(MMC) | <ul><li>Lower frequency operation;</li><li>Presence of a DC-link.</li></ul>                                                             | <ul><li>Complex control;</li><li>Bulky Capacitors;</li><li>High cost due to more devices and capacitors.</li></ul>                                                                  | High<br>Voltage   |

Figure 1.4: Circuit schemactic of AC-DC converters: a) NPC; b) CHB; c) MMC. Taken from [23].

#### 1.2.7.2 MVDC-LVDC connection stage

This stage is at the core of the SST design. It is composed of a high-frequency converter which serves as the power flow control between the MV and LV grids. The HFT is also part of this stage, bringing the converter's input voltage to the desired level through HF AC power [18] [14] [23]. This conversion stage is composed of there parts: a DC-AC converter, an HFT, and AC-DC converter;

This conversion stage is also the most challenging for SST design since the application's high-power requirements translate into high-current on the LV side and HV on the MV side. Two approaches to meet these high-power requirements have been investigated. The most straightforward solution is to use standard HV-rating devices. However, one can opt for a modular concept. This solution consists of cascading several LV device modules to share the total voltage and power. Additionally, it presents a high number of switching devices resulting in lower reliability. However, it also has several advantages: low electromagnetic interference, streamlined fault tolerance strategy and the usage of standardized LV rating devices, which are easily available and simplify modular implementation [23] [18]. Regarding existing topologies, Table 1.3 provides a comparative overview of the most relevant for SST applications. Furthermore, their circuit schematics are presented in Fig.1.5.

| DC-DC Converter                                       | Advantages                                                                                                                                                                                                                                       | Disadvantages                                                                                                                                           | Efficiency |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Dual-Active<br>Bridge<br>(DAB)                        | <ul><li>Simple control;</li><li>Controllable power flow;</li><li>Less reactive power flow.</li></ul>                                                                                                                                             | <ul> <li>Less efficient due</li> <li>to higher number of switches;</li> <li>Higher leakage inductance;</li> <li>Less transformer saturation.</li> </ul> | 92.5%      |

| DAB with<br>Series Ressonant<br>Converter<br>(SRC)    | <ul> <li>Well regulated output voltage;</li> <li>for a wide range of loads;</li> <li>Reliable;</li> <li>Higher switching frequency;</li> <li>No issues in inductance leakage;</li> <li>Protected against transformer over-saturation.</li> </ul> | <ul> <li>Incapable of regulating output power;</li> <li>Complex control;</li> <li>High resonant capacitor.</li> </ul>                                   | 98.61 %    |

| Dual-Half<br>Bridge<br>(DHB)                          | <ul> <li>Less number of switching devices;</li> <li>Higher reliability;</li> <li>Lower cost.</li> </ul>                                                                                                                                          | <ul><li>More reactive power;</li><li>Blocking voltage limitation;</li><li>High current through transformer windings.</li></ul>                          | 96%        |

| Asynchronous<br>Quadruple<br>-Active Bridge<br>(AQAB) | <ul><li>Less number of switching devices;</li><li>Higher reliability;</li><li>Controllable power flow.</li></ul>                                                                                                                                 | - High-power rating devices are necessary.                                                                                                              | 97.5%      |

Table 1.3: Comparison between the different DC-DC converters [18] [31] [23] [26] [38].

Some other topologies also are worth mentioning, such as the three-phase DAB and the multiple-active-bridge (MAB) converter. The three-phase topology may be adopted due to lower device stress, more efficient transformer usage and lower filter requirements [26]. The MAB converter has the same features as the three-phase DAB converter, but it reduces the number of HF transformers by linking more active bridges into a single transformer [23].

The modularity flexibility at this stage is key for the application's versatility. Multiple DC-

Figure 1.5: Circuit schemactic of DC-DC converters: a) Dual-Active Bridge (DAB) [23]; b) DAB with SRC [23]; c) DHB [21].

DC converters can be used to create more complex structures, as the application's necessities vary. Moreover, a parallel connection can be used on the MV side and a series connection in the LV side to reduce the LV side's voltage ripple. This is mandatory for single-input and single-output topologies such as the DAB, DHB and SRC-DAB converters. MAB converters introduce a higher degree of flexibility [23].

#### 1.2.7.3 LVDC-LVAC connection stage

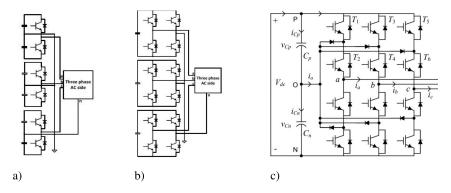

It is responsible for converting DC to AC. The power can be transferred from or to the DC-DC stage converter. The output terminal from the DC stage is often connected to AC loads, but it can also integrate DES. The voltage level can vary according to the application. Multilevel topologies can be adopted depending on the application. If HV is involved, modules should be cascaded to share the total voltage so the switching devices can withstand the HV rating. If the applications integrate AC loads, four-leg (three-phase plus the neutral conductor) topologies should be adopted. This stage plays an essential role in the SST's application as it is responsible for shaping the DC voltage into a sinusoidal AC waveform with the desired amplitude and frequency. The inversion process is not affected by any possible disturbances (*e.g.*, overvoltage or voltage sag) and other systems connected to the supply grid [18], since the HFT provides galvanic isolation. Moreover, if the AC output waveform needs to be improved more modules can be installed. The modularity approach is always an advantage as it presents a flexible solution for future variations in the application's power. Regarding existing topologies, Table 1.4 provides a comparative overview of the most relevant ones for SST applications. Furthermore, their circuit schematics are presented in Fig.1.6.

| DC-AC Converter | Advantages                               | Disadvantages                      |  |

|-----------------|------------------------------------------|------------------------------------|--|

| Half-Bridge     | - Most simple of all topologies;         |                                    |  |

| (HB)            | - Less number of switches;               | Voltage unbalance issues.          |  |

| (пв)            | - Higher Reliability.                    |                                    |  |

| Full-Bridge     | - Lower DC-link voltage.                 | Voltage unbalance issues.          |  |

| (H-bridge)      | - Lower DC-link voltage.                 |                                    |  |

| Neutral-Point   | - Enables the use of 600V power devices; |                                    |  |

| Clamped         | - Increased system's efficiency;         | Neutral-point voltage unbalancing. |  |

| (NPC)           | - Reduced voltage sag and THD.           |                                    |  |

Table 1.4: Comparison between the different DC-AC converters [18] [31] [23] [26] [37] [14].

Figure 1.6: Circuit schemactic of DC-AC converters: a) HB [31]; b) H-Bridge [31]; c) NPC [19].

Three-level topologies are the most feasible options with regards to applicability [23]. Thus, the HB and H-Bridge inverters may be connected in parallel to form multi-phase converters, including three-phase systems as represented in Fig.1.6. However, in some architectures, such as the HB and FB, this implies more DC-links, which directly influences the remaining stages in the application.

#### 1.2.8 High-frequency transformer

The HFT is at the core of the SST, replacing the traditional 50/60 Hz transformer and decreasing overall weight and volume. Moreover, it provides galvanic isolation to the SST's end application. The principle behind the functioning of the HFT is the same as in the traditional transformer, as expressed by Faraday's induction law 1.1. However, as the magnetic field's frequency crossing the transformer's windings is much higher than in a traditional LFT, the number of necessary windings to achieve the same voltage level transformation is much lower [18]. The basic HFT operation is shown in Fig.1.1.

$$\varepsilon = -N \cdot \frac{\Delta\phi}{\Delta t} \tag{1.1}$$

The higher-frequency operation makes the design of the HFT much more complex than the traditional LFT. Several design measures should be taken into account for this HV, high-power, and HF functioning.

During the HFT manufacturing process, **material selection for the core** is based on loss reduction (Foucault currents and Hysteresis phenomenon), saturated magnetic flux maximization (usually translating to higher power density), Curie and maximum operating temperatures, and magnetic permeability maximization [14] [18] [27]. Nanocrystalline proves to be the best material choice due to its high saturation flux density and lowest power losses. [18]. However, its high cost and limited design customization should be considered [36].

**Winding configuration** should also be carefully studied. Mutual inductances and windings' coupling coefficients are directly influenced by winding placement, affecting power loss and system efficiency. A popular SST application is core-type solenoidal structures for their low cost, and

easy manufacturing process [18].

Wire material selection is also a crucial consideration. Two key challenges arise due to HF functioning: the skin effect and the proximity effect [12]. Such effects can not be ignored, as they largely affect the system's performance. A Litz wire is implemented to suppress them, as it contains hundreds of smaller and properly isolated conductive strands (down to 0.005 mm<sup>2</sup> cross-section area) [18]. Taking voltage power calculations into account, the strands can be agglomerated into a thicker wire with the desired overall cross-section. Each strand's cross-section is quite small compared to penetration depth, making the AC flow roughly homogeneous across them and thus, the total cross-section, directly suppressing the skin effect. Moreover, to minimize the proximity effect, the wire is then twisted and woven [14].

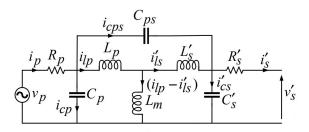

Although the above-mentioned methods aim to minimize parasitic phenomena, some cannot be ignored when mathematically modeling the HFT. For a core-type HFT with unity-turns ratio, a model was developed considering the parasitic quantities, presented in Fig.1.7.

Figure 1.7: HFT equivalent circuit schematic referred to primary. Taken from [22]

Regarding the circuit,  $v_p$  represents the primary excitation voltage, and  $v'_s$  the secondary voltage.  $L_p$ ,  $L'_s$  and  $L_m$  represent the primary and secondary windings, respectively, and mutual leakage inductances. These represent the imperfect magnetic linking between windings.  $C_p$  and  $C'_s$  represent the stray capacitances across each winding. Cps represents the stray capacitance between windings. All three capacitances arise from the electric potential differences between nearby surfaces, close enough to generate an electric field.

Moreover, other design elements can be considered for space-limited applications, such as **HV isolation between primary and secondary windings and thermal management**. Regarding isolation, a dry-type transformer design is only suitable to a certain extent. If necessary, insulating materials should be considered, such as epoxy or highly insulating wire [36]. In such applications, oil-free functioning is expected. Consequently, thermal management becomes a challenge in the SST design. If feasible, natural convection is the simpler and preferred solution. However, other more powerful approaches may be necessary, such as fan-cooled and water-cooled heat sinks [36].

#### **1.2.9 SST Applications**

Regarding functionality, the SST is well suited to replace the traditional LFT and other power electronic converters within the distribution system, allowing for a more compact and integrated

system. The SST's efficiency and cost discrepancy is justified by its several additional features and ancillary services. This increased versatility translates into broader applicability. Most of new SST applications exploit its advantages regarding better controllability, smaller necessary working space and integration capability in both AC and DC systems. The main SST applications are summarised in the following categories:

- Smart Grid: As mentioned in the introduction section, RES gain increased interest in the context of environmental concerns and the search for a more sustainable electrical power system. As some of the RESs are generated in DC power (*e.g.*, solar photovoltaic panels), bulky converters and inverters would be necessary to achieve grid connection if a traditional LFT was used. The SST is a viable solution to this inconvinience, as it allows for DC integration and for the necessary power conversions. More importantly, it is worth noting that RES are not continuously generating energy. Moreover, conventional RES systems would disconnect during overvoltages periods, decreasing profitability for exploring enterprises. Once more, the SST offers a solution to this challenge, as it can control the output power and provide disturbance shielding [18]. The SST has also shown to be suited in wind-powered generation systems, since these systems usually require extra circuitry for reactive power compensation, besides the already necessary voltage transformation devices for grid connection. Therefore, the STT provides a variety of smarter, more efficient and more compact solutions to a range of challenges present in LFT applications [36]. Moreover, the SST's LVDC-link could allow the integration of other types of DES and ESS.

- **Power Quality**: As presented in earlier sections, the SST may provide reactive power compensation depending on the adopted topology. Furthermore, it can also provide harmonic current filtering depending on the adopted switching frequency. Finally, the SST enables fault isolation and limitation if equiped with the respective control functions, as opposed to the passive LFT.

- Traction System: Traction systems are indeed one of the major SST's applications. The current systems use bulky LFTs, for instance, a 6 MVA LFT has a weight to power ratio of 1.7 kg/kVA (depending on the frequency), making its average weight around 10 Tones [18]. Thus, in such critical-sized applications, researchers are pushing for SST systems, providing size and weight reduction without compromising efficiency.

#### **1.3 Dissertation Objectives and Structure**

The goal of this dissertation is to develop, design, and simulate a Two-stage SST for connecting a battery storage system to the AC grid. The system must provide bidirectional power flow as well as meet minimal PQ standards (*e.g.*, input current harmonic distortion, voltage stability).

The introduction chapter starts by exposing the context & motivation behind the study of SST technologies which will be a crucial part of the electrical sector as it transits to a more sustainable and green reality. Following that, a brief state-of-the-art of SST technology is offered including its

various topologies based on the number of conversion steps used. There is also a breakdown of the connecting stages and the many sorts of converters utilized in each. The HFT, which is at the heart of the SST, is also briefly discussed, as are its primary design and modelling features. Finally, the most trending SST applications are discussed.

In chapter 2, the system is explained in detail. The configurations of the converters employed in each connection stage are discussed, as well as their primary design challenges and requirements.

In chapter 3, the modelling of the system is developed. A mathematical model is presented for the various converters employed in each stage.

In chapter 4, the control techniques employed in each converter are described in full detail.

In chapter 5, a simulation of the proposed system is presented, followed by a discussion of its respective results.

Finally, in chapter 6, a perspective on the already accomplished work is provided, as well as a proposal for future work.

### **Chapter 2**

## **Proposed System**

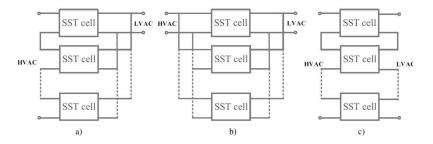

To integrate a Battery Storage System (BSS) into the HVAC electrical grid, the proposed system is a two-stage conversion SST. To further understand the system, a simplified block diagram is shown in Fig.2.1.

Figure 2.1: Proposed system to integrate the BSS to the HVAC electrical grid.

Due to the lack of a neutral connection in HV systems, the initial conversion step connects a three-phase system made up of three wires. The initial stage of conversion must meet minimal PQ standards, satisfy grid requirements and allow bidirectional power flow. When the BSS is in charging mode, electricity is rectified from the AC grid to the DC-Link-1 (HVDC), and when the BSS is delivering power, power is inverted from the DC-Link-1 to the HVAC grid.

The second conversion stage connects the DC-Link-1 (HVDC) to the DC-Link-2 (LVDC). As a result, it is made up of  $N_{DAB}$  converters connected in an ISOP, thus the converters share the DC-Link-1 voltage in series, and the DC-Link-2 current in parallel. To provide bidirectionality, converters must be able to manage power flow from or to each DC-Link. Each converter requires an HFT with a transformation ratio near to unity to provide galvanic isolation between the electrical grid and the BBS.

The BSS has a lower operating voltage and several operation modes, which means it can work with varying working voltages and currents. As a result, in order to discharge and charge the battery pack properly, the BSS requires the inclusion of a DC-DC converter.

The sections that follow provide justifications for the topologies employed in each stage, as well as a brief overview of their underlying configuration.

# 2.1 First Conversion Stage

The Modular Multilevel Converter (MMC) is an attractive topology for several applications in the energy field. The converter's base architecture characteristic is a cascade connection of Submodule (SM), which gives it modularity, scalability, and flexibility. Such features were critical in selecting this type of converter for the first conversion stage, since the modular topology allows the converter to operate over a wide voltage and power range, making it appropriate for the HVAC-HVDC conversion stage [11].

The converter does not require separate DC sources, hence no special transformer is required. Since each module has its own capacitor, the modular architecture reduces the requirement for HV capacitors, greatly reducing the cost of the application. Regarding PQ, the converter is able to generate line-to-line voltages and grid currents with low harmonic content. Depending on the chosen control strategy, it may offer low filter requirements in function of the converter's switching frequency [4].

The number of SMs in an MMC varies depending on the application, operating voltage and semiconductor device rating. 5 SMs/arm are required for a 3.3 kV operational voltage motor drive. HVDC applications, on the other hand, can require up to 400 SMs/arm to handle voltages up to 400 kV. The MMC can produce a DC-Link-1 voltage waveform with a very high number of voltage levels as the number of SMs rises. As a result, the SMs can be operated at a lower frequency reducing the converter's losses. Furthermore, depending on the number of SMs employed, it can use redundant SM in each arm to ensure fault tolerance [6].

The next section makes a brief review of the MMC's configuration along with its functionality.

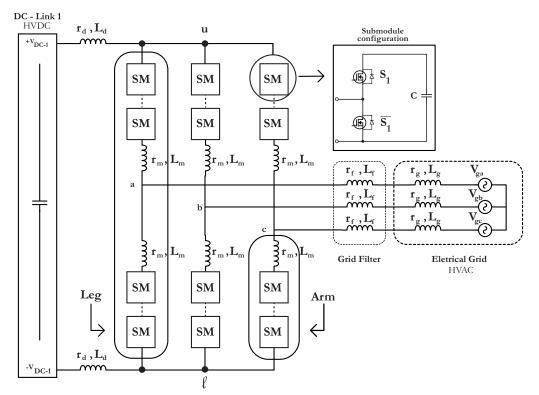

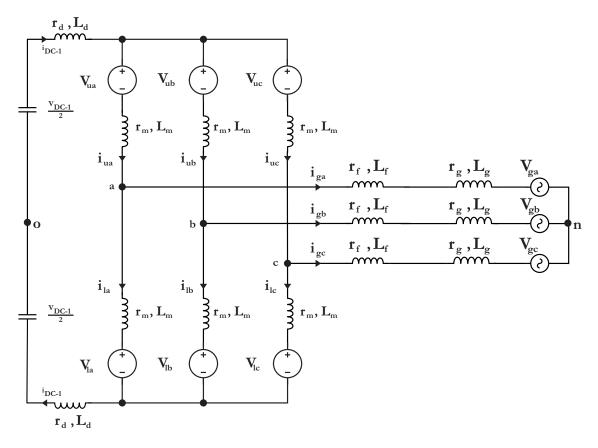

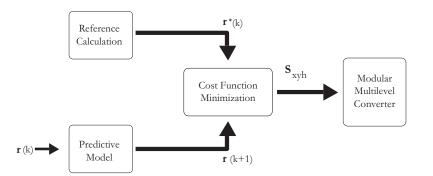

## 2.1.1 MMC Configuration

The MMC is a three-phase AC-DC converter and its configuration is represented in Fig.2.2. It consists of three legs, and each leg is divided into two arms: upper (u) and lower (l). Each arm is comprised of a series connection of SMs with an inductor  $(L_m)$ . This component, " $L_m$ ", can also be referred to as an arm inductor, and its power losses are represented with a resistance of " $r_m$ ". This inductor is placed mainly to limit the magnitude of Circulating Current (CC) flowing through the arms due to the instantaneous voltage difference between the arms [11].

All converters legs have their positive and negative bus terminals connected to a common DC system. Such a system is represented by an ideal split DC source of voltage rated  $\frac{V_{DC-1}}{2}$ . The DC cable is represented with an inductor " $L_d$ " and an equivalent resistance " $R_d$ ". The midpoint of each converter leg is an AC output terminal (a, b, c). Each terminal is connected to a grid filter,

represented by " $L_f$ " and " $R_f$ ", its necessity and functionality are discussed in subsection 2.1.3. The filter then connects to the grid, represented by an AC voltage source rated  $V_g$  in all three phases. The grid source is configured in the star connection, and their common point is referred to as "n". However, since the converter is connected to HVAC grid, this point is inaccessible and is merely representative for the discrete-time modelling of the converter, which is explored in detail in chapter 3.

Figure 2.2: MMC & SM configuration.

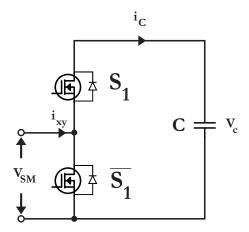

## 2.1.2 Configuration of SMs

Over the last few years, various SM configurations have been produced. However, due to its low number of components, easy control and high efficiency, the Half-Bridge Submodule (HB-SM) has proven extremely popular in various applications [6]. The HB-SM, also known as chopper cell, consists of two MOSFETS ( $S_1$  and  $\overline{S_1}$ ) with an anti-parallel diode and a floating capacitor (C), as shown in Fig.2.2. The two MOSFETS are operated in a complementary manner, thus an independent gating signal is sufficient to control the HB-SM. The discrete-time modelling of the HB-SM is also necessary for the chosen control strategy and is explored in subsection 3.1.2.

#### 2.1.3 Grid Filter

To connect to the HVAC grid, the SST application requires a filter. This filter primarily serves three purposes. The first is to allow active and reactive power control between the SST. The second function is to diminish the SST's harmonic distortion in order to maintain PQ, as the converter's line-to-line voltages are not sinusoidal like the AC grid voltages [4]. The filter's final duty is to

serve as a charging element, allowing the converter to convert HVAC power to HVDC since the HVDC-link rated voltage is higher than the HVAC peak voltage.

The L-filter, LC-filter, and LCL-filter are the three basic filters that can be used to connect the SST to the electrical grid [3]. Taking into consideration the MMC's architecture, the switching frequency increases as the number of SMs grows, allowing for more sinusoidal waveforms. As a result of these two qualities, harmonic distortion is minimized and filters are smaller. The high switching frequency guarantees proper filtering and allows for compact filters, resulting in a minimal voltage drop across the filter inductor [4]. Consequently, a simple L-filter can be used to link the converter to the HVAC grid, ensuring attenuation of -20dB/decade across the whole frequency range [3]. Furthermore, because HV capacitors are expensive, a filter with a capacitor should be avoided whenever possible to reduce costs.

# 2.2 Second Conversion Stage

Because the proposed system is a HV application, the stage connecting the battery pack to the HVDC-link must comprise a set of DC-DC converters capable of bidirectional power flow, coupled in an ISOP philosophy, as previously described. Since the converters are connected in series, the HV from the DC-Link-1 can be shared between the converters, and the resultant larger currents on the DC-Link-2 side can be shared via a parallel connection.

Different topologies exist for DC-DC converters; nevertheless, galvanic isolation is a condition that excludes all non-isolated topologies. Furthermore, resonant topologies were omitted since they require an additional capacitor, resulting in a bigger, heavier, and more expensive solution [15]. As a result, the DAB converter and its half-bridge variant are the only options. Even while the latter option uses fewer switches, it necessitates the use of split capacitors, which inevitably increases the size and cost of the application [5]. The following section will present a brief review of the DAB converter configuration.

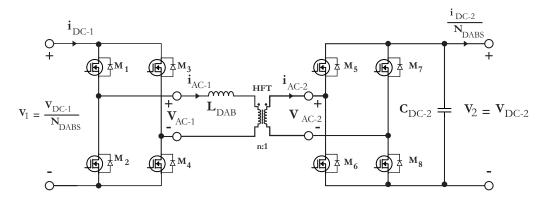

#### 2.2.1 Dual-Active Bridge

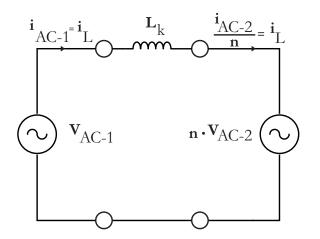

The DAB is a bidirectional, controllable DC-DC converter with high power capabilities. It comprises eight semiconductor devices, an HFT, an energy transfer inductor,  $L_{DAB}$ , and DC-link capacitors. This converter can be more commonly described as a full bridge with a controllable rectifier. Due to its symmetry, with identical primary and secondary bridges, it is capable of bidirectional power flow control [16].

The topology is shown in Fig.2.3, with  $V_1$  and  $V_2$  denoting the DC-link voltages,  $L_k$  denoting the transformer's leakage inductance plus a required external energy transfer inductor,  $L_{DAB}$ , and  $M_{1-8}$  denoting the controllable semiconductor switches. IGBTs or MOSFETS could be used in these devices. However, because the latter design incorporates an intrinsic body diode and drain-to-source capacitance, it eliminates the need for additional anti-parallel diodes and snubber capacitors to direct current commutation during switching events and enable ZVS. SiC is a wide bandgap material with greater voltage, thermal, and turn-on energy ratings, making it ideal for high-frequency switching converter applications [15].

Figure 2.3: Dual active bridge topology.

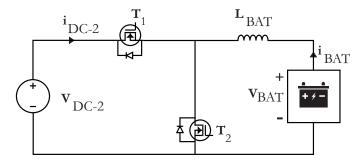

# 2.3 Battery Storage System