## UNIVERSIDADE D COIMBRA

### João Carlos da Costa Barreiros

# FAST SCALE-INVARIANT FEATURE TRANSFORM ON GPU

Mestrado Integrado em Engenharia Eletrotécnica e de Computadores, ramo de especialização em Computadores orientada pelo Professor Doutor Gabriel Falcão Paiva Fernandes e apresentada à Faculdade de Ciências e Tecnologia da Universidade de Coimbra no Departamento de Engenharia Eletrotécnica e de Computadores

Outubro de 2020

#### **Fast Scale-Invariant Feature Transform on GPU**

João Carlos da Costa Barreiros

## Dissertação para obtenção do Grau de Mestre em **Engenharia Electrotécnica e de Computadores**

Orientador: Doutor Gabriel Falcão Paiva Fernandes

#### Júri

Presidente: Doutor João Pedro de Almeida BarretoOrientador: Doutor Gabriel Falcão Paiva FernandesVogal: Doutor Jorge Nuno de Almeida e Sousa Almada Lobo

#### Outubro de 2020

We can only see a short distance ahead, but we can see plenty there that needs to be done

- Alan Turing

## Agradecimentos

Gostaria em primeiro lugar de agradecer ao professor Gabriel Falcão Paiva Fernandes pela sua orientação, dedicação, disponibilidade e paciência que teve para comigo durante o percurso desta dissertação. Destaco que o seu apoio contínuo foi fulcral para a conclusão da mesma.

Em segundo lugar gostaria de agradecer ao Instituto de Telecomunicações por disponibilizar todos os meios de trabalho necessários e também um ambiente amigavel e profissional.

Aos meus pais, por toda a ajuda prestada durante o meu percurso académico, sinto uma eterna gratidão. Agradeço todos os esforços que fizeram por mim para eu me tornar na pessoa que sou hoje.

Por fim, quero referir todos os meus colegas e amigos que me acompanharam também durante este percurso: Filipe, Óscar, Louro, Fraga, Martins, Costa, Veiga, Cavaleiro, Matos, Abegão, Janela, Bernardo e todos aqueles que conviveram comigo no dia-a-dia.

> A todos, Muito Obrigado

## Abstract

Feature extraction of high-resolution images is a challenging procedure in both high and low-power signal processing applications. This thesis describes how to optimize and efficiently parallelize the scale-invariant feature transform (SIFT) feature detection algorithm and maximize the use of bandwidth on the GPU subsystem. Together with the minimization of data communications between host and device, the successful parallelization of all the main kernels used in SIFT allowed a global speedup in high-resolution images above 78x while being more than an order of magnitude energy efficient (FPS/W) than its serial counterpart. From the 3 GPUs tested, the low-power GPU has shown superior energy efficiency in almost every case. Achieving up to 6x less power consumption than the CPU for the same amount of work.

## **Keywords**

Feature extraction, Scale-invariant feature transform (SIFT), GPGPU, CUDA, Parallel Programming.

## Resumo

A extração de caracteristicas de imagens de alta resolução é um procedimento bastante desafiante tanto em aplicações de processamento de sinais de alta como de baixa potência. Esta dissertação descreve como otimizar e paralelizar de forma eficiente o algoritmo scale-invariant feature transform (SIFT) e maximizar o uso da largura de banda na GPU. Juntamente com a minimização das comunicações de dados entre o host e o device, a paralelização bem-sucedida de todos os kernels principais usados no SIFT permitiu um aumento de velocidade global de 78x em imagens de alta resolução. Ao mesmo tempo, a solução apresentada consegiu uma maior ordem de grandeza de eficiência energética (FPS/W) do que a sua contraparte sequencial. Das 3 GPUs testadas, a GPU de baixo consumo mostrou maior eficiência energética em quase todos os casos. Alcançando até 6x menos consumo de energia do que a CPU para a mesma quantidade de trabalho.

## **Palavras Chave**

Feature extraction, Scale-invariant feature transform (SIFT), GPGPU, CUDA, Parallel Programming.

## Contents

| 1 | Intr | oductio   | 'n                                     | 1  |

|---|------|-----------|----------------------------------------|----|

|   | 1.1  | Motiva    | ation                                  | 2  |

|   | 1.2  | Object    | tives                                  | 3  |

|   | 1.3  | Disser    | tation Outline                         | 3  |

| 2 | Bac  | kgroun    | d on SIFT                              | 4  |

|   | 2.1  | The SI    | IFT Algorithm                          | 5  |

|   |      | 2.1.1     | Creation of the Scale-Space            | 5  |

|   |      | 2.1.2     | Extrema Detection                      | 6  |

|   |      | 2.1.3     | Orientation assignment                 | 8  |

|   |      | 2.1.4     | Keypoint Descriptor                    | 9  |

|   | 2.2  | Relate    | d Work                                 | 10 |

|   |      | 2.2.1     | High performance implementations       | 10 |

|   |      | 2.2.2     | Low-power implementations              | 11 |

| 3 | The  | GPU a     | rchitecture and CUDA programming model | 12 |

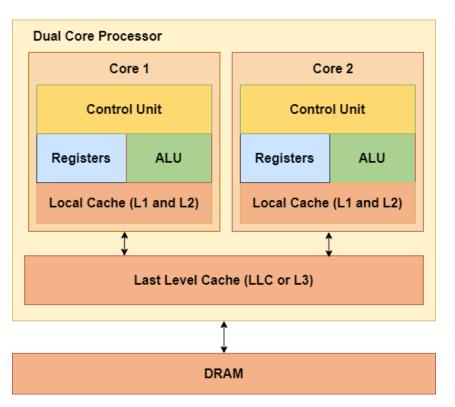

|   | 3.1  | CPU a     | architecture                           | 13 |

|   |      | 3.1.1     | Memory Hierarchy                       | 13 |

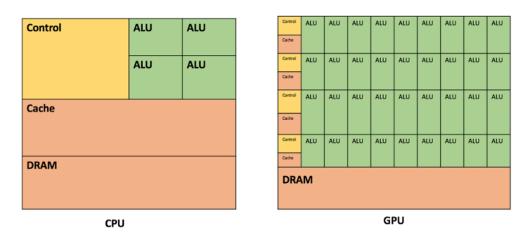

|   | 3.2  | GPU a     | architecture                           | 14 |

|   | 3.3  | CUDA      | A Programming Model                    | 15 |

|   |      | 3.3.1     | Memory Hierarchy                       | 16 |

|   |      | 3.3.2     | CUDA optimization techniques           | 18 |

| 4 | Para | allelizin | g SIFT on the GPU                      | 23 |

|   | 4.1  | The SI    | -<br>IFT Datablock                     | 24 |

|   | 4.2  | 2D Ga     | ussian Convolution                     | 24 |

|   |      | 4.2.1     | Separable convolution                  | 25 |

|   |     | 4.2.2    | Box Filters approximation                              | 26 |

|---|-----|----------|--------------------------------------------------------|----|

|   | 4.3 | Differe  | ence of Gaussians                                      | 27 |

|   | 4.4 | Extrem   | na Detection                                           | 29 |

|   | 4.5 | Orienta  | ation Histogram                                        | 30 |

|   | 4.6 | Feature  | e Descriptor                                           | 30 |

|   | 4.7 | Pinned   | memory optimizations                                   | 30 |

| 5 | Exp | eriment  | al Results                                             | 32 |

|   | 5.1 | System   | n Setup                                                | 33 |

|   |     | 5.1.1    | GPU Memory transfers                                   | 34 |

|   |     | 5.1.2    | CUDA shared memory                                     | 35 |

|   |     | 5.1.3    | Gaussian Convolution vs Box Filters                    | 36 |

|   | 5.2 | Scale-s  | space generation                                       | 37 |

|   | 5.3 | Differe  | ence of Gaussians                                      | 39 |

|   | 5.4 | Extrem   | na Detection                                           | 40 |

|   | 5.5 | Orienta  | ation Histogram                                        | 40 |

|   | 5.6 | Feature  | e Descriptor                                           | 41 |

|   | 5.7 | Global   | SIFT Behavior and Results                              | 41 |

|   |     | 5.7.1    | Performance analysis                                   | 42 |

|   |     | 5.7.2    | Energy Efficiency Analysis                             | 42 |

|   |     | 5.7.3    | Matching the robustness of the SIFT parallel algorithm | 44 |

| 6 | Con | clusions | 5                                                      | 52 |

|   | 6.1 | Future   | Work                                                   | 53 |

## **List of Figures**

| Difference of Gaussians, courtesy of [1]                                 | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Extrema detection, extracted from [1]                                    | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Descriptor generation, obtained from [1]                                 | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Example of image matching using SIFT                                     | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Example of image stitching using SIFT                                    | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Example of object detection using SIFT, adapted from [2]                 | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| An example of a modern dual core CPU architecture                        | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CPU vs GPU Architecture, adapted from [3]                                | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

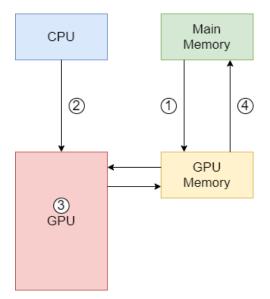

| Processing Flow in CUDA                                                  | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

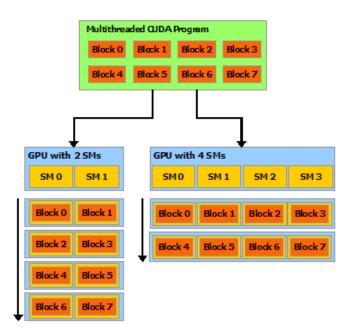

| Scalability in CUDA, obtained from [4]                                   | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

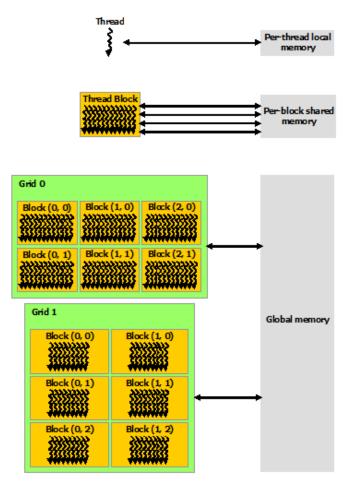

| GPU Memory Hierarchy, acquired from [4]                                  | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

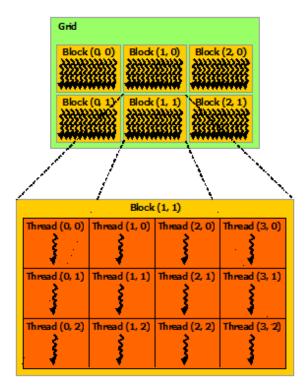

| Grid blocks layout, extracted from [4]                                   | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

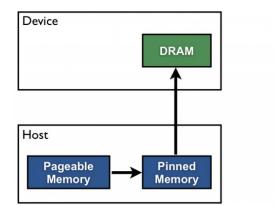

| Difference between pageable and pinned data transfers, obtained from [5] | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

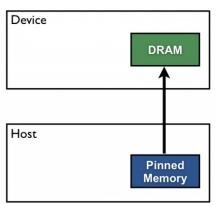

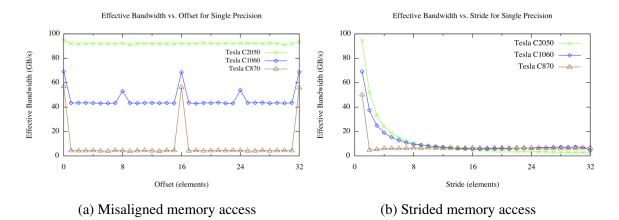

| Asynchronous vs synchronous transfers, adapted from [6]                  | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

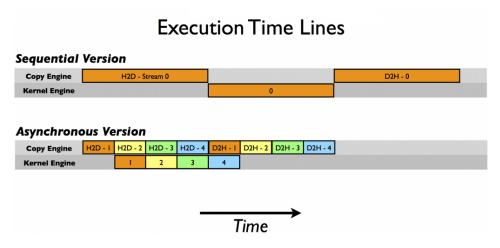

| The performance impact of different memory access patterns, ex-          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| tracted from [7]                                                         | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

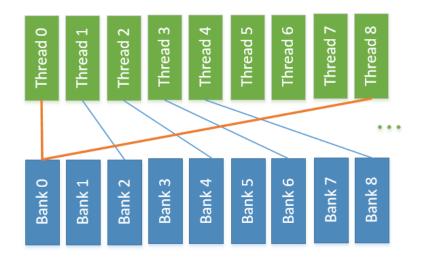

| Example of a 2-way bank conflict, obtained from [8]                      | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

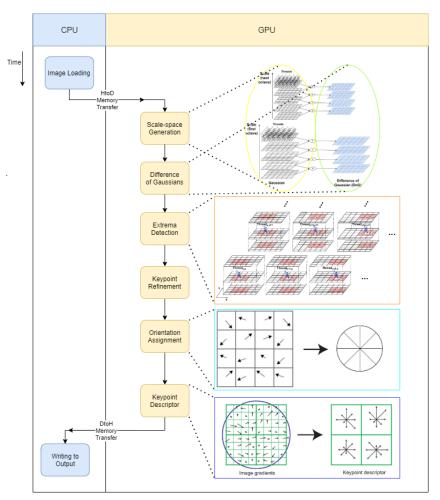

| The proposed execution flow of the SIFT algorithm on a GPU               | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

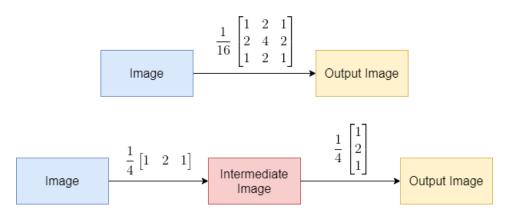

| Example of a spatially separable convolution using a Gaussian filter.    | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

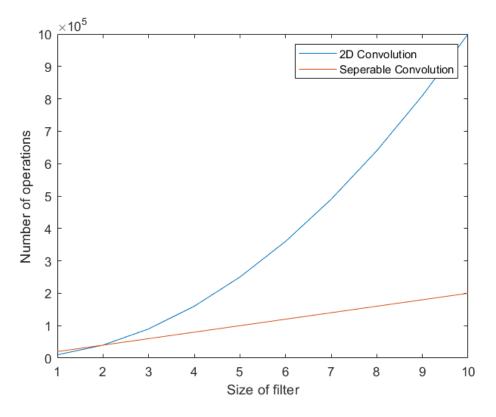

| 2D convolution versus separable convolution in a $100x100$ image         | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

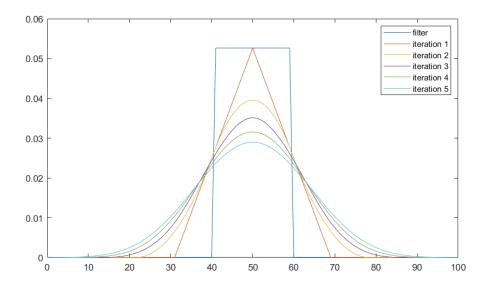

| Gaussian approximation using a box filter                                | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

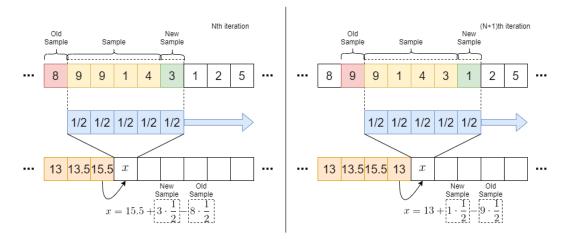

| Example of a 1D convolution with box filters using the sliding win-      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| dow method                                                               | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

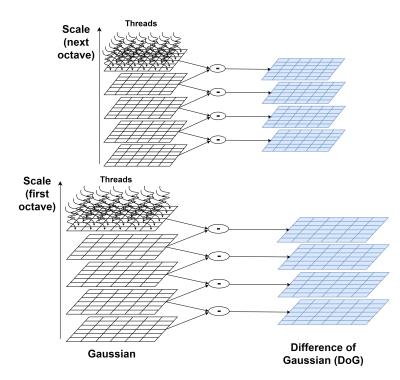

| Difference of Gaussians on the GPU                                       | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                          | Extrema detection, extracted from [1].Descriptor generation, obtained from [1].Example of image matching using SIFT.Example of image stitching using SIFT.Example of object detection using SIFT, adapted from [2].An example of a modern dual core CPU architecture.CPU vs GPU Architecture, adapted from [3].Processing Flow in CUDA.Scalability in CUDA, obtained from [4].GPU Memory Hierarchy, acquired from [4].Ofference between pageable and pinned data transfers, obtained from [5].Asynchronous vs synchronous transfers, adapted from [6].The performance impact of different memory access patterns, extracted from [7].Example of a 2-way bank conflict, obtained from [8].Che proposed execution flow of the SIFT algorithm on a GPU.Example of a spatially separable convolution using a Gaussian filter.2D convolution versus separable convolution in a 100x100 image .Gaussian approximation using a box filter.Che wethod.Convolution with box filters using the sliding window method. |

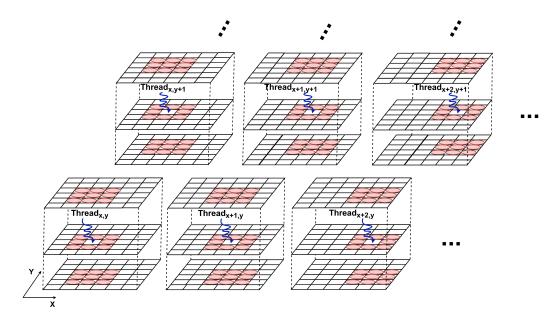

| 4.7                                                                                                          | Extrema Detection on the GPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 29                                     |

|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

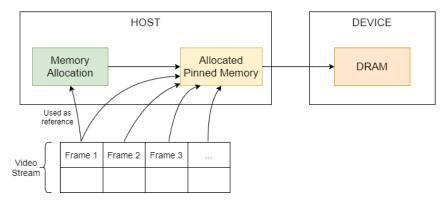

| 4.8                                                                                                          | Example of how a video stream can take advantage of pinned mem-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                        |

|                                                                                                              | ory transfers. Due to memory constraints, each frame must be pro-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                        |

|                                                                                                              | cessed sequentially, however the allocated memory space of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |

|                                                                                                              | first frame is reused by every other frame, hence allocation is only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                        |

|                                                                                                              | needed once.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 31                                     |

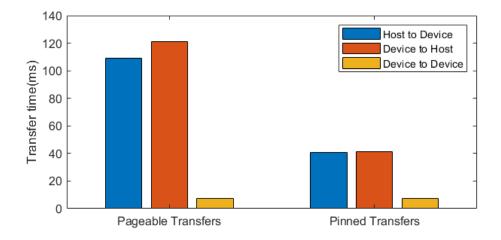

| 5.1                                                                                                          | HtoD, DtoH and DtoD transfer times for 5MB of data on a GTX 1060                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 35                                     |

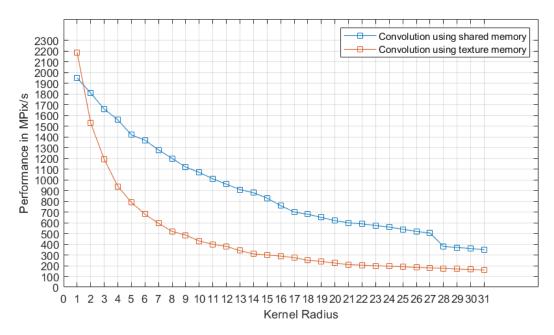

| 5.2                                                                                                          | Convolution using shared memory vs convolution using texture mem-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                        |

|                                                                                                              | ory, adapted from [9]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 36                                     |

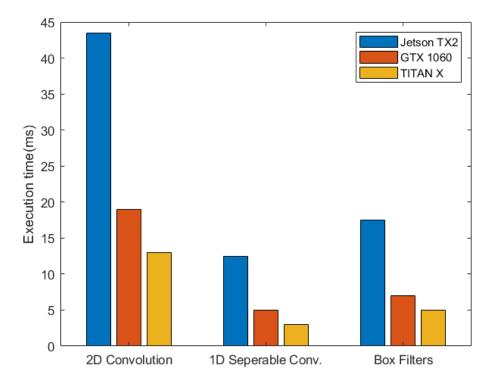

| 5.3                                                                                                          | The performance of the three convolution methods that were ana-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                        |

|                                                                                                              | lyzed in a 2560×1920 image using $\sigma = 10. \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37                                     |

| 5.4                                                                                                          | Comparison between the Gaussian convolution and Box convolu-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                        |

|                                                                                                              | tion using $\sigma = 10$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 38                                     |

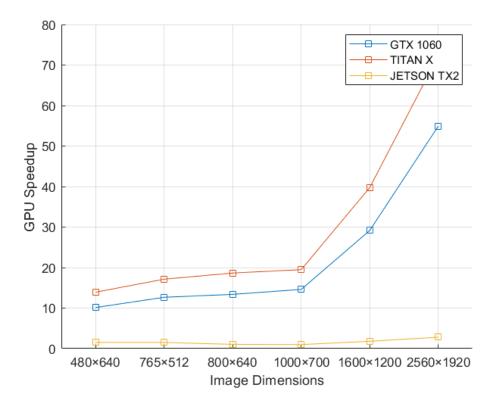

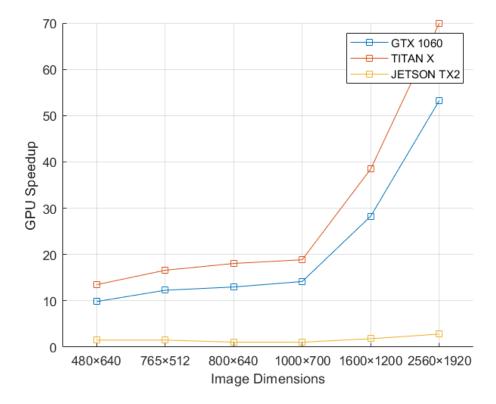

| 5.5                                                                                                          | Speedup of each device relative to the CPU while generating the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                        |

|                                                                                                              | scale-space.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39                                     |

| 5.6                                                                                                          | Speedup of each device relative to the CPU while locating extrema                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                        |

|                                                                                                              | points                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 41                                     |

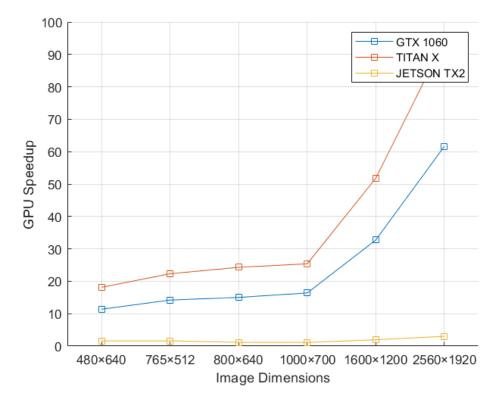

| 5.7                                                                                                          | Speedup of each device relative to the CPU while finding the orien-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                        |

|                                                                                                              | tation of each keypoint.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 42                                     |

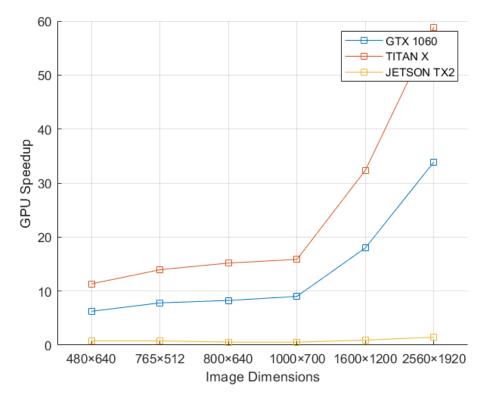

| 5.8                                                                                                          | Speedup of each device relative to the CPU while generating feature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                        |

|                                                                                                              | descriptors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 43                                     |

| 5.9                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                        |

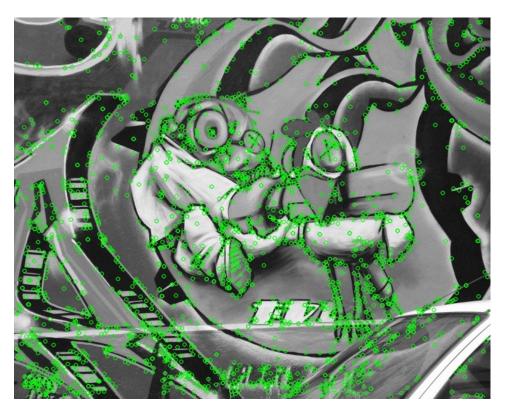

|                                                                                                              | 800x640 image from [10]: 2832 keypoints detected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44                                     |

| 5.10                                                                                                         | 800x640 image from [10]: 2832 keypoints detected.850x680 image from [10]: 8950 keypoints detected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 44<br>45                               |

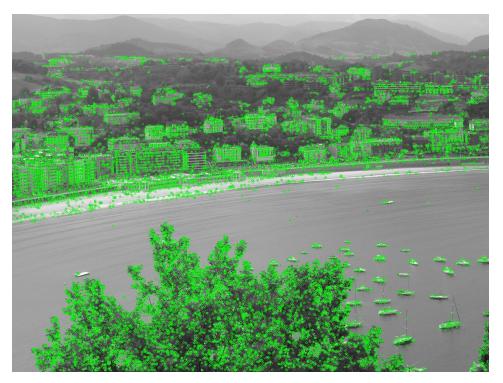

|                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                        |

| 5.11                                                                                                         | 850x680 image from [10]: 8950 keypoints detected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 45                                     |

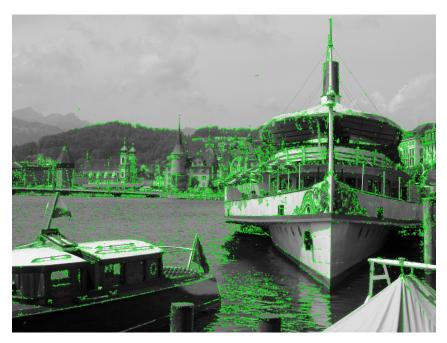

| 5.11<br>5.12                                                                                                 | 850x680 image from [10]: 8950 keypoints detected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 45<br>45                               |

| <ul><li>5.11</li><li>5.12</li><li>5.13</li></ul>                                                             | 850x680 image from [10]: 8950 keypoints detected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 45<br>45<br>46                         |

| <ol> <li>5.11</li> <li>5.12</li> <li>5.13</li> <li>5.14</li> </ol>                                           | 850x680 image from [10]: 8950 keypoints detected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 45<br>45<br>46<br>46                   |

| <ol> <li>5.11</li> <li>5.12</li> <li>5.13</li> <li>5.14</li> <li>5.15</li> </ol>                             | 850x680 image from [10]: 8950 keypoints detected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 45<br>45<br>46<br>46<br>46             |

| <ul> <li>5.11</li> <li>5.12</li> <li>5.13</li> <li>5.14</li> <li>5.15</li> <li>5.16</li> </ul>               | 850x680 image from [10]: 8950 keypoints detected.1600x1200 image from [11]: 18021 keypoints detected.2560x1920 image from [11]: 24432 keypoints detected.Example of scale invariance in matching.Another example of scale invariance in matching.Example of rotation invariance in matching.                                                                                                                                                                                                                                                                                                                                                                  | 45<br>45<br>46<br>46<br>46<br>47       |

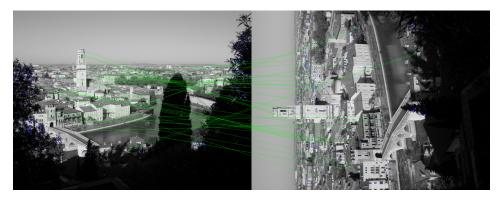

| <ul> <li>5.11</li> <li>5.12</li> <li>5.13</li> <li>5.14</li> <li>5.15</li> <li>5.16</li> <li>5.17</li> </ul> | 850x680 image from [10]: 8950 keypoints detected.1600x1200 image from [11]: 18021 keypoints detected.2560x1920 image from [11]: 24432 keypoints detected.Example of scale invariance in matching.Another example of scale invariance in matching.Example of rotation invariance in matching.Another example of rotation invariance in matching.                                                                                                                                                                                                                                                                                                               | 45<br>45<br>46<br>46<br>46<br>47<br>47 |

| 5.11<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18                                                 | 850x680 image from [10]: 8950 keypoints detected.1600x1200 image from [11]: 18021 keypoints detected.2560x1920 image from [11]: 24432 keypoints detected.Example of scale invariance in matching.Another example of scale invariance in matching.Example of rotation invariance in matching.Another example of rotation invariance in matching.Example of illumination invariance in matching.                                         | 45<br>45<br>46<br>46<br>47<br>47<br>47 |

| 5.11<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18                                                 | 850x680 image from [10]: 8950 keypoints detected.1600x1200 image from [11]: 18021 keypoints detected.2560x1920 image from [11]: 24432 keypoints detected.Example of scale invariance in matching.Another example of scale invariance in matching.Example of rotation invariance in matching.Another example of rotation invariance in matching.Example of rotation invariance in matching.Another example of illumination invariance in matching. | 45<br>45<br>46<br>46<br>47<br>47<br>47 |

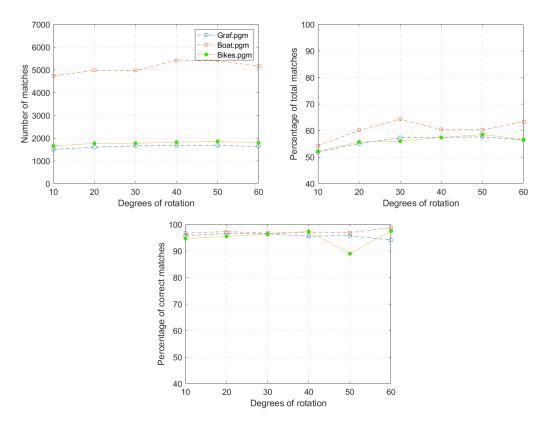

| 5.20 | Scale invariance analysis. Any time an image scales down in size,    |    |  |

|------|----------------------------------------------------------------------|----|--|

|      | the amount of information contained in the image decreases. For      |    |  |

|      | this reason, the number of keypoints and subsequent matches is ex-   |    |  |

|      | pected to decline as well                                            | 50 |  |

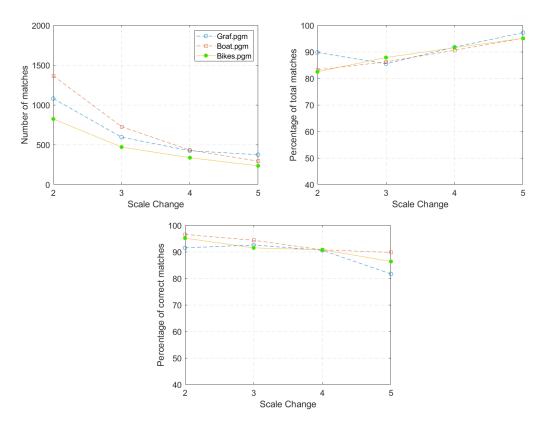

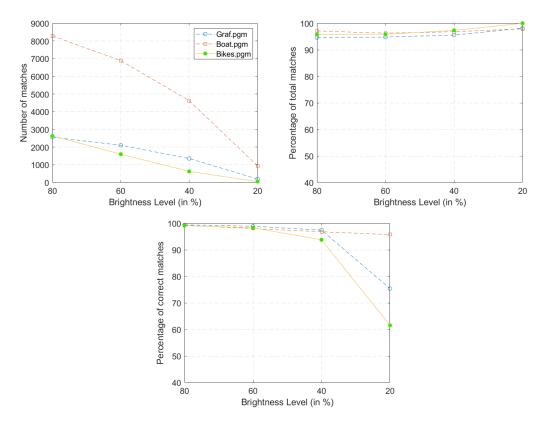

| 5.21 | Illumination invariance analysis. When the level of brightness is    |    |  |

|      | close to 20%, the number of detected keypoints and matches drops     |    |  |

|      | significantly. As a result, the quality of remaining matches becomes |    |  |

|      | uncertain as the number of correct matches decreases                 | 51 |  |

## **List of Tables**

| 2.1 | Performance of various implementations of the SIFT algorithm on    |    |  |  |

|-----|--------------------------------------------------------------------|----|--|--|

|     | the GPU                                                            | 11 |  |  |

| 5.1 | Test System Configurations                                         | 33 |  |  |

| 5.2 | GPU specifications                                                 | 33 |  |  |

| 5.3 | Accumulated times (in milliseconds) for the scale-space generation |    |  |  |

|     | of a 2560×1920 image                                               | 38 |  |  |

| 5.4 | Difference of Gaussians on CPU and GPU in milliseconds             | 40 |  |  |

| 5.5 | Summary of times(measured in milliseconds) and speedups of each    |    |  |  |

|     | segment in order to extract features from a 2560x1920 image        | 43 |  |  |

| 5.6 | Performance per watt of each device (FPS/W $\times$ 100)           | 44 |  |  |

## **List of Acronyms**

- GPU Graphics Processing Unit

- **CPU** Central Processing Unit

- **SIFT** Scale-invariant feature transform

- GPGPU General-Purpose computing on Graphics Processing Units

- CUDA Compute Unified Device Architecture

- ALU Arithmetic Logic Unit

- SM Streaming Multiprocessor

- SIMT Single Instruction Multiple Thread

- PCIe Peripheral Component Interconnect Express

- HPC High Performance Computing

- **OpenCL** Open Computing Language

- **DRAM** Dynamic Random-Access Memory

- SRAM Static Random-Access Memory

- **OS** Operating System

# Introduction

#### Contents

| 1.1 | Motivation           | 2 |

|-----|----------------------|---|

| 1.2 | Objectives           | 3 |

| 1.3 | Dissertation Outline | 3 |

#### 1. Introduction

In the field of computer vision, feature extraction has always been an intriguing topic of research. Its purpose is to eliminate redundancies from datasets, thus allowing derived values (features) to be unique and informative. In image processing, feature extraction is used to detect and isolate desired portions of an image or a video stream.

In order to do so, developers often resort to algorithms that are invariant to changes in scale, rotation, illumination, and, to some degree, affine distortions. All these characteristics are essential to Scale-invariant feature transform (SIFT), an algorithm that has stood the test of time and that it is still popular in various computer vision applications, such as, image registration [12], object recognition [13], motion tracking [14], 3D modelling [15], among others.

In the past decade, the growth of storage capacity [16] and quality of digital cameras has indirectly contributed to a significant increase in the size and resolution of digital images, which in turn has made feature extraction algorithms computationally more demanding. Under these circumstances, linear solutions implemented using the central processing unit (CPU) are limited by computational power and are no longer capable of maintaining real-time execution for large scale images.

#### **1.1 Motivation**

However, in the field of parallel computing, a group of architectures, traditionally linked to image rendering (mostly in games), has gained prominence within this area. Also known as graphics processing units (GPUs), their functionality has extended beyond the visualization domain, to also accommodate general-purpose processing on GPUs or GPGPU.

Companies and organizations such as Nvidia and The Khronos Group respectively, have designed APIs and frameworks (e.g., CUDA and OpenCL), thus providing developers with the ability to exploit the full potential of GPUs and to build faster parallel solutions for more resource-intensive problems.

Even though CUDA is exclusive to Nvidia GPUs, it is still far better optimized than its OpenCL counterpart, with speedups up to 30% when executing the same task on the same hardware [17]. As a result, this makes CUDA a preferable choice for this work.

Additionally, as AI-related applications (where feature extraction is included) started making the shift from the cloud down to the power-constrained edge, the demand for low-power solutions rose likewise. In order to meet this criterion, the current work purposes to exploit the parallel computational power of modern low-power GPUs and simultaneously perform algorithmic optimizations capable of re-

ducing computational complexity while incurring negligible accuracy losses.

Apart from that, while there are other feature extraction algorithms that are faster than SIFT, it cannot be overlooked that this algorithm is much more known and commonly used due to its high robustness and accuracy which other algorithms struggle to match [18]. It is therefore a suitable candidate to be parallelized on a GPU and to be the focal point of this thesis.

#### 1.2 Objectives

This thesis proposes to explore the parallelism of different families of GPUs in order to speedup and improve the energy efficiency of the SIFT algorithm. The main objectives of this work are:

- Review the state-of-art of the SIFT algorithm;

- Develop a parallel solution of SIFT using CUDA;

- Apply CUDA optimizations iteratively to the proposed solution;

- Measure and compare execution times as well as energy consumption of the proposed implementation;

- Evaluate the obtained results and the feasibility of the GPU for future applications that involve feature extraction.

#### **1.3 Dissertation Outline**

This thesis is organized into six chapters. The first chapter introduces the topic of the thesis, the motivation behind it and the main goals this work intends to achieve. Chapter 2 focuses on the structure of the SIFT algorithm. Chapter 3 presents and explains the differences between the CPU and GPU architectures, furthermore, it also introduces the CUDA programming model. Chapter 4 describes the methods that were tested and implemented in order to accelerate and optimize SIFT. Chapter 5 provides results alongside with their analysis. And finally, Chapter 6 concludes this thesis and presents some suggestions for future work.

## **Background on SIFT**

Contents

| 2.1 | The SIFT Algorithm | 5  |

|-----|--------------------|----|

| 2.2 | Related Work       | 10 |

This chapter introduces the theoretical concepts regarding feature extraction and the techniques that SIFT employs in order to obtain keypoints and features from digital images and video streams. Lastly, it is presented the performance and energy efficiency of several parallel approaches that were found in the literature.

#### 2.1 The SIFT Algorithm

SIFT can be decomposed into four major parts [1] [2]: Scale-Space creation (please see 2.1.1), extrema detection (see 2.1.2), attribution of orientations (2.1.3), and descriptor generation (2.1.4). Next, we address each step in detail.

#### 2.1.1 Creation of the Scale-Space

In image processing, scale-space is a technique that allows the representation of a given image at different scales. This is useful in SIFT because it grants scale invariance to the algorithm. Besides that, it can also remove unwanted details from the input image through recursive use of Gaussian filters, which, subsequently, also avoids the formation of aliasing artifacts [19]. Gaussian filters can be defined as

$$G(x,y) = \frac{1}{2\pi\sigma^2} e^{-\frac{x^2 + y^2}{2\sigma^2}},$$

(2.1)

where x and y are the axis coordinates and  $\sigma$  the standard deviation.

The scale-space is divided into groups of images with equal size that are increasingly blurry, each group is called an octave, and each image of an octave is referred to as a layer. The first octave usually begins with an  $(2\times)$  upscaled version of the input image. Some implementations make this an optional step and prefer to use the original image instead, however the present work tries to stay true to the algorithm and therefore includes the upscaling by default. After each octave, the Gaussian image with an accumulated blur of  $2\sigma$  of the initial layer is down-sampled by a factor of 2, creating a new octave. The cycle continues until the dimensions of the final octave reach a given threshold defined by the user.

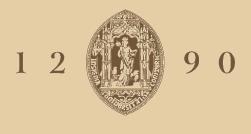

Once the scale-space is generated, the algorithm proceeds to detect blobs in every layer. These blobs are regions that present similar properties, such as brightness or color. These are aspects are crucial later for keypoint extraction. A simple way to locate these regions would be by applying a Laplacian filter over each of the generated images. However, this approach is computationally demanding, and not practical for most applications. D.Lowe, the author of SIFT, suggests to calculate the difference of Gaussians (DoG) instead, whose result is approximate to the Laplacian of the Gaussian and is overall much faster [1] [20] [21].

Figure 2.1: Difference of Gaussians, courtesy of [1].

Figure 2.1 shows that for each octave, a new group of layers is created from the subtraction of adjacent Gaussian layers.

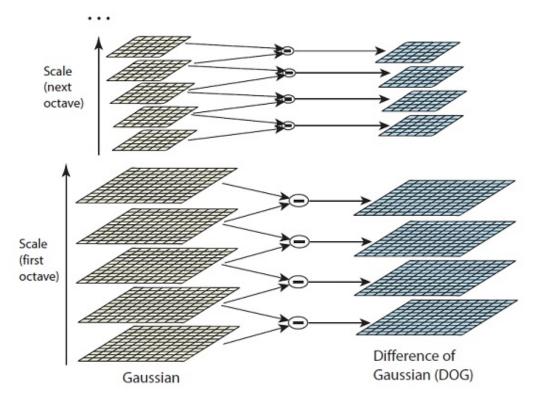

#### 2.1.2 Extrema Detection

The following step is to locate local extrema from the set of DoG images that were just generated. The algorithm transverses each point of each resulting nonbound layer and compares it to the neighboring pixels of that same layer and the adjacent ones (see Figure 2.2). This is equivalent to comparing each pixel with 26 neighbors in a  $3 \times 3 \times 3$  volume. If the selected pixel is a maximum or minimum of these 26 points, then it is considered to be a point of interest or a keypoint.

A later approach to SIFT [1] goes a step further and determines the sub-pixel location of each keypoint to improve matching and stability. This method uses the quadratic Taylor expansion to interpolate the DoG function  $D(x, y, \sigma)$  with the candidate keypoint as the origin. This Taylor expansion is given by:

$$D(\mathbf{x}) = D + \frac{\partial D^T}{\partial \mathbf{x}} \mathbf{x} + \frac{1}{2} \mathbf{x}^T \frac{\partial^2 D}{\partial \mathbf{x}^2} \mathbf{x}, \qquad (2.2)$$

where  $\mathbf{x} = (x, y, \sigma)^T$  is a column vector that represents the offset from the point of interest. The location of the extremum,  $\hat{\mathbf{x}}$ , is determined by taking the derivative of

Figure 2.2: Extrema detection, extracted from [1].

this function with respect to  $\mathbf{x}$  and setting it to zero, resulting in:

$$\hat{\mathbf{x}} = -\frac{\partial D^{-1}}{\partial \mathbf{x}^2} \frac{\partial D}{\partial \mathbf{x}},\tag{2.3}$$

where:

$$\frac{\partial D}{\partial \mathbf{x}} = \left(\frac{\partial D}{\partial x}, \frac{\partial D}{\partial y}, \frac{\partial D}{\partial \sigma}\right)^T \tag{2.4}$$

and:

$$\frac{\partial D}{\partial x} = \frac{D(x+1,y,\sigma) - D(x-1,y,\sigma)}{2}$$

$$\frac{\partial D}{\partial y} = \frac{D(x,y+1,\sigma) - D(x,y-1,\sigma)}{2}.$$

$$\frac{\partial D}{\partial \sigma} = \frac{D(x,y,\sigma+1) - D(x,y,\sigma-1)}{2}$$

(2.5)

One drawback this method usually has, is the detection of a vast number of extrema points, which may negatively impact performance, especially on larger scales.

Not all of these points provide useful information, in fact, some may have a very low contrast while others may be situated along edges. In either case, the best solution is to discard these points. For the former, we can analyze the intensity of each pixel by using the Taylor expansion in (2.2) and remove pixels whose value is less than a given threshold. For the latter, it is necessary to calculate the two gradients with orthogonal directions at the chosen point. From here we can attain three possible outcomes:

- A flat region, if both gradients are small;

- An edge, if one of the gradients is large and the other small;

• A corner, if both gradients are large.

Mathematically this can be achieved by analyzing the ratio between the eigenvalues of the second-order Hessian matrix, H:

$$H = \begin{bmatrix} D_{xx} & D_{xy} \\ D_{xy} & D_{yy} \end{bmatrix},$$

(2.6)

where  $D_{ij}$  are the derivatives obtained from the differences of the keypoint neighbors. Let  $\alpha$  and  $\beta$  be the smallest and largest eigenvalues respectfully. Then the trace and determinant of H can be computed as:

$$Tr(H) = D_{xx} + D_{yy} = \alpha + \beta$$

$$Det(H) = D_{xx}D_{yy} - (D_{xy})^2 = \alpha\beta$$

(2.7)

The SIFT algorithm discards keypoint candidates whose eigenvalue ratio  $r = \frac{\alpha}{\beta}$  is higher than a predefined threshold. Since only this ratio is required, the computation of the eigenvalues can be skipped. The ratio of the Hessian matrix determinant and its trace are related to r by:

$$\frac{Tr(H)^2}{Det(H)} = \frac{(\alpha+\beta)^2}{\alpha\beta} = \frac{(r\beta+\beta)^2}{r\beta^2} = \frac{(r+1)^2}{r}$$

(2.8)

Therefore, to determine if a point is within the threshold, SIFT checks for:

$$\frac{Tr(H)^2}{Det(H)} < \frac{(r+1)^2}{r}$$

(2.9)

#### 2.1.3 Orientation assignment

The next stage consists of assigning orientations for each keypoint. Orientation is an essential aspect of the algorithm, as it grants invariance to rotation. This is achieved by analyzing gradient directions and magnitudes around each point of interest. In practice, SIFT uses a 36 bin circular histogram to store the essential data(orientation and magnitudes of the gradients). Afterward, it checks for the bin with the highest contribution and defines it as the predominant orientation of the current keypoint. Additionally, if any other bin is at least 80% of the maximum, then another keypoint is generated in the same location, but with that bin's orientation.

The magnitudes and orientations of the gradients can be obtained with equations (2.10) and (2.11), respectively:

$$m(x,y) = \sqrt{(L(x+1,y) - L(x-1,y))^2 + (L(x,y+1) - L(x,y-1))^2},$$

(2.10)

$$\theta(x,y) = tan^{-1}\left(\frac{(L(x,y+1) - L(x,y-1))}{(L(x+1,y) - L(x-1,y))}\right),$$

(2.11)

where *m* is the magnitude of the gradient,  $\theta$  is the orientation, *L* is the smoothed image and *x*, *y* the coordinates of the point.

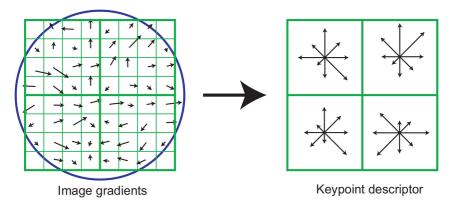

#### 2.1.4 Keypoint Descriptor

Finally, SIFT generates the keypoint descriptors/features, which are unique fingerprints that help identify important and unique regions of the original image. In order to achieve this, it first calculates the gradient map around each keypoint using a  $16 \times 16$  window, which is later divided into 16 cells  $4 \times 4$  (Figure 2.3 shows a simplified version with a  $8 \times 8$  window). Then in each cell the magnitude and orientation of the gradients are determined and their values are placed in an 8-bar histogram. In this histogram, the magnitude of the closest gradients to the keypoint weights more than the magnitude of more distant gradients. Once the histogram is completed, it produces a 128 element vector that, once normalized, corresponds to a feature.

Figure 2.3: Descriptor generation, obtained from [1].

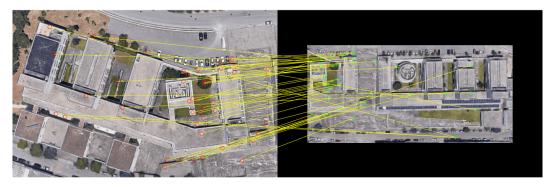

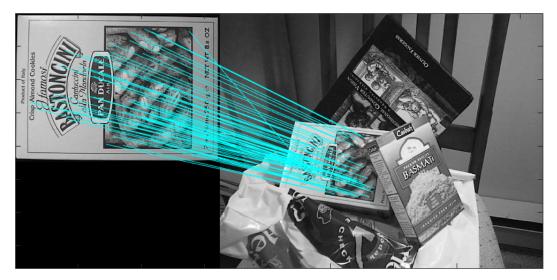

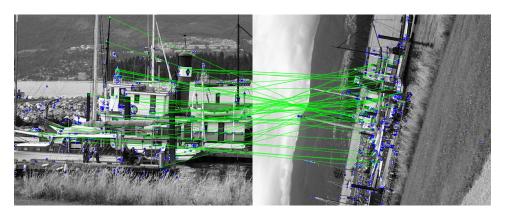

Some examples of applications using this algorithm can be seen in figures 2.4, 2.5 and 2.6, which illustrate image matching, image stitching and object detection, respectively.

Figure 2.4: Example of image matching using SIFT.

Figure 2.5: Example of image stitching using SIFT.

Figure 2.6: Example of object detection using SIFT, adapted from [2].

#### 2.2 Related Work