Diogo Henrique de Castro Caires

# DESENVOLVIMENTO DE UMA PLATAFORMA DIGITAL DE INTERFACE COM MATLAB/SIMULINK PARA CONTROLO DE CONVERSORES DE POTÊNCIA

Dissertação no âmbito do Mestrado integrado em Engenharia Eletrotécnica e de Computadores no ramo de Energia orientada pelo Professor Doutor André Manuel dos Santos Mendes e coorientada pelo Doutor Luís Miguel Antunes Caseiro apresentada ao Departamento de Engenharia Eletrotécnica e de Computadores da Faculdade de Ciência e Tecnologia da Universidade de Coimbra.

Setembro de 2019

# Desenvolvimento de uma plataforma digital de interface com Matlab/Simulink para controlo de conversores de potência

## Diogo Henrique de Castro Caires

Dissertação no âmbito do Mestrado Integrado em Engenharia Eletrotécnica e de Computadores, na área de Energia e apresentada à Faculdade de Ciências e Tecnologias da Universidade de Coimbra.

**Orientador:** Prof. Doutor André Manuel dos Santos Mendes

**Coorientador:** Doutor Luís Miguel Antunes Caseiro

Juri: Prof. Doutor Fernando José Teixeira Estêvão Ferreira

Prof. Doutor Tony Richard de Oliveira de Almeida

Prof. Doutor André Manuel dos Santos Mendes

Este trabalho insere-se no projeto SAICT-45-2017-POCI-01-0145-FEDER-029112 - PTDC/EEI-EEE/29112/2017, financiado pelo "Programa Operacional Temático Competitividade e Internacionalização" – FEDER e pela Fundação para a Ciência e a Tecnologia (FCT)—OE, e em parte pelo projeto UID/EEA/50008/2019, financiado pela FCT-OE.

## Agradecimentos

Começo por agradecer ao meu orientador, Professor Doutor André Manuel dos Santos Mendes e coorientador Luís Miguel Antunes Caseiro por todo o apoio, ajuda e acima de tudo confiança nas minhas capacidades.

Agradeço ao Instituto de Telecomunicações de Coimbra pelo material disponibilizado para a realização desta dissertação.

Agradeço aos meus amigos, que sempre me apoiaram e tornaram o meu percurso académico uma experiência única e enriquecedora.

Também agradeço aos meus colegas do laboratório de sistemas energéticos, em especial ao Tiago Oliveira e ao Válter Costa por todas as recomendações ao longo deste trabalho, bem como aos momentos de descontração.

O meu especial obrigado aos meus pais por todo o apoio ao longo do meu percurso, assim como pelos conselhos dados e todo o apoio desde sempre.

Quero agradecer a uma pessoa especial, à minha namorada Carolina, por todos os momentos partilhados e pelo incansável apoio ao longo desta jornada.

Por fim agradeço a todas as pessoas que têm vindo a me apoiar, pois sem o apoio de todos, certamente este percurso teria sido muito mais árduo.

#### Resumo

Com a evolução da tecnologia, os algoritmos de controlo passaram a ser cada vez mais avançados e complexos, o que suscitou um aumento das necessidade de processamento. Deste modo, as plataformas de controlo, a utilizar em sistemas de eletrónica de potência, têm de ter velocidades de processamento elevadas. Ao nível da investigação de sistemas de controlo e desenvolvimento de protótipos, podem ser escolhidos dois tipos de plataformas bastante distintos. Uma é o uso de plataformas para prototipagem rápida, que têm um elevado desempenho e uma programação simples, sendo que a sua desvantagem é o custo elevado. A outra solução é a utilização de placas de desenvolvimento que são uma solução económica, contudo a sua programação é complexa, ou então a sua capacidade de processamento é baixa.

O objetivo da tese é desenvolver uma solução que junte o baixo custo e o alto desempenho a uma programação fácil que recorra a ferramentas muito utilizadas. Com estes parâmetros, será possível apresentar uma solução de prototipagem com um custo-eficiência elevado, ideal para a investigação. Quanto à plataforma a utilizar, optou-se pela ZedBoard da *Digilent*, que apresenta uma capacidade de processamento alta e compatibilidade com a ferramenta *Matlab/Simulink*, muito utilizada a nível global.

O uso do *Matlab/Simulink* permite a implementação direta de código previamente desenvolvido, sem necessidade de conversão. Assim, é possível facilitar o processo de programação da plataforma e eliminar erros de transição que existem em plataformas configuradas diretamente com linguagem C/VHDL e não através do *Simulink*. Além do mais, o *Simulink* é um dos programas para desenvolvimento de algoritmos de controlo e simulação mais utilizado o que faz com que este seja o programa ideal para a solução a desenvolver.

Ao longo do trabalho, é pretendido aplicar na ZedBoard um algoritmo para controlo de um conversor de potência. Para isso, é necessário desenvolver ferramentas para programação da placa no *Simulink*, explorar as suas formas de processamento e garantir os requisitos do algoritmo. Após o desenvolvimento do modelo com o respetivo tipo de processamento, é realizada a programação da plataforma de controlo. Por último serão apresentadas as conclusões do trabalho bem como as propostas para trabalhos futuros.

**Palavras-Chave:** Plataformas Contorlo, Conversores de Potência, Zedboard, Protótipos, Sistemas Embebidos, *Simulink HDL Coder*, *Simulink Embedded Coder*, *Simulink SoC Blockset*.

#### **Abstract**

With the evolution of technology, the control platform became a critical feature in electric power systems. This leads to increased research of electric power systems. Demand has guaranteed the evolution of control platforms, with a price reduction and increase of processing power. Even with the price reduction of control systems, solutions focused in rapid prototyping still have a high cost. Either it is possible to use barebone solution with lower cost, but in this case the processing power is slow or the programming procedure is complex and slow. Due to these problems, it does not exit an appropriate solution for use in research projects or small companies with low investments capacities.

The objective of this work is to create a solution, wich fills a blank space in the control platform market. The solution needs to have a low cost and high processing capacity with an easy programming procedure. With these characteristics, the platform to be developed will be a prototyping solution with high cost-efficiency, ideal for use in research. The used platform is a ZedBoard from *Digilent*, which has a good processing capacity, is compact, and compatible with *Simulink*.

Using *Matlab/Simulink* ensures the direct implementation of code developed and tested, with no need for conversion. Due to the fact that the code doesn't need to be converted, as happen on platforms programmed in C/VHDL, conversion errors are eliminated. Furthermore, *Simulink* is one of the most used programs for develop control algorithms, testing and development, making this program ideal for programming the ZedBoard.

This thesis aims to develop a simple way to program a ZedBoard from Matlab/Simulink. The test model will be a power converter algorithm, and the used platform needs to guarantee all the control needs.

**Keywords:** Control Platforms, Power Converters, Zedboard, Prototypes, Embedded Systems, Simulink HDL Coder, Simulink Embedded Coder, Simulink SoC Blockset

# Índice

| A  | grade   | cimento | os —                                  | vii   |

|----|---------|---------|---------------------------------------|-------|

| R  | esumo   | •       |                                       | ix    |

| A  | bstrac  | et      |                                       | xi    |

| Li | ista de | Figura  | as                                    | xvii  |

| Li | ista de | Tabela  | as                                    | xxi   |

| Li | ista de | Acrón   | imos                                  | xxiii |

| 1  | Intr    | odução  |                                       | 1     |

|    | 1.1     | Motiva  | ação                                  | . 1   |

|    | 1.2     | Objeti  | vos                                   | . 2   |

|    | 1.3     | _       | mentação                              |       |

|    | 1.4     | Estruti | ura do Trabalho                       | . 3   |

| 2  | Esta    | do da A | Arte                                  | 5     |

|    | 2.1     | Sistem  | na de Conversão de Energia Elétrica   | 5     |

|    |         | 2.1.1   | Conversores de Eletrónica de Potência | . 7   |

|    |         |         | 2.1.1.1 Conversores Multinível        | . 7   |

|    |         | 2.1.2   | Estratégias de Controlo               | . 8   |

|    | 2.2     | Platafo | ormas de Controlo                     | 9     |

|    |         | 2.2.1   | Programação pelo Simulink             | 10    |

|    |         | 2.2.2   | Escolha da Plataforma                 |       |

|    |         | 2.2.3   | ZedBoard                              |       |

|    | 2.3     | Sistem  | nas UPS                               |       |

|    |         | 2.3.1   | Conversores Multinível nas UPS        | 13    |

|    |         | 2.3.2   | Controlo Preditivo                    | 13    |

|    |         | 2.3.3   | Retificador Ativo                     | 14    |

|    |         | 2.3.4   | Inversor                              | 16    |

|    |         | 2.3.5   | Requisitos do Sistema a Utilizar      | . 17  |

# Índice

| 3  | Dese        | envolvin                                                       | nento da l  | Plataforma                                       | 19 |  |  |

|----|-------------|----------------------------------------------------------------|-------------|--------------------------------------------------|----|--|--|

|    | 3.1         | Escolh                                                         | a ADCs .    |                                                  | 20 |  |  |

|    |             | 3.1.1                                                          | Funciona    | amento Pmod AD1                                  | 20 |  |  |

|    | 3.2         | Config                                                         | uração da   | Plataforma                                       | 21 |  |  |

|    |             | 3.2.1                                                          | Módulos     | s dos Pmod AD1                                   | 21 |  |  |

|    |             | 3.2.2                                                          | Verificaç   | ção da aquisição de dados em simultâneo          | 22 |  |  |

|    |             | 3.2.3 Aquisição de Dados e Atualização de Saídas em Simultâneo |             |                                                  |    |  |  |

|    |             | 3.2.4                                                          | Velocida    | des de Transferência de Dados                    | 24 |  |  |

|    |             | 3.2.5                                                          | Adição d    | de ADC's ao IP CORE                              | 26 |  |  |

| 4  | Prog        | gramaçâ                                                        | ío da Plat  | taforma de Controlo                              | 27 |  |  |

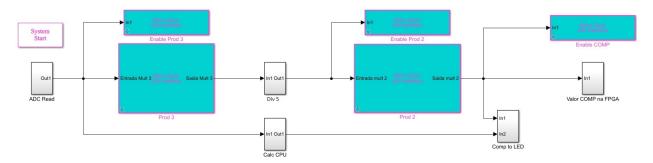

|    | 4.1         | Proces                                                         | samento d   | lo Algoritmo                                     | 27 |  |  |

|    |             | 4.1.1                                                          | Processa    | imento na FPGA                                   | 29 |  |  |

|    |             |                                                                | 4.1.1.1     | Conversão do Código para a ZedBoard              | 30 |  |  |

|    |             |                                                                | 4.1.1.2     | Aplicação do Algoritmo na ZedBoard               | 31 |  |  |

|    |             |                                                                | 4.1.1.3     | Resultados Obtidos                               | 32 |  |  |

|    |             | 4.1.2                                                          | Processa    | mento no ARM                                     | 33 |  |  |

|    |             |                                                                | 4.1.2.1     | Sincronismo Através de Esperas                   | 34 |  |  |

|    |             |                                                                | 4.1.2.2     | Sincronismo Através de uma Verificação Periódica | 36 |  |  |

|    |             | 4.1.3                                                          | Processa    | mento Híbrido                                    | 36 |  |  |

|    |             |                                                                | 4.1.3.1     | Sincronismo com Múltiplas Esperas                | 37 |  |  |

|    | 4.2         | Alterna                                                        | ativa de Pr | rocessamento                                     | 38 |  |  |

|    |             | 4.2.1                                                          | SoC Blo     | ckset                                            | 38 |  |  |

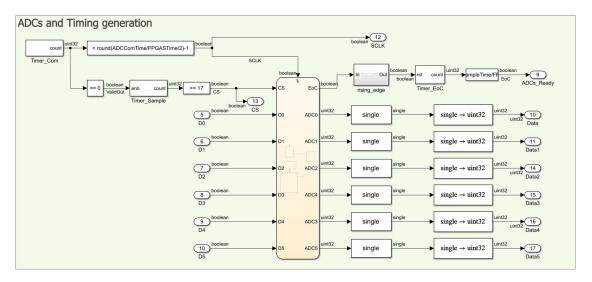

|    |             |                                                                | 4.2.1.1     | Desenvolvimento dos ADCs                         | 39 |  |  |

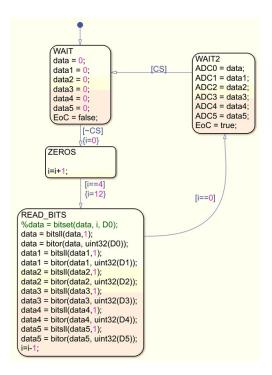

|    |             |                                                                | 4.2.1.2     | Interrupções                                     | 41 |  |  |

| 5  | Con         | clusões                                                        | e Sugestõ   | ses para Trabalhos Futuros                       | 45 |  |  |

|    | 5.1         | Conclu                                                         | ısões       |                                                  | 45 |  |  |

|    | 5.2         | Sugest                                                         | ões para T  | Trabalhos Futuros                                | 46 |  |  |

| Re | eferên      | cias                                                           |             |                                                  | 47 |  |  |

| A  | Man         | ual Ins                                                        | talação     |                                                  | 49 |  |  |

|    | <b>A.</b> 1 | Instala                                                        | ção Matla   | b                                                | 49 |  |  |

|    | A.2         | Instala                                                        | ção Vivad   | 0                                                | 50 |  |  |

|    | A.3         | Conec                                                          | ção ao Hai  | rdware e testes                                  | 50 |  |  |

| В  | Man         | ual Util                                                       | lização     |                                                  | 51 |  |  |

|    | B.1         | Leitura                                                        | de Dados    | s da FPGA no Matlab/Simulink                     | 51 |  |  |

|    | B.2         | Gerar l                                                        | P Core at   | ravés do Simulink                                | 59 |  |  |

|    | B.3         | Utiliza                                                        | r o "HDL    | Workflow Advisor"                                | 61 |  |  |

|   |             | Índ                                             | lice |

|---|-------------|-------------------------------------------------|------|

|   | B.4         | Alteração do Projeto no <i>Vivado</i>           | 67   |

| C | Cód         | igo VHDL dos IP Cores utilizados                | 71   |

|   | <b>C</b> .1 | Código VHDL da <i>Digilent</i> para os Pmod AD1 | 71   |

|   | C.2         | Código VHDL para Flip Flop                      | 74   |

|   | C.3         | Código VHDL para múltiplos Pmod AD1             | 75   |

| D | Con         | versão Blocos Retificador Ativo                 | 81   |

| E | Zed         | Board e Plataformas Utilizadas no Laboratório   | 87   |

# Lista de Figuras

| 2.1  | Esquema de um sistema de conversão de energia elétrica                         | 6  |

|------|--------------------------------------------------------------------------------|----|

| 2.2  | Esquema de um inversor NPC de 3 níveis                                         | 8  |

| 2.3  | Algumas das estratégias de controlo mais comuns                                | 9  |

| 2.4  | Arquitetura de um SoC Zynq                                                     | 11 |

| 2.5  | Modelo de um sistema UPS                                                       | 12 |

| 2.6  | Retificador trifásico multinível do tipo NPC                                   | 14 |

| 2.7  | Diferentes vectores de tensão representados no plano $\alpha\beta$             | 15 |

| 2.8  | Inversor trifásico multinível do tipo NPC                                      | 16 |

| 2.9  | Sistema <i>Back-to-Back</i> a utilizar                                         | 17 |

| 3.1  | Medidas a efetuar no sistema                                                   | 19 |

| 3.2  | Pmod AD1 da Digilent                                                           | 20 |

| 3.3  | Funcionamento transferência de dados do Pmod AD1 da Digilent                   | 20 |

| 3.4  | Módulo Vivado Pmod AD1                                                         | 21 |

| 3.5  | Board Defenition para 2 ADC PMOD AD1                                           | 22 |

| 3.6  | Valores adquiridos pelos 2 ADCs de um módulo, com uma frequência de amostragem |    |

|      | de 8kHz                                                                        | 23 |

| 3.7  | Ampliação dos valores adquiridos pelos 2 ADCs de um módulo, com uma frequên-   |    |

|      | cia de amostragem de 8kHz                                                      | 23 |

| 3.8  | Módulo FF no Vivado                                                            | 24 |

| 3.9  | Simulação ao código VHDL do FF desenvolvido                                    | 24 |

| 3.10 | Esquema do envio de dados pelo Pmod AD1                                        | 25 |

| 3.11 | Forma de onda do sinal SCLK a 2 MHz e a 20 MHz                                 | 25 |

| 3.12 | Valor adquiridos pelos 4 ADC, a uma amostragem de 8kHz                         | 26 |

| 4.1  | Fluxograma da programação ZedBoard pelo Simulink                               | 28 |

| 4.2  | Esquema de processamento de dados apenas pela FPGA                             | 29 |

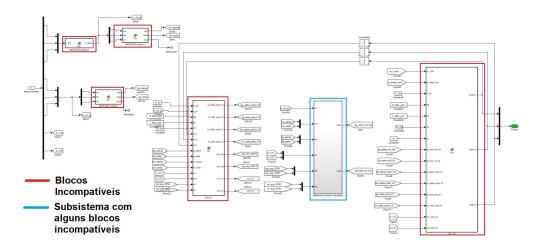

| 4.3  | Modelo do Simulink com os blocos do código do retificador incompatíveis com o  |    |

|      | HDL Coder                                                                      | 30 |

| 4.4  | Algoritmo do bloco responsável por estimar os valores das variáveis no ciclo   |    |

|      | seguinte, após a sua conversão                                                 | 31 |

## Lista de Figuras

| 4.5  | Modelo <i>Vivado</i> a implementar na ZedBoard                                   | 32 |

|------|----------------------------------------------------------------------------------|----|

| 4.6  | Esquema de processamento de dados apenas pelo ARM                                | 33 |

| 4.7  | Fluxograma para sincronização de dados com recurso à espera ativa                | 35 |

| 4.8  | Variação do sinal de <i>clock</i> do ARM e da FPGA                               | 35 |

| 4.9  | Esquema de processamento de dados híbrido                                        | 36 |

| 4.10 | Modelo Simulink, para verificação do sincronismo                                 | 37 |

| 4.11 | Exemplo da camada superior de um projeto do SoC Blockset                         | 39 |

| 4.12 | Esquema para implementação do ADC no SoC Blockset                                | 40 |

| 4.13 | Algoritmo do ADC desenvolvido no Add-On Stateflow do Simulink                    | 40 |

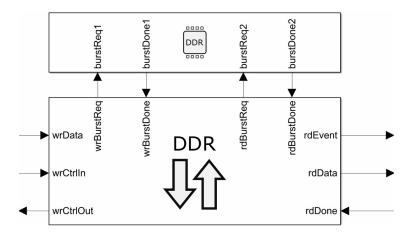

| 4.14 | Blocos do controlo e canal de memória                                            | 41 |

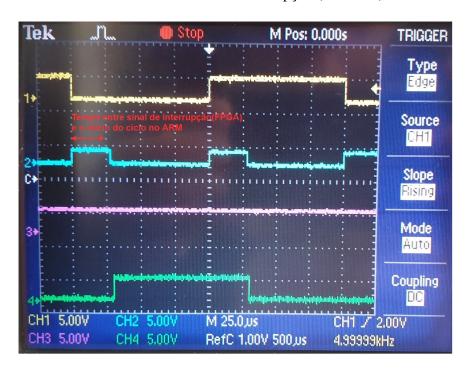

| 4.15 | Resultados de envio de dados pela memória RAM                                    | 42 |

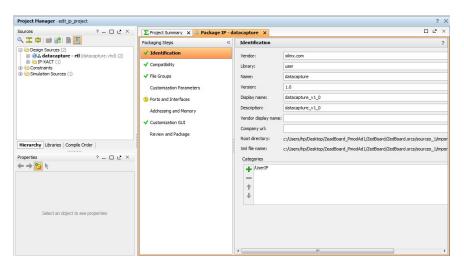

| B.1  | Gui para gerar IP Core para captura de dados                                     | 52 |

| B.2  | Seleção "Board" para um novo projeto.                                            | 52 |

| B.3  | Painel de navegação no lado esquerdo com a opção "Create Block Design"           | 53 |

| B.4  | Esquema básico da placa ZedBoard                                                 | 53 |

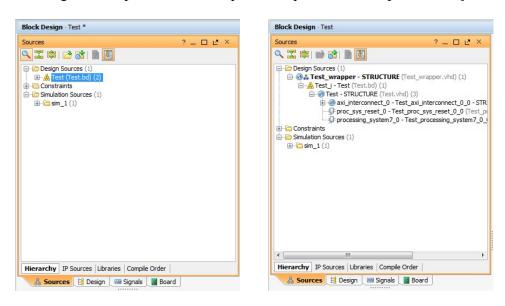

| B.5  | "Design Sources" antes (a) e depois (b) de executar o HDL wrapper                | 54 |

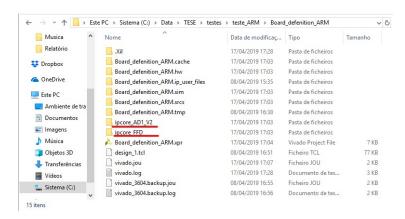

| B.6  | Exemplo de localização das pastas com os ficheiros VHDL dos IP Cores             | 54 |

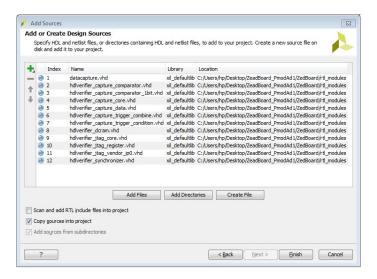

| B.7  | Exemplo da janela de adição de ficheiros VHDL                                    | 55 |

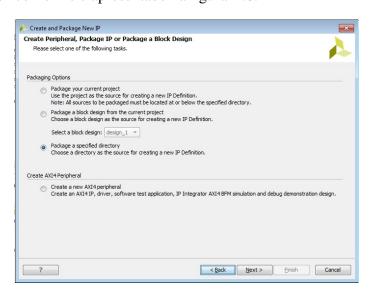

| B.8  | Ferramenta "Create and Package IP Core"                                          | 55 |

| B.9  | Projeto temporário criado pela ferramenta " Create and Package New IP " do passo |    |

|      | anterior                                                                         | 56 |

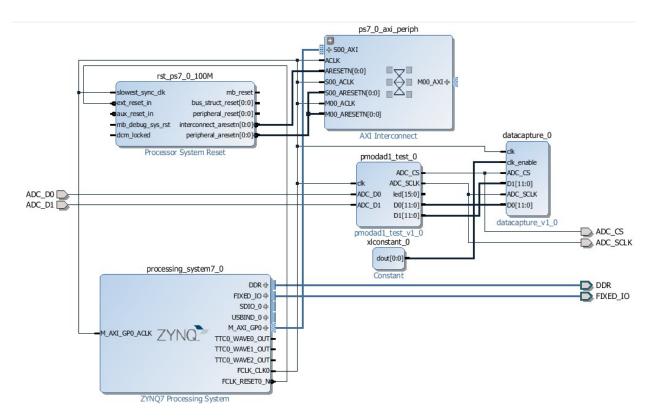

| B.10 | Zedboard "block design" com os IP Cores "datacapture" e "pmodad1 _test"          | 57 |

| B.11 | Ficheiro ".xdc" com definição da correspondência entre pinos da ZedBoard com o   |    |

|      | conector JA1                                                                     | 58 |

| B.12 | Matlab Data Capture GUI                                                          | 58 |

| B.13 | Ficheiro da ZedBoard plugin _board.m                                             | 60 |

| B.14 | Ficheiro plugin _rd.m da ZedBoard                                                | 61 |

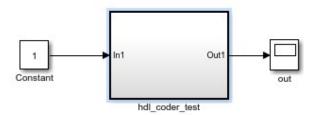

| B.15 | Exemplo de um subsistema onde será executado o workflow advisor                  | 62 |

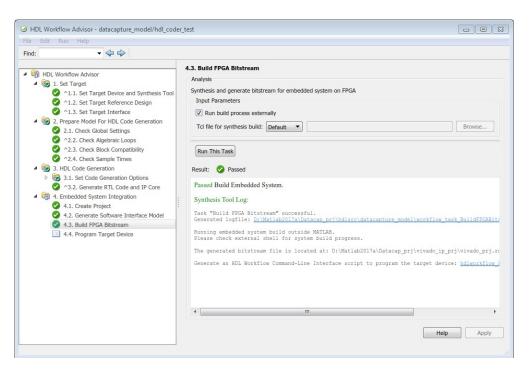

| B.16 | Feramenta HDL Workflow Advisor                                                   | 63 |

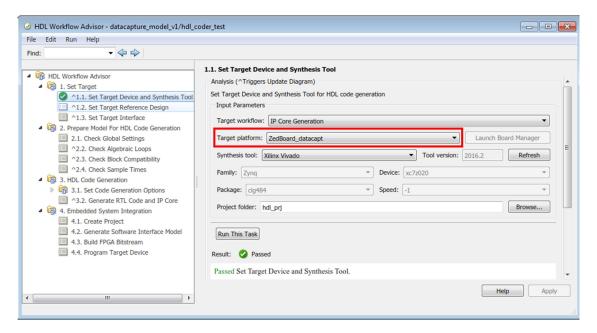

| B.17 | Janela do HDL Workflow Advisor durante o a escolha da plataforma                 | 63 |

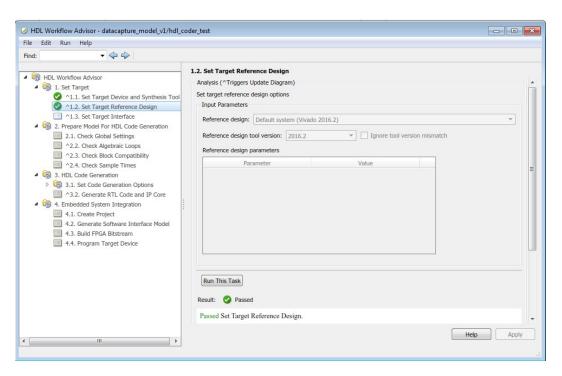

| B.18 | Janela do HDL Workflow Advisor durante o ponto 1.2                               | 64 |

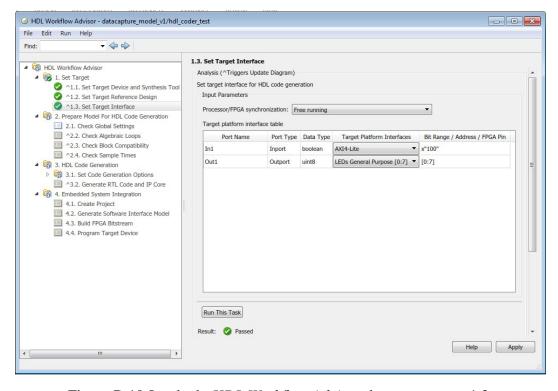

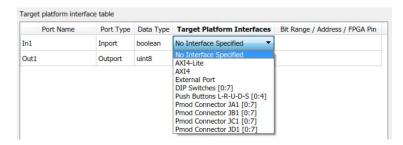

| B.19 | Janela do HDL Workflow Advisor durante o ponto 1.3                               | 64 |

| B.20 | Janela do HDL Workflow Advisor durante o ponto 1.3                               | 65 |

| B.21 | Janela do HDL Workflow Advisor no ponto para criar o projeto no Vivado           | 66 |

| B.22 | Janela do HDL Workflow Advisor após criação do projeto no Vivado                 | 66 |

| B.23 | Janela do Vivado com o projeto criado a partir do Workflow Advisor               | 68 |

| B.24 | Ferramenta "create port" para adicionar portas de entrada e/ou saida no Vivado   | 69 |

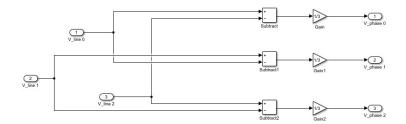

| D 1  | Blocos do algoritmo incompatíveis com o <i>HDL Coder</i>                         | 21 |

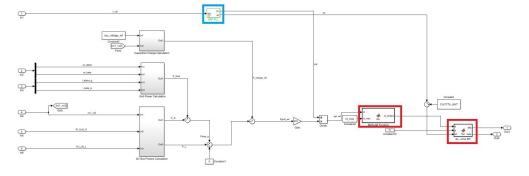

| D.2                                                                                | Interior de um dos blocos incompatíveis com o HDL Coder            | 81 |  |  |

|------------------------------------------------------------------------------------|--------------------------------------------------------------------|----|--|--|

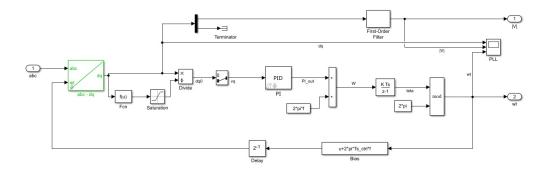

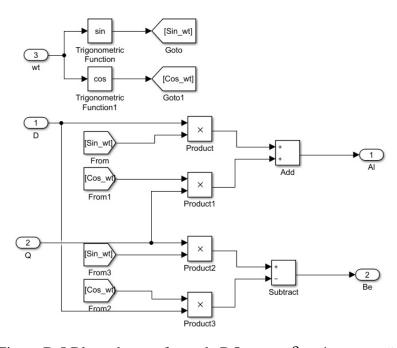

| D.3                                                                                | Bloco responsável pela PLL existente no algoritmo                  | 82 |  |  |

| D.4                                                                                | Bloco que converte as tensões complexas nas tensões simples        | 82 |  |  |

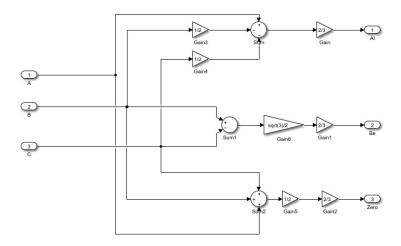

| D.5                                                                                | Bloco da transformada DQ para $\alpha\beta$ após conversão         | 82 |  |  |

| D.6                                                                                | Bloco da transformada ABC para $\alpha\beta$ após conversão        | 83 |  |  |

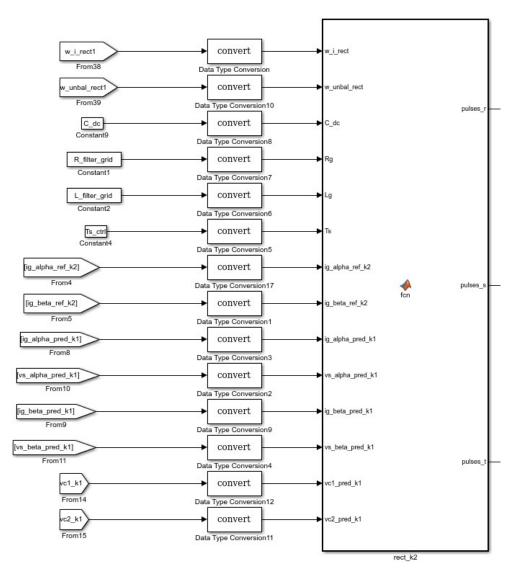

| D.7 Bloco "rect _K2" o único bloco onde foi aplicado a conversão de variáveis para |                                                                    |    |  |  |

|                                                                                    | ponto fixo                                                         | 83 |  |  |

| D.8                                                                                | Bloco "rect <sub>k</sub> 1" apsconverso                            | 84 |  |  |

| D.9                                                                                | Bloco responsável pela PLL após conversão dos blocos incompatíveis | 85 |  |  |

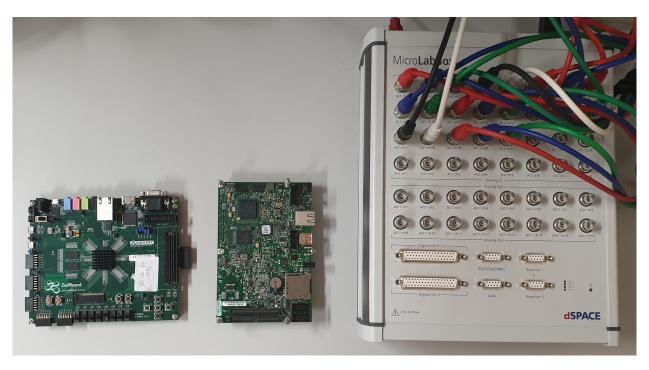

| E.1                                                                                | Imagem da ZedBoard, e o seu tamanho comparado a uma caneta         | 87 |  |  |

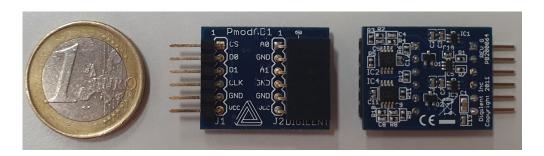

| E.2                                                                                | Módulos Pmod AD1 utilizados no projeto                             | 87 |  |  |

| E.3                                                                                | Comparação de tamanhos entre ZedBoard, SB Rio e MicroLabBox        | 88 |  |  |

# Lista de Tabelas

| 2.1 | Comparação entre Várias Soluções de Mercado e Placas de Controlo          | 11 |

|-----|---------------------------------------------------------------------------|----|

| 2.2 | Diferentes estados de cada braço do retificador                           | 15 |

| 2.3 | Entradas e saídas do algoritmo de controlo                                | 17 |

| 4.1 | Valores de utilização ZedBoard para diferentes tipos de compilação        | 33 |

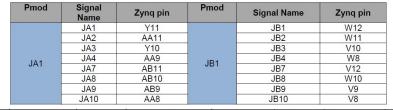

| B.1 | Correspondência entre pinos Zedboard e conector Pmod JA1                  | 57 |

| B.2 | Correspondência entre os id dos pinos da ZedBoard com as suas portas PMOD | 69 |

# Lista de Acrónimos

#### Acrónimos e Abreviaturas

AC Alternating Current

ADC Conversor Analógico para Digital

ARM Advanced RISC Machine

AXI4 Advanced eXtensible Interface 4

CHB Cascade H-Bridge

CS Chip Select

DC Direct Current

DMA Direct Memory Access

DSPs Digital Signal Processor

FCs Flying Capacitors

FIFO First In First Out

FOC Field Oriented Control

FPGA Field-programmable Gate Array

IGBT Insulated Gate Bipolar Transistor

LED Light Emitting Diode

LUT Look-up-Table

NPC Neutral Point Clamped

SCLK Serial Clock

UPS Uninterruptible Power Supply

# Capítulo 1

# Introdução

No primeiro capítulo serão enunciados os objetivos da dissertação, as motivações para a sua realização, e a estratégia de implementação a utilizar. Este ponto será finalizado com uma apresentação da estrutura da dissertação, com uma indicação das temáticas a serem abordadas em cada um dos capítulos.

A plataforma a desenvolver, insere-se no projeto "DRIFT" (Datacenter Resilience Increase through Fault Tolerance in UPS systems) que consiste no desenvolvimento de um protótipo de uma fonte de alimentação ininterrupta (UPS) de alta credibilidade para datacenter a decorrer no Instituto de Telecomunicações de Coimbra, no Laboratório de Sistemas de Energéticos. O projeto, deparou-se com a necessidade de, após desenvolvimento do sistema de controlo no Simulink, e a verificação do funcionamento do mesmo, escolher entre dois tipos de plataformas: Uma plataforma que permitisse uma programação simples, utilizando o Simulink para implementação do algoritmo, mas que apresentasse um custo elevado; Ou uma plataforma económica mas com uma processo de programação complexo, devido à necessidade de conversão do algoritmo desenvolvido.

O objetivo do trabalho é desenvolver uma solução intermédia, que tenha um custo baixo mas que permita a implementação de algoritmos pelo *Simulink* de forma a utilizar o sistema de controlo já desenvolvido. Outro aspeto desta solução é ter dimensões reduzidas, de forma a ser facilmente incorporada no protótipo em desenvolvimento.

## 1.1 Motivação

O desenvolvimento de técnicas de controlo mais avançadas e complexas fez com que as plataformas de controlo precisassem de uma maior capacidade de processamento. O aumento dos requisitos destas plataformas levou a um grande desenvolvimento e à redução do custo das mesmas. As soluções para prototipagem rápida dispõem de uma programação simples e elevada velocidade de processamento. Contudo, estas plataformas ainda apresentam custos elevados. Em alternativa, existem placas de desenvolvimento que têm custos baixos, contudo apresentam uma programação complexa, ou então uma capacidade de processamento reduzida.

#### Introdução

Ainda existem poucas plataformas adequadas para investigação, com boa capacidade de processamento e que permitam uma programação pelo *Simulink* a um baixo custo. Esta falha no mercado das plataformas digitais, motivou a procura de uma solução para satisfizer estas necessidades. Posto isto, o trabalho a realizar é uma mais valia para o grupo de investigação, pois providencia uma solução com custo-eficiência bastante apelativo.

## 1.2 Objetivos

O objetivo principal é o desenvolvimento de uma plataforma de controlo de baixo custo, para aplicação em protótipos de conversores de eletrónica de potência. A solução deverá ter uma capacidade de processamento elevada, embora com um preço reduzido. Esta capacidade de processamento e baixo custo, fará com que a solução tenha um custo-eficiência bastante elevado e apelativo.

Quanto à programação da plataforma, esta deve ser compatível com o *Matlab/Simulink* que permite o desenvolvimento de um algoritmo, simulação e posteriormente a implementação do mesmo. O *Simulink* apresenta vantagens não só a nível da implementação, uma vez que o uso do código é direto, mas também oferece uma programação simples (programação por blocos) e uma grande quantidade de informação devido aos inúmeros utilizadores do programa.

No decorrer do trabalho são desenvolvidas as ferramentas para programação da plataforma a partir do *Simulink* e são asseguradas as necessidades do sistema de controlo a implementar. Por último, pretende-se implementar um algoritmo na plataforma desenvolvida, bem como realizar testes e medições comparando a solução desenvolvida com uma já existente no mercado.

## 1.3 Implementação

A implementação pode ser dividida em duas partes distintas: Uma secção inicial onde será desenvolvido o modelo de *Simulink* para a plataforma, e uma segunda secção onde o algoritmo será implementado no modelo desenvolvido.

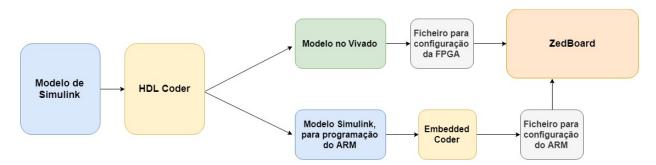

O desenvolvimento do modelo será realizado através das extensões (*Add-Ons*) "*Embedded Coder*" e "*HDL Coder*" que permitem a adaptação dos modelos do *Simulink* às plataformas digitais. Neste ponto, será verificado o funcionamento do modelo desenvolvido, e se o mesmo assegura os requisitos do algoritmo de controlo a implementar.

Após o desenvolvimento das ferramentas para programação da ZedBoard pelo *Simulink*, será efetuada a sua programação. Na implementação do algoritmo de controlo, é possível configurá-lo através de diversas formas de processamento. Como a plataforma a utilizar contém duas unidades de processamento, nomeadamente um ARM e uma FPGA, é possível executar o algoritmo apenas numa das unidades ou em ambas extraindo as vantagens de cada uma.

Para concluir, será ainda explorado o *SoC Blockset*, que é uma nova extensão do *Simulink* (adicionada na versão 2019a), que adiciona novas funcionalidades à programação de plataformas digitais, e sistemas embebidos.

Concluída a implementação do algoritmo na plataforma de controlo, será verificado o desempenho do sistema, por comparação com a plataforma *MicroLabBox* da *dSPACE*.

#### 1.4 Estrutura do Trabalho

O presente documento está dividido em cinco capítulos distintos, sendo o primeiro capítulo composto por uma pequena introdução e pelas motivações que levaram à realização deste trabalho.

O capítulo 2 apresenta uma pequena introdução aos sistemas de conversão de energia elétrica. Aborda a temática das plataformas de controlo existentes e a escolha da plataforma a desenvolver. No fim deste capítulo será explicado os sistemas UPS a utilizar, bem como o seu sistema de controlo.

Quanto ao capítulo 3 é apresentado o trabalho realizado ao nível da plataforma, sendo explicado a adição dos ADCs, a verificação da aquisição de dados simultânea, e a verificação da actualização de dados em simultâneo com a aquisição.

No capítulo 4, o último referente ao trabalho desenvolvido, é exposto o modo como se realiza a programação da plataforma de controlo, e os diferentes modos de processamento do algoritmo na ZedBoard. Este capítulo será finalizado com a exploração da ferramenta *SoC Blockset* para programação da ZedBoard, e as diferenças que esta apresenta em relação ao *HDL Coder* e *Embedded Coder*.

Por fim no capítulo 5 serão apresentadas as conclusões do trabalho, bem como as sugestões para trabalhos futuros.

# Capítulo 2

# Estado da Arte

Este capítulo tem como principal intuito explicar qual a função da plataforma a desenvolver bem como o seu enquadramento nos sistemas de eletrónica de potência. Na primeira secção será explicado o funcionamento dos sistemas de conversão de energia elétrica. Seguidamente na secção 2.2 será falado das plataformas de controlo, e como se procedeu à escolha da plataforma para o trabalho a desenvolver.

Verificado o enquadramento das plataformas de controlo e os sistemas onde estas são utilizadas, passar-se-à a um sistema concreto, nomeadamente, uma fonte de alimentação ininterrupta (*Uninterruptible Power Source -* UPS) e os seus constituintes.

## 2.1 Sistema de Conversão de Energia Elétrica

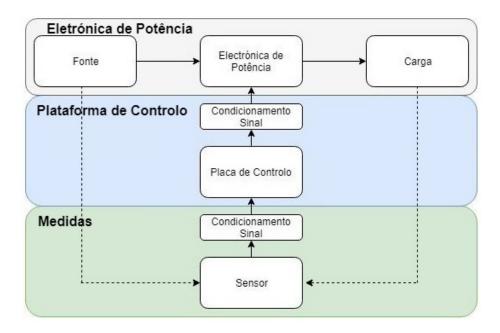

Um sistema de conversão de energia elétrica é constituído por três partes, representadas na figura 2.1. É constituído por uma componente de eletrónica de potência, que converte os níveis de corrente e tensão da fonte (entrada) para os valores pretendidos na carga (saída) e permite ainda o controlo do fluxo energético em função do que é necessário. Existe uma zona de medição que, através de sensores ligados à carga, permite obter os valores instantâneos das grandezas elétricas necessárias, enviando-os para a placa de controlo. Finalmente a placa controladora que executa o algoritmo de controlo, enviando os pulsos de activação para os semicondutores do conversor de eletrónica de potência, permitindo variar o fluxo de energia consoante os parâmetros do algoritmo.

A zona de eletrónica de potência é constituída por todo o sistema elétrico e o conversor de potência. O conversor de potência é responsável por interligar ambas as partes do sistema, permitindo que estas possam ter níveis e tipos de correntes e tensões diferentes. Existem quatro tipos de conversores de potência, distintos em função das formas de onda à entrada e saída do conversor. Contudo, todos têm em comum o facto de ser possível controlar o fluxo de energia entre os dois lados do conversor. Os diferentes conversores são:

**AC-DC ou Retificador** Recebe tensões e correntes alternadas, transformando em tensões e correntes contínuas.

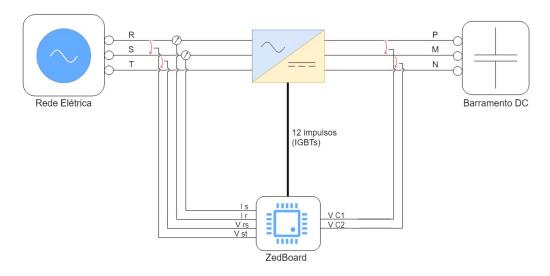

Figura 2.1 Esquema de um sistema de conversão de energia elétrica.

- **DC-AC ou Inversor** Inversamente ao que acontece no retificador, o inversor converte tensões contínuas em tensões alternadas.

- **DC-DC** Permite a alteração dos níveis de tensão entre os dois pontos do conversor, de forma a permitir a interligação de sistemas com diferentes tensões DC.

- **AC-AC** Modifica os níveis de tensão alternada, possibilitando a ligação entre dois sistemas de tensões diferentes.

Na zona azul, da figura 2.1 está situada a placa de controlo, ou plataforma digital, onde o algoritmo é executado. O algoritmo de controlo envia os sinais para o conversor de eletrónica de potência em função dos parâmetros impostos no controlo. Usualmente é necessário ajustar os sinais da placa de controlo, denominado de condicionamento de sinal, pois os sinais recebidos pela eletrónica de potência têm valores de tensão superiores. Para que tudo isto se torne possível são necessárias medidas provenientes dos sensores.

Na parte de medidas, representada a verde, os sensores efetuam as medições de corrente e tensão, permitindo que a placa de controlo atue corretamente no conversor de potência em função do algoritmo de controlo. O condicionamento de sinal é necessário uma vez que os valores de tensão e corrente adquiridos pelos sensores podem ser diferentes dos valores aceites pela placa de controlo, pelo que têm de ser ajustados para valores compatíveis com os ADC da plataforma de controlo.

Durante a dissertação, apenas se atuará na plataforma de controlo, desenvolvendo uma solução baseada na Zedboard, sendo que a sua escolha será justificada no ponto 2.2.3. Esta unidade de controlo deve ser compatível com o *Matlab/Simulink* e tem como principal objetivo a substituição de placas de desenvolvimento como a ds1103, *MicroLabBox* da *dSPACE* e a TMS320 da *Texas Instruments*. As soluções da *dSpace* são multi propósitos pelo que contêm capacidades superiores

às necessárias, nomeadamente a existência de ADC e entradas e saídas digitais superiores às utilizadas,o que faz aumentar o seu custo. Estas soluções apresentam,como desvantagens para o seu uso em protótipos, elevado custo e elevada dimensão, o que dificulta a sua utilização em sistemas compactos. Já a solução da *Texas*, tem pequenas dimensões a um baixo custo, contudo esta plataforma carece de velocidade de processamento e um maior número de entradas e saídas. Posto isto, a solução a desenvolver deve conter as vantagens das diferentes soluções apresentadas. Isto é, ter um custo reduzido, e pequenas dimensões, sem comprometer excessivamente a capacidade de processamento.

#### 2.1.1 Conversores de Eletrónica de Potência

Com o avanço da tecnologia e o aumento da automatização de processos, houve necessidade de controlo nos equipamentos eletrónicos, o que proporcionou o crescimento dos conversores de potência no mercado.

Os conversores de potência podem ser de vários tipos, com tensões de entrada e de saída alternada ou contínua. Devido a esta flexibilidade, os conversores de potência são utilizados nas mais diversas áreas desde controlo de motores, processos fabris automatizados, sistemas de armazenamento de energia, compensadores de energia reativa ou até mesmo nos computadores e eletrónica de consumo.

#### 2.1.1.1 Conversores Multinível

Os conversores multinível são um dos maiores avanços na eletrónica de potência da última década. Estes conversores apresentam várias vantagens (em relação aos conversores convencionais ou de dois níveis) sendo que, a principal, é a possibilidade da tensão à saída do conversor poder apresentar um maior número de valores distintos (mais de 2 diferentes). Com este aumento do número de níveis é possível melhorar as formas de onda da tensão, aproximando-as a uma sinusóide, e com isto reduzir a distorção harmónica produzida pelos conversores [1]. Outra das vantagens destes conversores é a redução da tensão a que cada semicondutor está sujeito (no caso de um um conversor de três níveis os semicondutores estão sujeitos a metade da tensão dos semicondutores de um conversor de dois níveis, quando ligados ao mesmo barramento DC). Esta redução da tensão a que os semicondutores estão sujeitos permite a utilização de conversores em níveis de tensão mais elevados (por ex. média tensão). A principal desvantagem destes sistemas é a necessidade de um maior número de semicondutores que incrementa a complexidade do sistema elétrico e do sistema de controlo. O aumento da complexidade no algoritmo de controlo, faz com que este tipo de conversor necessite de uma elevada velocidade de processamento.

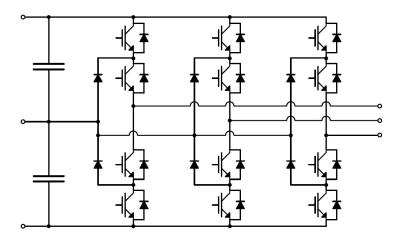

Existem várias tipologias para os conversores multiníveis como é o caso da: *neutral point clamped* (NPC), *cascaded H-bridge* (CHB) e *flying capacitors* (FCs) [2]. Todas as soluções referidas têm o mesmo propósito, o aumento dos níveis de tensão intermédios, sendo que a solução NPC, apresentada na figura 2.2, é a mais frequente.

Figura 2.2 Esquema de um inversor NPC de 3 níveis.

O uso de uma montagem NPC permite a redução do número de condensadores necessários. Contudo, esta solução apresenta dificuldades no equilíbrio da tensão dos condensadores do barramento DC. Este problema é um dos desafios dos algoritmos de controlo quando aplicados em conversores multinível do tipo NPC.

#### 2.1.2 Estratégias de Controlo

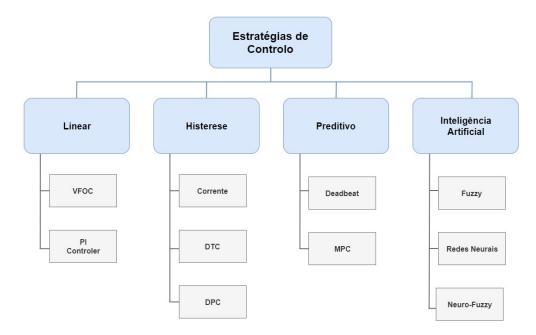

O controlo de conversores de potência pode ser efetuado de inúmeras formas distintas, sendo algumas delas muito precisas, mas com necessidades de processamento elevadas face à complexidade do seu algoritmo de cálculo. Posto isto, o controlo ideal varia de situação para situação consoante a precisão necessária, limitações da localização do equipamento, e dimensões pretendidas.

Face à evolução da indústria, são desenvolvidas novas estratégias de controlo sendo que os métodos mais comuns são apresentados na figura 2.3.

O controlo linear é um dos métodos mais frequentes do mercado, nomeadamente, o controlo FOC que orienta constantemente o vector do fluxo do motor. Existem outras estratégias lineares que atuam através da diferença entre o valor teórico da situação existente e o valor do sistema adquirido através dos sensores instalados [3, 4].

De forma distinta dos controladores lineares que atuam a uma frequência fixa, o controlo por histerese atua sempre que os valores saem dos limites pretendidos, o que faz com que este controlo não imponha nos semicondutores uma comutação de frequência constante. Os problemas destas oscilações de frequência é que as perdas de comutação deixam de ser previsíveis, pois variam com a frequência, e podem ainda ocorrer comutações em frequências que aumentam o desgaste dos semicondutores [3, 5].

Ainda existem técnicas de controlo preditivo, que como o próprio nome indica consistem num método que prevê o comportamento das variáveis do sistema. Para isso, o controlador calcula o comportamento do sistema para todos os estados de comutação possíveis, escolhendo o que produz o resultado mais próximo do desejado [6, 4].

Figura 2.3 Algumas das estratégias de controlo mais comuns.

Os métodos Fuzzy e Neuro-Fuzzy surgiram devido à aplicação de conceitos de inteligência artificial aos algoritmos de controlo. Ambos os métodos consistem na lógica difusa que ao invés de utilizar um lógica binária com dois valores, utiliza valores intermédios [7].

### 2.2 Plataformas de Controlo

Relativamente às plataformas digitais, atualmente existem no mercado várias soluções de controlo, embora a maioria das soluções multipropósito sejam bastante caras. O facto de estas soluções abrangerem a utilização numa grande variedade de sistemas faz com contenham funcionalidades que acabam por ser desnecessárias para sistemas simples. Com isto, é necessário que unidades de investigação e pequenas empresas tenham de optar por plataformas de prototipagem rápida, que são caras, ou então optar por soluções simples e baratas que abdicam da capacidade de processamento ou da programação rápida e simples.

O projeto na qual esta dissertação se insere, consiste no desenvolvimento de um protótipo de uma UPS, onde é necessário o uso de uma plataforma compacta, com uma capacidade de processamento elevada e compatibilidade com o programa *Simulink*. Das soluções utilizadas pelo grupo, nomeadamente as *DS1103*, Autobox e LabBox da *dSPACE*, a TMS320 da *Texas* e a *Compact Rio* e *SingleBoard Rio* da *National Instruments*, nenhuma preenchia as necessidades referidas. A plataforma *SB Rio* é a mais próxima da solução pretendida, contudo apenas pode ser programada através de *software* proprietário (*LabView*) da empresa que desenvolve o *Hardware*, o que implicava a conversão do sistema de controlo já desenvolvido no *Simulink* e a necessidade da compra da licença do *LabView*.

No caso das soluções sem compatibilidade com o *Simulink*, como é o caso da *SB Rio*, é sempre necessário adaptar o algoritmo de controlo desenvolvido. desta forma o código desenvolvido no *Simulink* que permitem a simulação e a verificação do funcionamento do algoritmo desenvolvido, tem de ser convertido para C (*LabView* no caso da *SB Rio*) e seguidamente implementado na plataforma de controlo. Em situações onde a plataforma de controlo contém uma FPGA para aumento do desempenho, é necessário transcrever o código para linguagem HDL (VHDL ou Verilog), que é uma linguagem complexa. Outras agravantes deste tipo de soluções é o tempo necessário para transcrição do código para C (ou HDL no caso de FPGAs) e a possibilidade de aparecimento de erros devido à transcrição do código.

Deste modo procurou-se desenvolver uma plataforma que satisfaça as necessidades do projeto, ou seja, uma plataforma compacta, económica com alta capacidade de processamento que permitisse a programação pelo *Simulink*

### 2.2.1 Programação pelo Simulink

A programação pelo *Simulink* é uma mais valia, pois oferece a possibilidade de implementação do código utilizado em simulação em plataformas de controlo compatíveis com o *Matlab/Simulink*. Esta vantagem é notória em ambiente de investigação pois o a funcionalidade dos algoritmos desenvolvidos tem de ser sempre verificada em ambiente de simulação antes de se proceder à sua implementação. Uma outra vantagem é a implementação direta já que traz facilidade na programação das plataformas, pois não é necessário realizar a conversão do código. Esta conversão é um dos maiores problemas das plataformas sem compatibilidade com *Simulink* (ou outro programa que permita a implementação após a simulação do algoritmo).

Embora o uso do *Simulink* acrescente os custos do programa para possibilitar a configuração da plataforma, as vantagens do programa fez com que se optasse por uma plataforma com compatibilidade com o mesmo. Na prática, os custos do *Simulink* acabam por ser necessários, pois ao nível da investigação este programa é utilizado para desenvolvimento e validação do funcionamento do algoritmo em simulação.

#### 2.2.2 Escolha da Plataforma

Com base nos soluções referidas no ponto 2.2, procurou-se uma solução compacta, que tivesse compatibilidade com o *Simulink* e que fosse uma plataforma versátil, por forma a permitir uma maior possibilidade de expansão. Posto isto, as soluções mais apelativas para os sistema a desenvolver foram as placas Arduino, RasberryPi e a ZedBoard, apresentadas na tabela 2.1.

Na seleção das soluções teve-se o cuidado de verificar plataformas compatíveis com o *Matlab*, e com custos inferiores às soluções de mercado.

Devido à necessidade de executar o algoritmo a cada 100µs (valor típico), fez com que a escolha da primeira plataforma a ser eliminada recaísse sobre o *Arduino*. O *RasberryPi* não é desenvolvido para execução em tempo real, pelo que as entradas e saídas não seriam fáceis de

| Equipamento        | Programação | FPGA | Dimensões | Processameto  | Custos |

|--------------------|-------------|------|-----------|---------------|--------|

| ds1103             | Simulink    | Não  | Elevadas  | Muito elevado | €€€    |

| LabBox             | Simulink    | Sim  | Elevadas  | Muito elevado | €€€    |

| <b>TMS320</b>      | Simulink    | Não  | Reduzidas | Baixo         | €      |

| <b>Compact Rio</b> | LabView     | sim  | Médias    | Muito elevado | €€€    |

| SingleBorad Rio    | LabView     | Sim  | Reduzidas | Elevado       | €€     |

| ZedBoard           | Simulink    | Sim  | Reduzidas | Elevado       | €€     |

| RaspberyPi         | Simulink    | Não  | Reduzidas | Médio         | €      |

| Arduino            | Simulink    | Não  | Reduzidas | Baixo         | €      |

Tabela 2.1 Comparação entre Várias Soluções de Mercado e Placas de Controlo.

utilizar à frequência pretendida, ao contrário da ZedBoard que contém uma FPGA que permite a gestão de periféricos a tempo-real. Com esta vantagem da ZedBoard, seria fácil interligar os periféricos com uma temporização perfeita que não seria possível num processador.

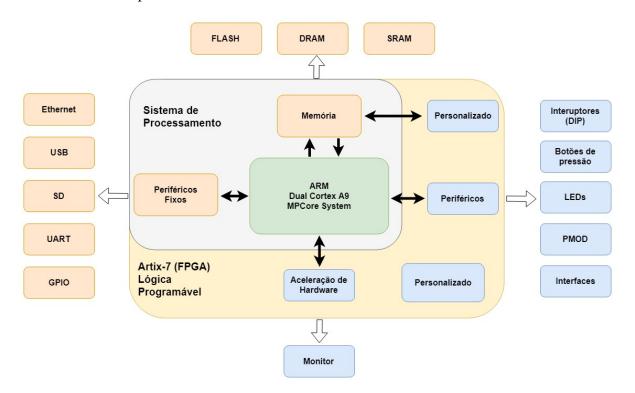

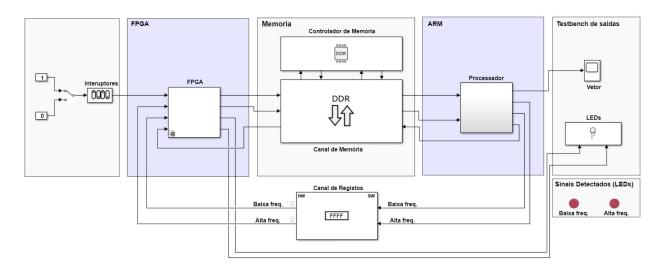

#### 2.2.3 ZedBoard

A ZedBoard da *Digilent* é baseada num *system on chip* (SoC) Zynq-7000 da *Xilinx* que é composto por um processador ARM A9 de 2 núcleos e uma FPGA Artix-7. Esta arquitetura (Zynq) é apresentada na figura 2.4, onde é possível verificar que há possibilidade de ligar vários periféricos a uma unidade de processamento, pelo que as mesmas têm de comunicar entre si para acederem a todos os recursos disponíveis.

Figura 2.4 Arquitetura de um SoC Zynq.

A comunicação entre processador e a FPGA é realizada pelo protocolo de comunicação AXI4 permitindo que haja troca de informação. Outro ponto é o facto de que embora o processador tenha acesso às entradas e saídas pré estipuladas (USB, Internet, Cartão SD), as entradas e saídas (I/O) digitais configuráveis, apenas podem ser acedidas pela FPGA. Nestes pinos I/O tem-se 30 pinos configuráveis distribuídos por 5 portas PMOD, 8 Leds, 8 interruptores e 7 botões de pressão. Visto esta plataforma não conter ADCs, as soluções são individuais e dependem de projeto para projeto, sendo fundamental a adição de ADCs, na quantidade necessária.

## 2.3 Sistemas UPS

Devido à dissertação estar inserida no projeto "DRIF" que tem como objetivo o controlo de UPS, a plataforma a desenvolver deve ser focada no controlo deste tipo de sistemas. A nível de desenvolvimento iniciou-se pelo uso de apenas 1 dos conversores dada a complexidade destes sistemas, sendo que após verificação do funcionamento da plataforma será possível implementar todo o sistema.

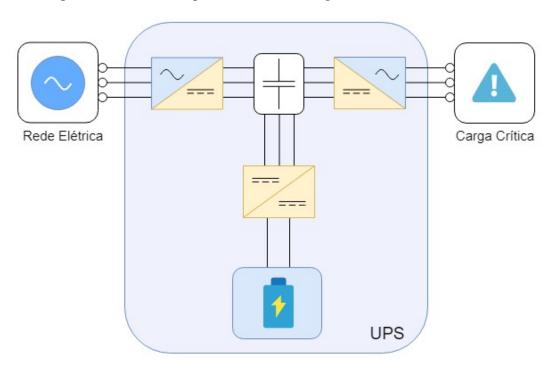

A figura 2.5 representa o esquema de um sistema UPS, que tem um papel importante no mundo atual. Com o aumento das necessidade dos consumidores, é necessário manter diversos sistemas em funcionamento com elevada qualidade de energia mesmo em casos de falha da rede de energia elétrica. Esta imunidade às falhas pode ser realizada com geradores de socorro ou através de sistemas UPS que utilizam baterias para alimentar as cargas críticas durante falhas da rede elétrica.

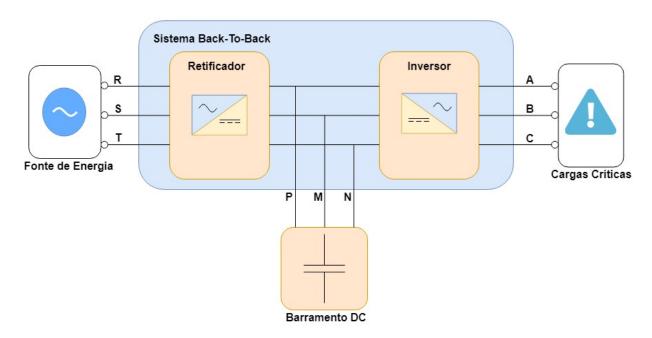

Figura 2.5 Modelo de um sistema UPS.

Os sistemas são compostos por 3 conversores interligados entre si pelo barramento DC (representado na figura 2.5 com um condensador). A UPS tem um retificador ativo que transforma a

energia AC da rede elétrica em DC. Existe ainda um conversor DC-DC que liga este barramento a um conjunto de baterias, responsável pelo ajuste da tensão do sistema de armazenamento de energia nas baterias. Por fim, existe o inversor que transfere a energia existente no barramento DC para as cargas críticas.

Na prática, o sistema absorve energia da rede suficiente para as cargas críticas e mantém as baterias carregadas. Em caso de falha da rede elétrica, o conversor DC-DC envia a energia armazenada nas baterias para o barramento DC. Quanto ao inversor, este mantém sempre o mesmo modo de funcionamento, garantindo que a carga crítica é continuamente alimentada por uma onda de tensão de elevada qualidade.

#### 2.3.1 Conversores Multinível nas UPS

A utilização de conversores multinível em sistemas UPS proporciona várias vantagens [8, 9], que permitem a melhoria da qualidade da energia através da redução da distorção harmónica quer na corrente absorvida da rede, quer nas ondas de tensão na carga. Os conversores multinível apresentam melhor qualidade de onda quando comparados a conversores tradicionais (2 níveis) equipados com filtros idênticos, devido à menor distorção harmónica dos mesmos. Deste modo, é possível reduzir significativamente os elementos de filtragem. Esta redução dos filtros permite uma diminuição do peso e volume da UPS (mais de 50% de acordo com [10]).

Os custos dos conversores multinível tornam-se superiores aos custos dos conversores de 2 níveis, devido ao maior número de semicondutores existentes. Contudo, a maior eficiência dos multiníveis, assim como um menor consumo de energia, faz com que sejam uma solução mais apelativa, tendo em conta a vida útil da UPS [11].

As vantagens enunciadas são aplicáveis quer ao retificador quer ao inversor. Nos sistemas UPS é adotada uma configuração *Back-to-Back*.

#### 2.3.2 Controlo Preditivo

Com o aumento de capacidade de processamento a nível de microprocessadores, DSPs (*digital signal processor*), e FPGAs (*field programmable gate array*), assim como a redução dos custos tornou o controlo preditivo cada vez mais apelativo. Dada a sua versatilidade na aplicação de sistemas de eletrónica de potência, o preditivo tem sido uma das escolhas mais atraentes e por isso muito utilizada para investigação[12–14].

O controlo preditivo a utilizar no sistema UPS do projeto onde a dissertação se insere é o controlo preditivo baseado em modelos de estados finitos. Esta técnica de controlo preditivo consiste na predição em cada período de amostragem do valor de variável a controlar para cada estado de comutação possível do conversor, escolhendo a mais favorável. Durante cada ciclo os valores das variáveis são calculados para todos os estados possíveis assim como a avaliação de uma função objetivo. O estado que minimiza o valor da função objetivo, e consequentemente minimiza o erro em relação às referências, é o estado aplicado ao conversor. A única grande desvantagem deste

método de controlo é a sua elevada carga computacional [15]. Hoje em dia, devido à evolução das unidades de processamento, é já possível utilizar este tipo de controlo em sistemas reais. Ainda assim, em sistemas complexos constituídos por conversores multinível, pode ser necessário utilizar frequências de amostragem menores, que têm um impacto direto no desempenho do sistema. Outra desvantagem deste método é a necessidade de um modelo matemático preciso, de forma a maximizar o desempenho do sistema, que variam a sua complexidade em função do sistema. Além do mais, caso não haja uma correta definição dos parâmetros ou caso estes variem ao longo do tempo faz com que ocorra uma redução no desempenho do sistema [16].

O sistema pode considerar uma única função objetivo g ou várias funções  $g_1, g_2, g_3, ..., g_n$ . Neste segundo caso a função objetivo acaba por ser uma combinação das várias funções

$$g = W_1g_1 + W_2g_2 + W_3g_3 + ... + W_ng_n$$

onde  $W_1, W_2, ..., W_n$  são os pesos de cada função objetivo, e definem qual a importância relativa de cada uma das funções. Nos pontos seguintes serão expostos os objetivos do retificador e do inversor do sistema UPS, que por sua vez são aplicados numa função objetivo. Esta será uma breve exposição das variáveis a considerar, sendo que não terá foco no modelo matemático (visto não ser objetivo do trabalho a desenvolver).

#### 2.3.3 Retificador Ativo

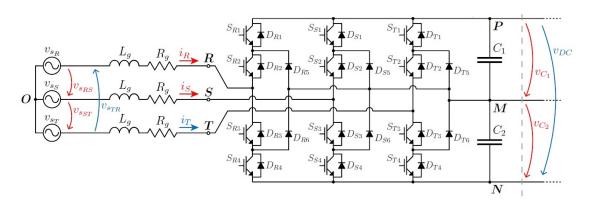

O retificador do sistema a utilizar, é um retificador trifásico de três níveis de tipologia NPC conforme está representado na figura 2.6. Os retificadores ativos têm como vantagens a redução da distorção harmónica e o aumento da eficácia quando comparados com os retificadores a díodos. A principal vantagem é a redução da distorção harmónica, sendo que o principal objetivo do sistema de controlo é garantir que a forma de onda da corrente do lado da rede é aproximadamente sinusoidal (com fator de potência unitário<sup>1</sup>), mantendo a tensão desejada no barramento DC.

Figura 2.6 Retificador trifásico multinível do tipo NPC.

<sup>&</sup>lt;sup>1</sup>Com exceção do caso de ser pretendido utilizar o Retificador para compensar o fator de potência

Ao aplicar o algoritmo de controlo ao retificador ativo é necessário efetuar 6 medições assinaladas a vermelho na figura 2.6. Na figura, são também apresentados dados a azul, que são necessários para a aplicação do algoritmo, contudo podem ser calculados posteriormente, minimizando os custos com sensores e ADC. Isto apenas é possível devido a ser utilizado um sistema trifásico sem neutro, pelo que a soma das correntes e tensões é sempre nula. Com a medição dos pontos do sistema identificados é possível o controlo preditivo calcular os 27 estados possíveis, que produzem 19 tensões distintas. Os estados resultam da combinação dos 3 estados possíveis de cada um dos braços do conversor (correspondente a uma fase). Os estados estão representados na tabela 2.2 sendo definidos como 1, 0 e -1, e onde o valor *x* corresponde à fase.

Tabela 2.2 Diferentes estados de cada braço do retificador.

| Estado | Condutor              | Tensão Fase-Ponto Médio    |

|--------|-----------------------|----------------------------|

| 1      | $S_{X_1}$ e $S_{X_2}$ | $vc_1 (\approx v_{DC}/2)$  |

| 0      | $S_{X_2}$ e $S_{X_3}$ | 0                          |

| -1     | $S_{X_3}$ e $S_{X_4}$ | $-vc_2(\approx -v_{DC}/2)$ |

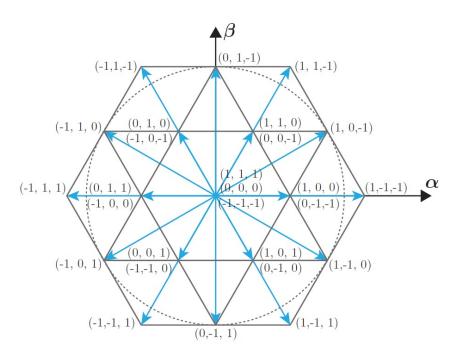

Das 3 possibilidades de cada braço surgem 27 estados de comutação( $3 \times 3 \times 3 = 27$ ). Contudo, alguns deles aplicam na saída o mesmo vector de tensão. Na figura 2.7, estão representado os 27 estados no plano  $\alpha\beta$ , onde apenas existem 19 vértices (19 estados distintos). Nesta figura é notória a redundância dos conversores NPC multinível, onde diferentes estados originam vectores de tensão iguais.

Figura 2.7 Diferentes vectores de tensão representados no plano  $\alpha\beta$ .

Após o cálculo dos valores esperados no sistema através do algoritmo em função do estado aplicado no retificador, é verificado qual o estado a aplicar consoante a função objetivo. No caso do retificador, a função objetivo tem como ideal os seguintes pressupostos:

- Minimizar o erro da corrente na rede;

- Minimizar o desequilíbrio de tensão entre os condensadores do barramento DC;

- Minimizar a frequência de comutação.

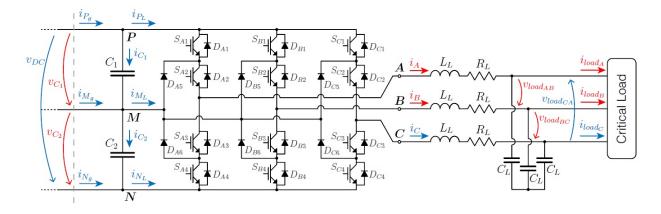

#### 2.3.4 Inversor

O inversor presente no sistema UPS a utilizar é um inversor trifásico de três níveis de tecnologia NPC, assim como o retificador. No caso dos inversores e retificadores multinível, estes têm a mesma estrutura física, pelo que o algoritmo de controlo que atua nos semicondutores permite que o conversor funcione como retificador ou inversor. Contudo, as medidas necessárias para cada um dos sistemas são conforme ilustrado na figura 2.8. As variáveis assinaladas a vermelho são medidas por sensores, pelo que as azul são calculados pelo algoritmo de controlo.

Figura 2.8 Inversor trifásico multinível do tipo NPC.

Assim como o retificador, o inversor NPC de 3 níveis também contem 27 estados, sendo que 19 deles são distintos. Como no caso anterior, o algoritmo de controlo a cada ciclo com base nos valores medidos permite o cálculo de diversos parâmetros. Seguidamente, com base na sua função objetivo verifica que estado minimiza o erro da função objetivo.

O inversor apresenta três objetivos principais:

- Minimizar o erro da tensão na carga;

- Minimizar o desequilíbrio de tensão entre os condensadores do barramento DC;

- Minimizar a frequência de comutação.

## 2.3.5 Requisitos do Sistema a Utilizar

O sistema a testar, já previamente desenvolvido, é composto por dois conversores numa montagem tipo *Back-to-Back*, projetado para utilização em sistemas UPS. O esquema do sistema previamente desenvolvido está presente na figura 2.9, sendo que ao longo dos testes ao sistema apenas será utilizado um conversor.

Figura 2.9 Sistema *Back-to-Back* a utilizar.

Esta utilização de apenas um conversor (retificador ou inversor) apenas é possível pois no sistema *Back-to-Back* todos os terminais estão acessíveis, embora estejam embutidos numa caixa. No caso do uso de apenas um conversor a funcionar como inversor ou retificador, é necessário ter em atenção para qual dos conversores são enviados os pulsos.

Para os testes com a plataforma de controlo a desenvolver optou-se por controlar apenas um dos conversores. Para aplicação do algoritmo de controlo, também já desenvolvido (no *Simulink*), é necessário que a ZedBoard possibilite a leitura dos sensores e envie os sinais de controlo necessários. As entradas e saídas necessárias estão representadas na tabela 2.3, sendo que é necessário deixar alguma margem nestas entradas e saídas de forma a possibilitar a adição de novos componentes.

Tabela 2.3 Entradas e saídas do algoritmo de controlo.

| Conversor   | Entradas              | Saídas                 |

|-------------|-----------------------|------------------------|

| Retificador | 6(ADCs)               | 12(Sinais de controlo) |

| Inversor    | 8(ADCs)               | 12(Sinais de controlo) |

| UPS         | 12(ADCs) <sup>2</sup> | 24(Sinais de controlo) |

<sup>&</sup>lt;sup>2</sup>Pois nesta situação os 2 ADC do barramento DC, são utilizados pelo retificador e pelo inversor.

#### Estado da Arte

Para o ideal funcionamento do sistema é importante ter em conta a funcionalidade das entradas e saídas como também é necessário que a plataforma a desenvolver consiga:

- Adquirir os valores das entradas analógicas em simultâneo;

- Atualizar os valores das saídas no instante em que adquire os dados.

Estas restrições são essenciais para o funcionamento do algoritmo, isto porque, caso os valores não sejam adquiridos simultaneamente, os valores de corrente e de tensão calculados deixam de ser precisos. O segundo ponto, é um requisito do controlo preditivo, de forma a maximizar a sua eficiência. Caso o segundo ponto não seja garantido, o sistema consegue funcionar, contudo a qualidade do algoritmo de controlo será severamente prejudicada.

# Capítulo 3

## Desenvolvimento da Plataforma

Conforme foi referido anteriormente, para o desenvolvimento da plataforma digital, é necessário o conhecimento do sistema a controlar de forma a saber as entradas e as saídas necessárias. No presente caso foi escolhido um retificador ativo, baseado num conversor NPC de 3 níveis, com um controlo preditivo. De forma a ser possível aplicar o controlo é necessário medir as 4 tensões e as 2 correntes assinaladas na figura 3.1.

Figura 3.1 Medidas a efetuar no sistema.

Embora a tensão entre as fases TR e corrente da fase T sejam necessárias, estas podem ser calculadas através dos resultados das restantes fases, pois num sistema trifásico sem neutro a soma das 3 tensões compostas e das 3 correntes é nula. Quanto às saídas, são necessários 12 impulsos de comando, um para cada IGBT do retificador NPC de 3 níveis. Posto isto, é necessário que sejam adicionados 6 ADC à ZedBoard de forma a poder efetuar as medições referidas, mantendo 12 saídas disponíveis para emitirem os impulsos para os IGBTs.

## 3.1 Escolha ADCs

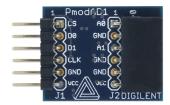

Para a escolha dos ADCs, procurou-se um módulo que fosse compatível com as entradas PMOD da ZedBoard para facilitar a ligação ao sistema. Desta forma, optou-se pelos módulos Pmod AD1 da *Digilent* compostos por 2 ADCs com 12 bits de resolução (valores entre 0 e 4095). O módulo tem 2 conectores conforme é possível verificar na figura 3.2, o conetor J1 liga à ZedBoard e no J2 são ligados os sinais externos (2 sinais a medir e alimentação(Facultativo)).

Figura 3.2 Pmod AD1 da Digilent.

Como o módulo é desenvolvido para ler sinais entre os 3,3V e 0V é possível ligá-lo diretamente à alimentação existente nas portas PMOD (no valor de 3,3V).

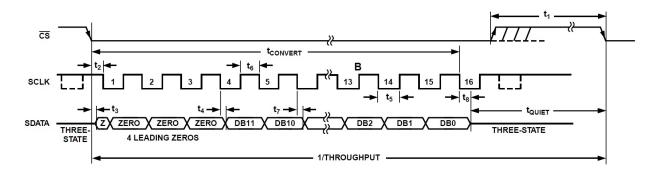

#### 3.1.1 Funcionamento Pmod AD1

O ADC recebe os sinais CS e CLK vindos da ZedBoard, sendo que o primeiro (CS) indica a frequência de aquisição do sinal e o segundo (CLK) a frequência da passagem de dados. Quando o sinal CS faz a transição descendente, o ADC adquire o valor. Após a transição descendente (1 -> 0) é enviado imediatamente o primeiro bit. Seguidamente, a cada transição descendente do sinal de CLK são enviados os 16 bits de dados. Enviados todos os bits, o sinal CS pode retornar a "1" conforme é apresentado na figura 3.3. Caso o sinal CS retorne ao 1 lógico durante a passagem de dados, esta é considerada inválida.

Figura 3.3 Funcionamento transferência de dados do Pmod AD1 da Digilent.

Embora o ADC seja de apenas 12 bits de resolução o sinal de dados tem o tamanho de 16 bits, isto porque, devido ao tempo de conversão do sinal os primeiros 4 bits são sempre 0. Quanto à velocidade máxima de aquisição de dados estipulada no *datasheet* é de 1MSPS, ou seja, uma amostra a cada 1µs. Para a velocidade de transferência de dados, é apresentada uma velocidade

máxima de 20MHz, ou seja 50ns, que nunca deve ser excedida. Após a passagem dos dados é necessário um tempo de repouso antes da conversão seguinte, representado na figura 3.1.1, como  $T_{Ouiet}$ , que deve ter no mínimo 50ns.

## 3.2 Configuração da Plataforma

Conhecidas as necessidades para a plataforma a desenvolver, nomeadamente a adição de 6 ADCs, a aquisição de dados simultânea e a atualização das saídas no mesmo instante que a aquisição de dados, passou-se à configuração da plataforma. Para a configuração da ZedBoard foram utilizados os programas *Simulink* e *Vivado*. De forma a facilitar a instalação e utilização dos programas em conjunto documentou-se um manual de instalação e utilização presentes nos apêndices A e B.

Durante a configuração dos ADCs, procurou-se garantir os vários parâmetros, nomeadamente, aquisição simultânea dos diversos ADCs, a atualização de saídas em simultâneo com os ADCs e verificar qual a frequência máxima para a transferência de dados.

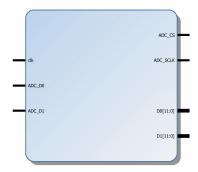

#### 3.2.1 Módulos dos Pmod AD1

Para a configuração dos módulos Pmod AD1 da *Digilent*, utilizou-se o programa *Vivado*, de forma a que as entradas dos ADCs fossem adicionadas à placa. O procedimento utilizado foi o descrito no manual de utilização, presente no apêndice B. Embora o desenvolvimento de código em VHDL para adição dos módulos à Zedboard seja complexo devido à linguagem utilizada, a existência de uma biblioteca da *Digilent* com um código VHDL já elaborado para os módulos a utilizar presente no apêndice C.1, facilitou esta tarefa.

Figura 3.4 Módulo Vivado Pmod AD1.

Quanto ao funcionamento dos módulo em VHDL, estes recebem um sinal de CLK que é convertido nos sinais SCLK e CS, sendo divisores inteiros do sinal de CLK. A frequência do sinal de SCLK é o resultado da divisão da frequência do sinal CLK pelo tamanho do vetor  $ce\_sr+1$ . Já o sinal CS tem uma frequência igual à divisão da frequência do SCLK pelo tamanho do vetor  $sequncer\_shift\_reg+1$ . Estes dois sinais têm cada um deles uma função específica no código fornecido pela Digilent, o  $sequncer\_shift\_reg$  é o número de bits enviados a cada interação e o  $ce\_sr$  é o número de bits para tempo de repouso do ADC. É de salientar que, o número de bits enviados a

cada interação contempla, os primeiros 4 bits a zero para espera da conversão do sinal, os 12 bits da conversão, os bits de tempo de repouso e por último bits inutilizados (estes bits embora não sejam utilizados são importantes para maximização da velocidade de transferência de dados sem alteração da frequência da aquisição como será demonstrado no ponto 3.2.4).

Após a adaptação dos módulos Pmod AD1 à ZedBoard no programa *Vivado* para os ADCs serem tratados como uma entrada da placa, foi criada uma *Board Definition*, conforme está explicado no apêndice B. Em seguida, foram realizadas as verificações de funcionamento do sistema.

## 3.2.2 Verificação da aquisição de dados em simultâneo

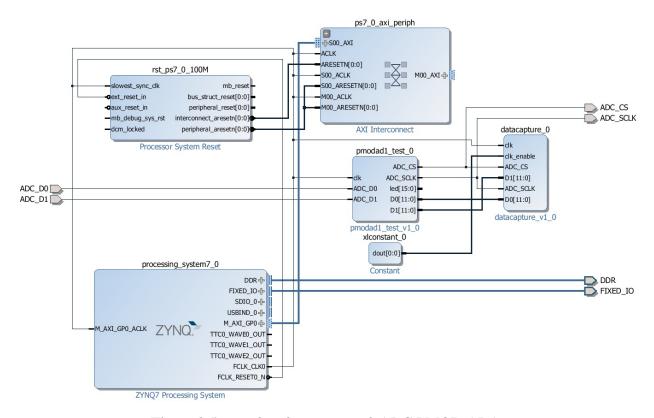

Para garantir que o sistema adquire os dados em simultâneo, desenvolveu-se uma configuração de placa (*Board Definition*), no programa *Vivado*, onde foram adicionados os blocos dos ADCs fornecidos pela biblioteca da *Digilent*. O esquema da figura 3.5 apresenta os ADCs e contém o bloco *datacapture* gerado pelo *Matlab* de forma a permitir o envio de dados da ZedBoard para o *Matlab/Simulink*.

Figura 3.5 Board Defenition para 2 ADC PMOD AD1.

O bloco *datacapture* é gerado através do comando *generateFPGADataCaptureIP* na linha de comandos do *Matlab*, e posteriormente anexado na *Board Definition* no *Vivado*. Este bloco tem como função a aquisição de diversos dados na FPGA num buffer, posteriormente enviando-os para o processador (ARM) permitindo exportar os dados para o *Simulink*. Após gerar o código *bitstream* do modelo da figura 3.5, este foi implementado na Zedboard. O algoritmo em questão efetua a

leitura de 2 ADCs em simultanêo e guarda os valores no bloco de *datacapture*. De forma a adquirir os dados, abre-se o modelo de *Simulink* e executar durante o tempo pretendido de forma a adquirir os valores guardados no bloco *datacapture ip*.

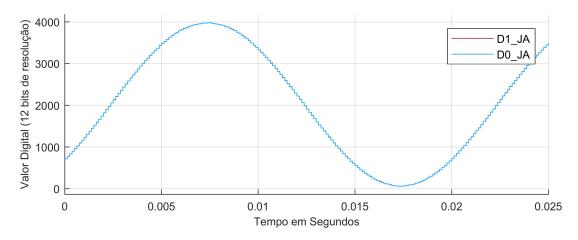

A figura 3.6 mostra os dados adquiridos ao longo do intervalo de tempo. No presente teste, o mesmo sinal foi ligado aos 2 ADCs, pelo que todas as leituras deveriam apresentar os mesmos valores.

Figura 3.6 Valores adquiridos pelos 2 ADCs de um módulo, com uma frequência de amostragem de 8kHz.

Conforme esperado, os sinais da figura 3.6 estão sobrepostos o que indica que os 2 ADCs, 2 presentes nos módulos Pmod AD1 da *Digilent*, adquiriram simultaneamente as amostras. Ao ampliar para uma análise mais fina, é notório algumas variações em torno de 2 bits, embora pouco notórias na figura 3.7. Estas variações são provocadas essencialmente por ruído e variações de conversão.

Figura 3.7 Ampliação dos valores adquiridos pelos 2 ADCs de um módulo, com uma frequência de amostragem de 8kHz.

Foi verificada a aquisição simultânea, que garante que os dados são adquiridos no mesmo instante, fundamental para o funcionamento correto do controlo preditivo a utilizar.

## 3.2.3 Aquisição de Dados e Atualização de Saídas em Simultâneo

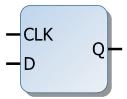

De forma a garantir que as saídas são atualizadas em simultâneo com a aquisição de dados, caraterizada pela transição descendente do sinal CS, desenvolveu-se o código em VHDL para esta função (presente no apêndice C.2). O código é um simples flip-flop (FF) do tipo D com ativação na transição descendente, ou seja, sempre que acontece uma transição descendente o sinal à entrada do FF é passado para a saída. Desenvolvido o código, o mesmo foi adicionado ao *Vivado*, obtendo o módulo da figura 3.8.

Figura 3.8 Módulo FF no Vivado.

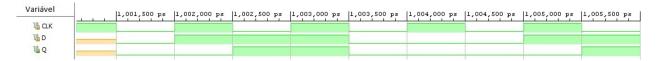

Após a adição do módulo ao *Vivado* foi possível realizar a simulação, representada na figura 3.9, onde foi verificado que o código VHDL funcionava como pretendido. Na figura estão representados os sinais de *Clock* (CLK), entrada (D) e saída(Q). Durante a simulação no *Vivado* colocou-se um sinal aleatório na entrada e sempre que o sinal de CLK efetuava a transição negativa, a saída atualizava o seu valor para o existente na entradas. Confirmado, que o sistema funcionava conforme pretendido prosseguiu-se para os testes práticos que confirmaram os resultados obtidos em simulação.

Figura 3.9 Simulação ao código VHDL do FF desenvolvido.

### 3.2.4 Velocidades de Transferência de Dados

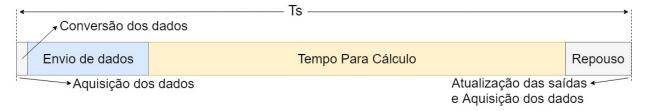

A velocidade de transferência de dados é um ponto muito importante de verificar, pois permite aos ADCs minimizar o tempo que demoram a disponibilizar os 12bits correspondentes ao valor de leitura. Neste ponto é importante maximizar a velocidade, sem afectar o funcionamento dos ADCs. A cada ciclo (Ts) é pretendido efetuar uma nova leitura, processamento de dados e atualização de valores no fim do ciclo, conforme está representado na figura 3.10, pelo que quanto menor o tempo de envio de dados maior o tempo para cálculo do algoritmo. Para a redução deste tempo é necessário aumentar a frequência do sinal de envio de dados (SCLK), mantendo a frequência de

aquisição de dados (CS), sendo que para isso é necessário aumentar o número de bits inutilizados referidos no ponto 3.2.1.

Figura 3.10 Esquema do envio de dados pelo Pmod AD1.

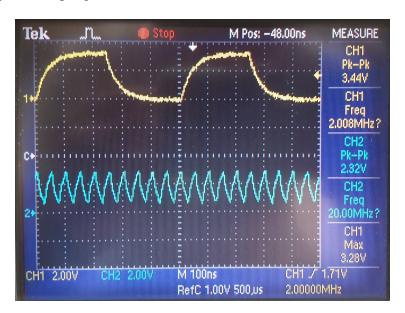

O incremento do vetor *sequncer\_shift\_reg* contribuiu para o aumento da diferença entre a frequência do SCLK e do CS. Após este incremento, verificou-se que o aumento da frequência reduzia o tempo de envio de dados. Contudo, ao atingir-se a gama dos 20 MHz (valor máximo apresentado no *datasheet* ) o ADC apresentou problemas na conversão de dados apresentando apenas 11 bits de resolução em vez dos 12 bits de resolução máxima. Embora fosse expectável que este problema ocorresse devido aos ADCs não terem tempo suficiente para conversão dos dados, verificou-se que o problema situava-se nas capacidades da FPGA. Após medição do sinal de SCLK à frequência de 20 MHz verificou-se que o mesmo não tinha tempo de estabilizar, devido às limitações de frequência das portas de saída da FPGA. Este problema é apresentado na figura 3.11 e devido à forma de onda a 20 MHz ser pouco confiável reduziu-se o sinal para 2 MHz de forma a obter uma onda quadrada que garanta o correto funcionamento dos ADCs.

Figura 3.11 Forma de onda do sinal SCLK a 2 MHz e a 20 MHz.

Este problema do sinal enviado pela ZedBoard é notório na figura 3.11, onde a onda amarela a 2 MHz apresenta alguma deformação, mas tem tempo de atingir os valores de pico (0 V e 3,3V). Já no caso da onda a 20 MHz representada a azul, isto já não acontece. Nesta situação a excursão do sinal é apenas 2,3 V quando deveria ser 3,3 V. Por este motivo, os ADCs não conseguem detetar

corretamente o sinal de *clock*, prejudicando o seu funcionamento. Devido a esta limitação da frequência de saída das portas PMOD da ZedBoard, optou-se por uma velocidade de transferência de dados a 2 MHz pois foi uma das maiores velocidades que permitiam o funcionamento estável dos ADCs.

Esta limitação que implica utilizar a frequência do sinal de SCLK a 2 MHz em vez dos 20 MHz (frequência máxima apresentada no *Datasheet*) faz com que o tempo que o ADC leve a disponibilizar os dados suba de  $0.8~\mu s$  para  $8~\mu s$ (situação com o SCLK a 2 MHz). De forma a minimizar o tempo de disponibilização dos dados, pode ser utilizado um oscilador externo de forma a reduzir o tempo para os  $0.8~\mu s$ .

## 3.2.5 Adição de ADC's ao IP CORE

Os IP Cores são blocos de construção utilizados em projetos para programação de FPGA. No presente caso, estes blocos são utilizados no *Vivado*, e uma vez desenvolvidos, podem ser reutilizados em diferentes projetos.

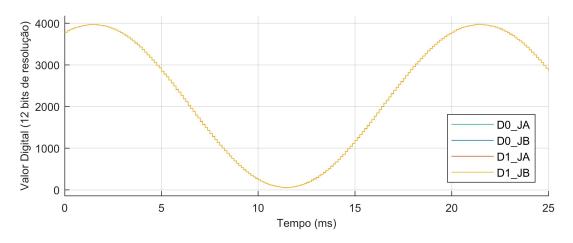

Para adicionar mais ADCs ao IP core fornecido pela *Digilent* alterou-se os parâmetros indicados no apêndice C.3 para o número de ADCs necessários. Os ADCs foram adicionados dois a dois (número de ADC existentes em cada módulo), sendo que todos partilhavam o mesmo sinal para transferência de dados e aquisição (sinal SCLK e CS). Depois da adição de um módulo repetiu-se o procedimento da alínea 3.2.2, adquirindo os dados presentes na figura 3.12. Como esperado foram obtidos sinais sobrepostos o que garante que todos os ADCs adquirem em simultâneo os valores independentemente do número de ADCs colocados.

Figura 3.12 Valor adquiridos pelos 4 ADC, a uma amostragem de 8kHz.

Confirmado que as alterações ao código VHDL não provocaram qualquer interferência no funcionamento do código, prosseguiu-se com a adição de ADCs para o número necessário. Na utilização de múltiplos ADCs, caso estejam ligados diretamente nas portas PMOD da ZedBoard é necessário que cada porta PMOD tenha o sinal de SCLK e CS do seu Pmod AD1 ligado à saída do módulo de ADC no *Vivado*.

# Capítulo 4

## Programação da Plataforma de Controlo

Conforme já explicado, a ZedBoard consiste apenas numa unidade de processamento, pelo que ao ser utilizada como uma unidade de controlo necessita de funções das quais não dispõe. Ao serem adicionados periféricos, a ZedBoard consegue ultrapassar estas limitações. Contudo, é necessário saber qual o projeto a realizar de forma a estipular quais e quantos componentes expansíveis serão necessários adicionar à ZedBoard. No ponto 2.3, já foi identificado o sistema a controlar e no capítulo anterior foram identificados os componentes periféricos necessários.

Neste capítulo, será explicada a importância das proteções e de que forma são aplicadas na ZedBoard, bem como as diferentes formas de processar o algoritmo de controlo. Estas diferentes formas de processar o algoritmo apresentam caraterísticas diferentes, sendo que cada uma delas tem as suas vantagens e, por isso, diferentes formas de aplicar o algoritmo, conforme será demonstrado ao longo deste capítulo.

## 4.1 Processamento do Algoritmo

Na ZedBoard, tal como em outros SoCs híbridos, o processamento de informação pode ser realizado de duas formas distintas, devido à existência de um processador (ARM) e de uma FPGA, sendo que cada uma delas tem as suas vantagens e desvantagens. A FPGA permite a execução do código num tempo de cálculo baixo, na ordem das dezenas a centenas de nanossegundos. As FPGAs têm como principal limitação a área programável limitada do dispositivo, o que faz com que algoritmos muito complexos não possam ser executados unicamente numa FPGA. Por outro lado, um processador consegue correr qualquer tipo de código independentemente da complexidade, sendo que o tempo de execução aumenta proporcionalmente.

Na estrutura da placa, apresentada no ponto 2.2.3, as entradas e saídas são sempre manipuladas pela FPGA, o que faz com que a gestão das mesmas seja mais rápida e permita uma temporização extremamente precisa dos eventos de leitura e escrita, assim como uma perfeita sincronização entre eles. Ao nível dos métodos de implementação estes podem ser divididos em:

#### Processamento apenas na FPGA

- Processamento apenas<sup>1</sup> no ARM

- · Processamento Híbrido

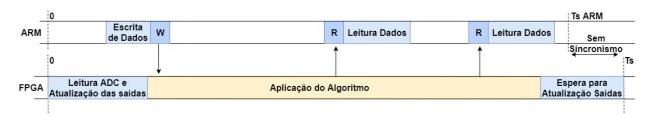

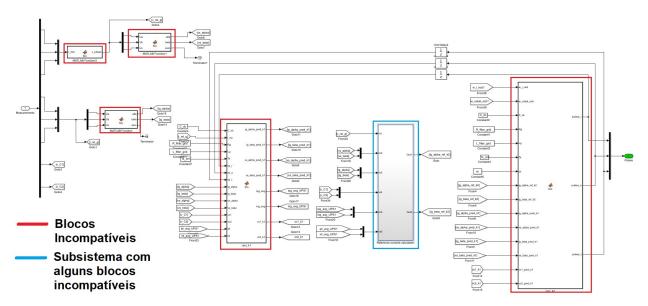

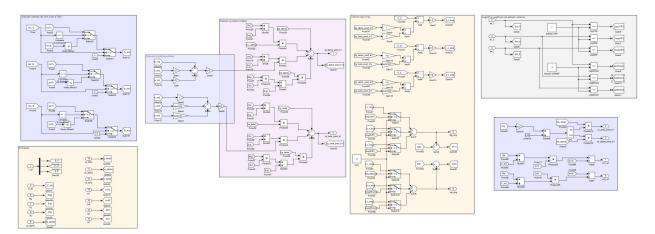

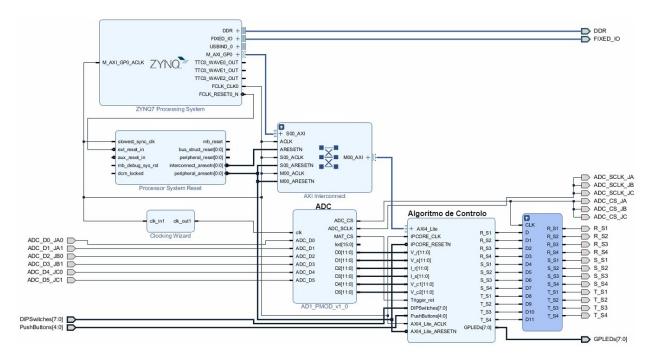

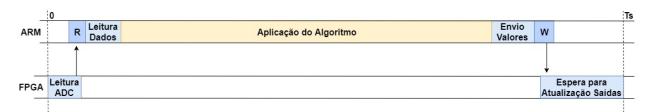

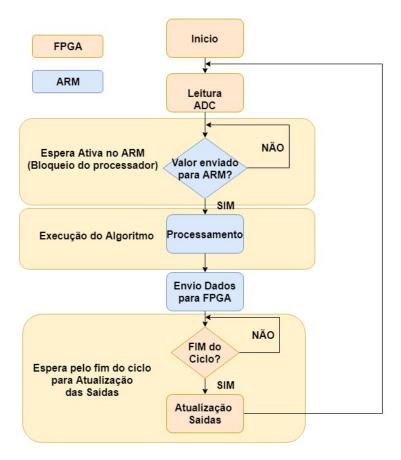

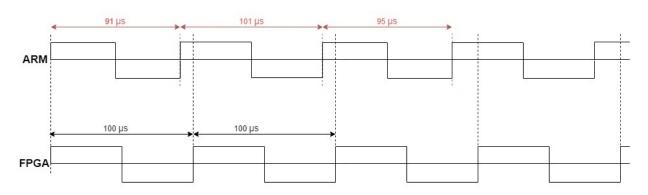

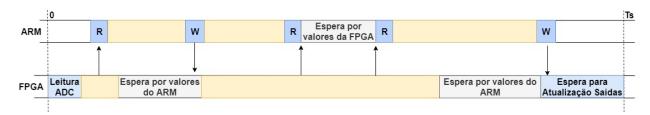

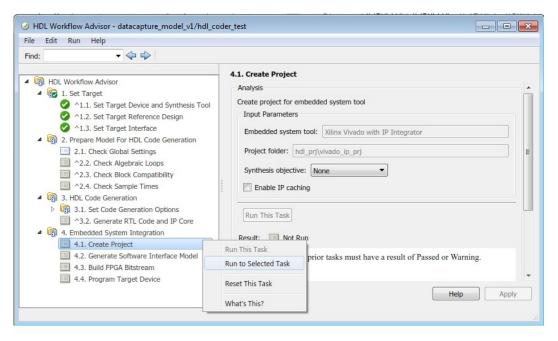

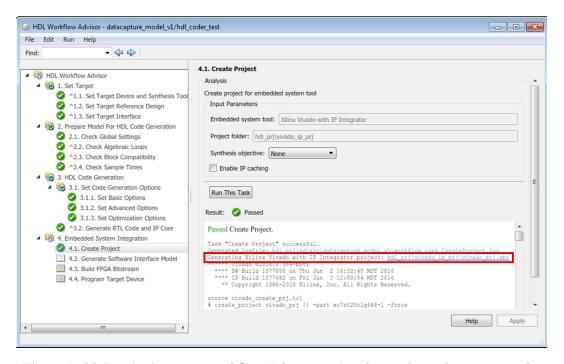

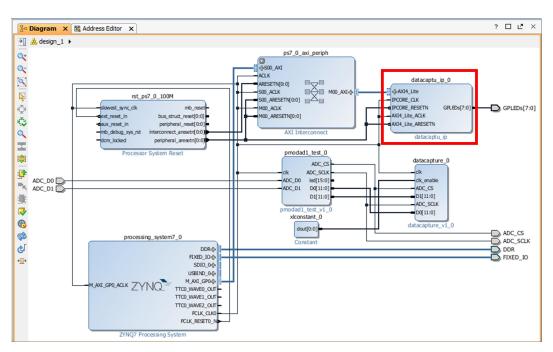

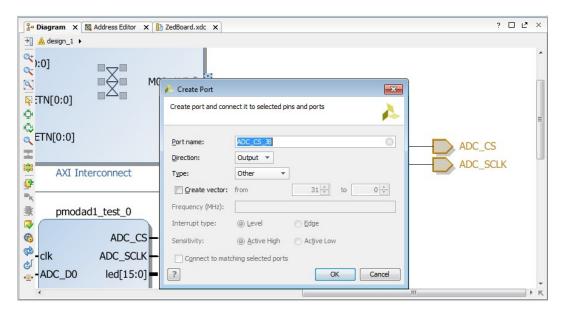

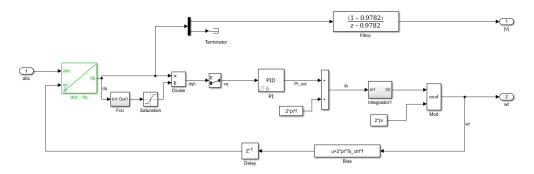

Ao longo do capítulo serão expostas as vantagens e desvantagens de cada uma destas formas de processamento, assim como as dificuldades de implementação de cada uma delas. Os programas utilizados para aplicação do algoritmo de controlo na plataforma são os *Add-Ons*: *Embedded Coder* e *HDL Coder* do *Simulink*. Estes *Add-Ons* interligam o modelo do *Simulink* ao *Vivado* que permite a sua implementação, quer no ARM quer na FPGA (duas unidades de processamento da ZedBoard).