Pedro Miguel Parola Duarte

## Application-specific Soft-GPGPU on Reconfigurable Substrates

Dissertação submetida para a satisfação parcial dos requisitos do grau de Mestre em Engenharia Electrotécnica e de Computadores

Julho de 2016

Universidade de Coimbra

Background of cover image source: FPGA implementation of a MicroBlaze (in orange) and one Compute Unit (NEKO) (in blue).

## UNIVERSIDADE DE COIMBRA FACULDADE DE CIÊNCIAS E TECNOLOGIA departamento de engenharia electrotécnica e de computadores

## Application-specific Soft-GPGPU on Reconfigurable Substrates

Pedro Miguel Parola Duarte

## Dissertação para a obtenção do Grau de Mestre em **Engenharia Electrotécnica e de Computadores**

Júri

Presidente: Doutor Vitor Manuel Mendes da Silva Vogal: Doutor Jorge Nuno de Almeida e Sousa Almada Lobo

## Orientadores

Orientador: Doutor Gabriel Falcão Paiva Fernandes Co-orientador: Doutor Pedro Filipe Zeferino Tomás

Coimbra

Julho 2016

Pedro Miguel Parola Duarte: *Application-specific Soft-GPGPU on Reconfigurable Substrates,* Tese de Mestrado em Engenharia Electrotécnica e de Computadores, ramo de especialização em Computadores, Faculdade de Ciências e Tecnologia, Universidade de Coimbra © Julho 2016

## Acknowledgments

Aos meus orientadores, Professor Gabriel Falcão e Professor Pedro Tomás, tenho a agradecer toda a ajuda, sugestões e apoio, sem as quais não teria conseguido realizar este trabalho. Sem o apoio do Professor Gabriel certamente teria desistido, mas passo a passo, com pequenos avanços que muitas vezes não pareciam ajudar, conseguimos atingir o que nos tínhamos proposto a fazer. Mais ainda tenho a agradecer-lhe as perspetivas de futuro e todas as portas que me abriu ou deixou abertas. Também o Professor Pedro com as suas sugestões certeiras que sempre ajudaram a dar o passo em frente e sem as quais nunca se teriam atingido todos os objectivos propostos.

Agradeço ao Doutor João Andrade, por todas as tardes (dias) perdidas a dar-me apoio quando nada o obrigava a fazê-lo.

I thank Ziliang Guo, for all the help and support he provided to better understand MIAOW, without which I would still be in the system design stage. I would also like to thank Sam for the help provided in writing this thesis.

Ao Zé, ao Jamaro, ao Manuel, e todos os restantes colegas de laboratório, não só a ajuda que nunca me negaram, mas também todos os momentos de boa disposição (procrastinação) que proporcionaram.

Sem o apoio incondicional da minha família não seria possível ter chegado aqui. Aos meus Pais agradeço o permanente incentivo para aprender mais e maximizar o meu capital humano, bem como todo o apoio.

Por fim, o meu mais especial agradecimento, para a Diana, por todo o apoio, preocupação, e amor sem os quais teria enlouquecido provavelmente ainda antes de começar esta tese.

A todos, muito obrigado,

Bran thought about it. 'Can a man still be brave if he's afraid?' 'That is the only time a man can be brave,' his father told him.

- George R.R. Martin, A Game of Thrones

## Abstract

Driven by the increasing performance requirements of modern scientific applications, general-purpose computing on modern *graphics processing units* (GPUs) have recently become a common approach. However, although GPU's massively parallel architectures provide high flexibility and performance, off-the-shelf devices have fixed designs that cannot be adapted towards the specific characteristics of the target applications. On the other hand, application-specific architectures can be designed and implemented in reconfigurable fabric that can be easily tailored to maximize the performance of a given application. However, such approaches often require a profound architectural redesign at the presence of minimal algorithmic changes.

To overcome both issues, a new solution is herein proposed that relies on emerging implementations of general-purpose massively parallel and programmable architectures on reconfigurable fabric, often referred to as soft-*general-purpose GPUs* (GPGPUs). Hence, the proposed solution adopts the recently developed MIAOW implementation of the AMD Southern Islands architecture, which is herein extended in order to support a wide set of 154 instructions (up from 42 in the original design). Furthermore, to tackle important performance bottlenecks associated with the critical path and with the memory access latency, a set of architectural improvements were introduced, providing a speedup of up to 80x when implemented on a Xilinx Virtex 7 FPGA. Finally, a new compile-time methodology was proposed that, by trimming down the implemented resources, allows tailoring the soft-GPGPU architecture towards the application characteristics, leading up to 18% energy savings without any performance penalty.

## **Keywords**

Soft GPGPU, application-specific architecture, re-configurable computing, architectures, power-and energy-efficient computing, parallel processing, FPGA

## Resumo

Impulsionada pelas crescentes exigências de performance das aplicações científicas modernas, a computação de propósito geral (*general-purpose*) em *graphics processing units* (GPUs) tornou-se uma abordagem comum. No entanto, apesar da arquitetura massivamente paralela das GPUs fornecer alta flexibilidade e desempenho, o *design* do *hardware* em dispositivos comerciais é fixo, não podendo ser adaptado às características específicas de cada aplicação. Por outro lado, é possível conceber e implementar arquiteturas, específicas para uma dada aplicação, em tecidos reconfiguráveis. Estas, podem ser facilmente adaptadas para maximizar o desempenho de uma determinada aplicação. No entanto, estas abordagens frequentemente requerem um profundo redesenho arquitetónico na presença de alterações mínimas ao algoritmo.

Para superar ambas as questões, é aqui proposta uma nova solução que se baseia em implementações emergentes de arquiteturas general-purpose massivamente paralelas e programáveis em tecidos reconfiguráveis, muitas vezes apelidadas de soft-*generalpurpose GPU* (GPGPU). Assim, a solução proposta adota a implementação recentemente desenvolvida chamada 'MIAOW' e que é baseada na arquitetura da AMD Southern Islands. O soft-GPGPU é aqui ampliado a fim de apoiar um conjunto amplo de 154 instruções (de 42 no projeto original). Além disso, para resolver os *bottlenecks* de performance associados com o caminho crítico e com a latência de acesso à memória, um conjunto de melhorias de arquitetura foram introduzidas, proporcionando uma melhoria de até 80x na performance, quando implementada numa *field-programmable gate array* (FPGA) Xilinx Virtex 7. Finalmente, uma nova metodologia de tempo de compilação foi proposta que, por diminuir os recursos consumidos pela implementadação, permite a adaptação da arquitetura soft-GPGPU para as características de uma dada aplicação, levando a uma poupança de energia de até 18% sem qualquer perda de desempenho.

## **Palavras Chave**

GPGPU sintetizáveis, arquitectura aplicação específica, computação reconfigurável, arquiteturas, computação eficiente, processamento paralelo, FPGA

## Contents

## Page

| 1                                       | 1 Introduction                                         |                                               |  |  |  |  |

|-----------------------------------------|--------------------------------------------------------|-----------------------------------------------|--|--|--|--|

|                                         | 1.1                                                    | Motivation                                    |  |  |  |  |

|                                         | 1.2                                                    | Objectives                                    |  |  |  |  |

|                                         | 1.3                                                    | Main Contributions                            |  |  |  |  |

|                                         | 1.4                                                    | Outline                                       |  |  |  |  |

| 2                                       | Soft                                                   | -GPGPUs Overview 7                            |  |  |  |  |

|                                         | 2.1                                                    | FlexGrip 8                                    |  |  |  |  |

|                                         | 2.2                                                    | MIAOW 10                                      |  |  |  |  |

|                                         | 2.3                                                    | FGPU                                          |  |  |  |  |

|                                         | 2.4                                                    | Summary                                       |  |  |  |  |

| 3                                       | MIA                                                    | AOW Base Architecture 17                      |  |  |  |  |

|                                         | 3.1                                                    | Base Instruction Set Architecture 18          |  |  |  |  |

|                                         |                                                        | 3.1.1 Compute Unit Architecture               |  |  |  |  |

|                                         | 3.2                                                    | NEKO                                          |  |  |  |  |

|                                         | 3.3                                                    | FPGA Design                                   |  |  |  |  |

|                                         |                                                        | 3.3.1 Base system                             |  |  |  |  |

|                                         |                                                        | 3.3.2 Full system                             |  |  |  |  |

|                                         |                                                        | 3.3.3 Simulation system                       |  |  |  |  |

|                                         | 3.4                                                    | FPGA Validation 27                            |  |  |  |  |

|                                         | 3.5                                                    | Summary                                       |  |  |  |  |

| 4 Application-specific GPU Architecture |                                                        |                                               |  |  |  |  |

|                                         | 4.1 Enhancing functionality and throughput performance |                                               |  |  |  |  |

|                                         |                                                        | 4.1.1 Vector register direct access interface |  |  |  |  |

|                                         |                                                        | 4.1.2 Dual clock domain                       |  |  |  |  |

|                                         |                                                        | 4.1.3 Internal block RAM memory 33            |  |  |  |  |

|                                         | 4.2                                                    | System benchmark                              |  |  |  |  |

|                                         |                                                        | 4.2.1 Applications                            |  |  |  |  |

|                                         |                                                        | 4.2.2 Compute unit initialization             |  |  |  |  |

|                                         |                                                        | 4.2.3 Benchmarking procedures                 |  |  |  |  |

|                                         | 4.3                                                    | Application-Specific system development       |  |  |  |  |

|                                         | 4.4                                                    | Summary                                       |  |  |  |  |

#### Contents

| 5             | Experimental Results 4                       |                                                   |    |  |  |  |

|---------------|----------------------------------------------|---------------------------------------------------|----|--|--|--|

|               | 5.1 Synthesized Instruction Set Architecture |                                                   |    |  |  |  |

|               | 5.2                                          | Validation of dual-clock domain and BRAM usage    | 44 |  |  |  |

|               |                                              | 5.2.1 Benchmark results                           | 44 |  |  |  |

|               |                                              | 5.2.2 Area and power analysis                     | 47 |  |  |  |

|               | 5.3                                          | Application-specific area gains and power savings | 49 |  |  |  |

|               |                                              | 5.3.1 Power savings                               | 49 |  |  |  |

|               |                                              | 5.3.2 Area gains                                  | 52 |  |  |  |

|               | 5.4                                          | Summary                                           | 54 |  |  |  |

| 6 Conclusions |                                              |                                                   | 55 |  |  |  |

|               | 6.1                                          | Future work                                       | 57 |  |  |  |

| A             | Plots of benchmark results                   |                                                   |    |  |  |  |

| B             | Energy consumption results                   |                                                   |    |  |  |  |

| C             | Scalar Instruction Testing                   |                                                   |    |  |  |  |

| D             | OVector Instruction Testing10                |                                                   |    |  |  |  |

| E             | Memory Instruction Testing 1                 |                                                   |    |  |  |  |

# **List of Figures**

| <ol> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> </ol> | FlexGrip Streaming Multiprocessor's pipeline                                                                                                | 9<br>11<br>11<br>13<br>15 |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 3.1<br>3.2                                                                  | Base FPGA system       Simplified FPGA system                                                                                               | 25<br>27                  |

| 4.1<br>4.2<br>4.3<br>4.4                                                    | Simplified scheme of the improved FPGA systemOpenCL Code ExampleAMD CodeXL AssemblyAMD CodeXL Pre-Initialized Registers                     | 34<br>36<br>37<br>38      |

| 5.1<br>5.2                                                                  | Power requirements for the original and the two clock domain systems<br>Power requirements for the system with two clock domains and a BRAM | 48                        |

|                                                                             | module                                                                                                                                      | 49                        |

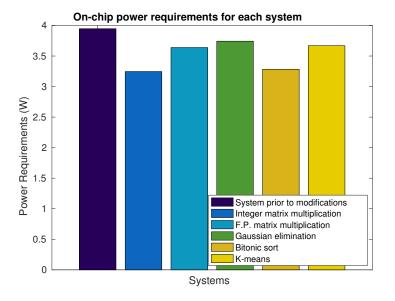

| 5.3                                                                         | Total on-chip power per system                                                                                                              | 50                        |

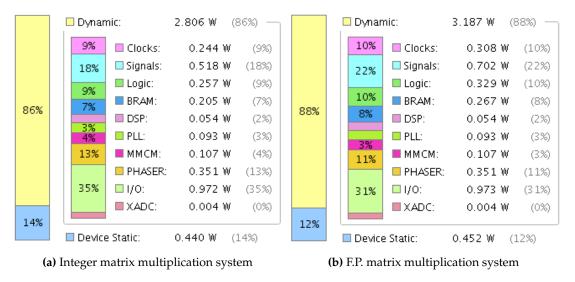

| 5.4                                                                         | Power requirements for the matrix multiplication systems                                                                                    | 50                        |

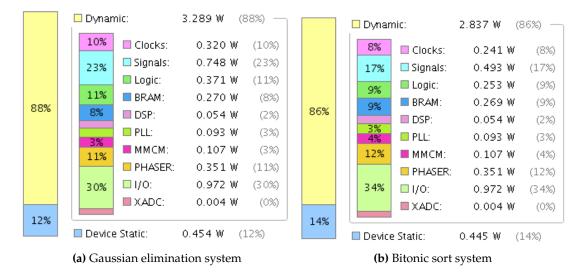

| 5.5                                                                         | Power requirements for the Gassian elimination and bitonic sort systems .                                                                   | 51                        |

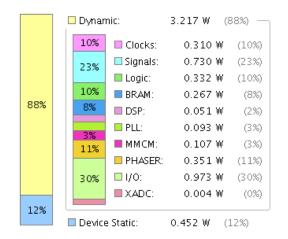

| 5.6                                                                         | Power requirements for the K-means clustering system                                                                                        | 51                        |

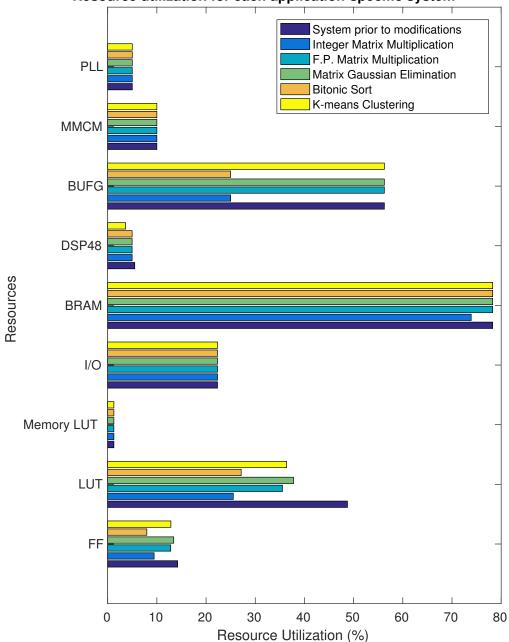

| 5.7                                                                         | Comparison in resource utilization between the system prior to the archi-                                                                   |                           |

|                                                                             | tectural trim-down and all the application-specific systems                                                                                 | 53                        |

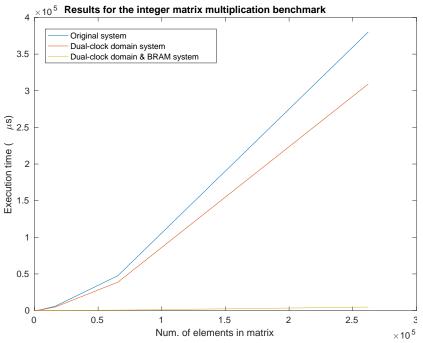

| A.1                                                                         | Integer matrix multiplication results                                                                                                       | 64                        |

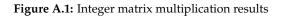

| A.2                                                                         | Floating-point matrix multiplication results                                                                                                | 64                        |

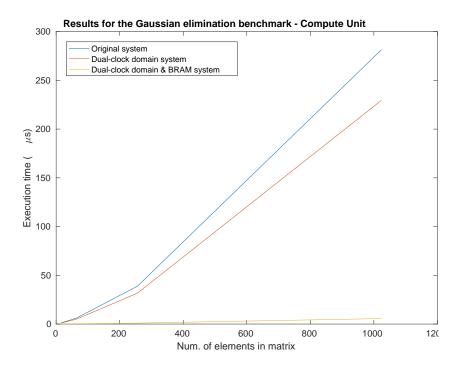

| A.3                                                                         | Matrix Gaussian elimination results - Compute Unit (CU)                                                                                     | 65                        |

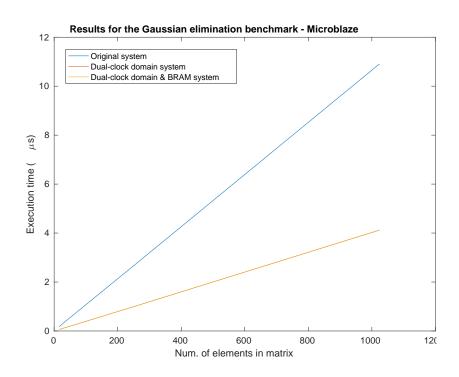

| A.4                                                                         | Matrix Gaussian elimination results - Microblaze                                                                                            | 65                        |

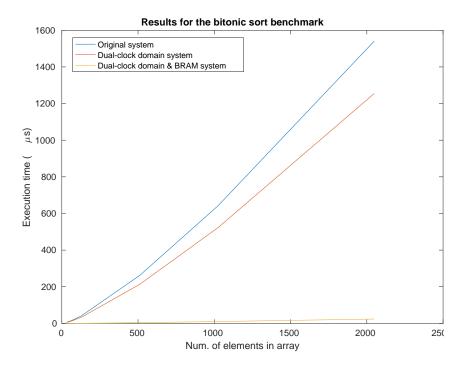

| A.5                                                                         | Bitonic sort results                                                                                                                        | 66                        |

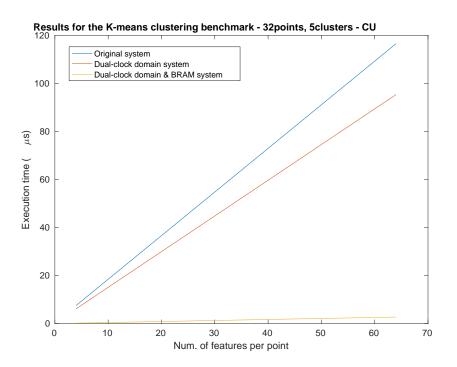

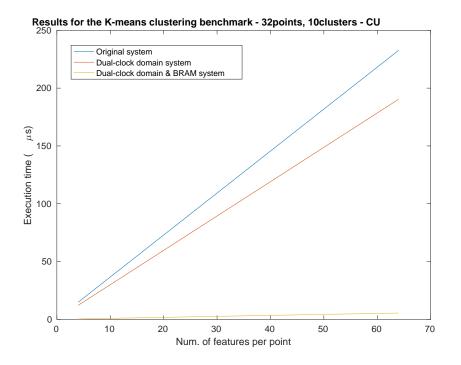

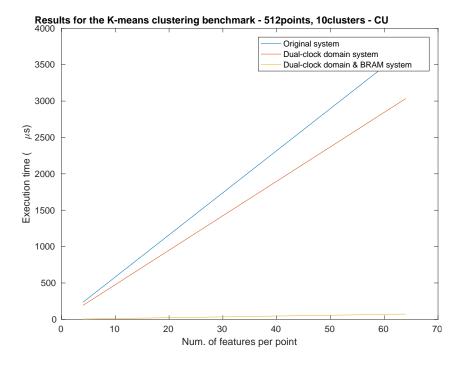

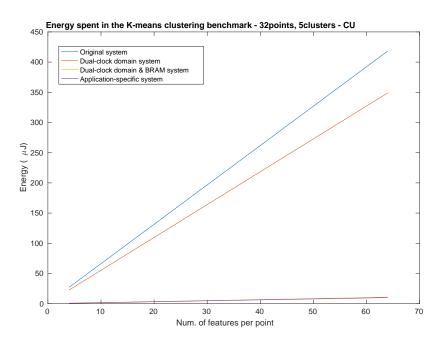

| A.6                                                                         | K-means clustering benchmark results - 32points, 5clusters - CU                                                                             | 66                        |

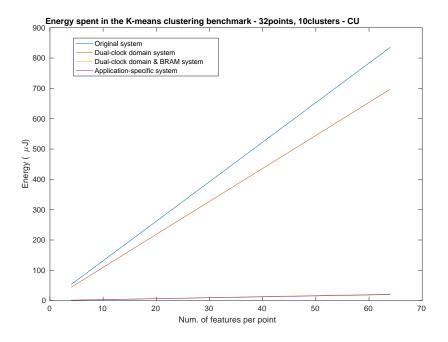

| A.7                                                                         | K-means clustering benchmark results - 32points, 10clusters - CU                                                                            | 67                        |

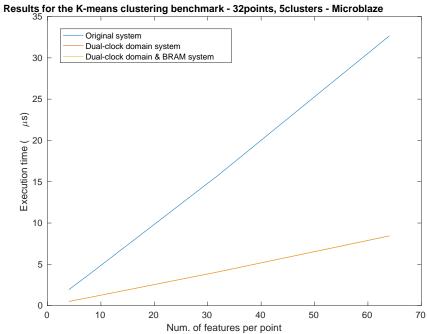

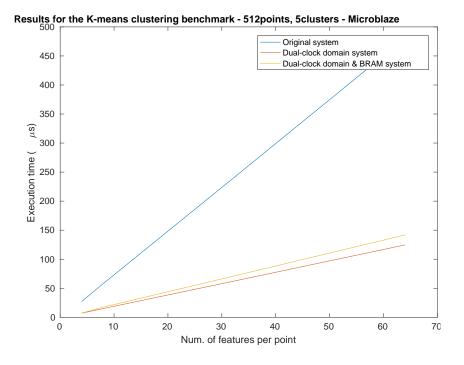

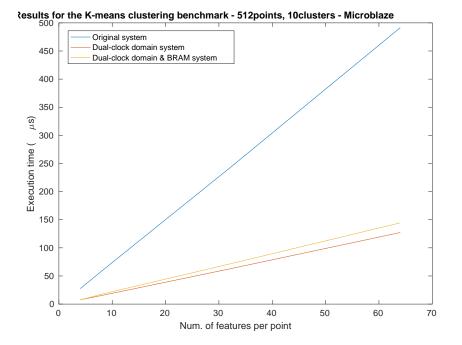

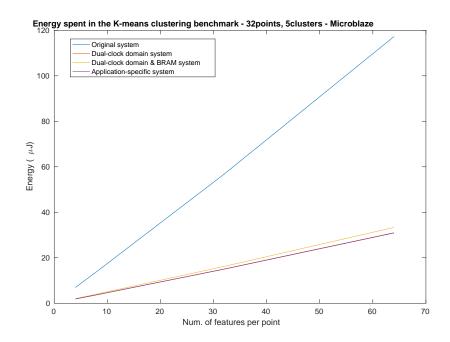

| A.8                                                                         | K-means clustering benchmark results - 32points, 5clusters - Microblaze .                                                                   | 67                        |

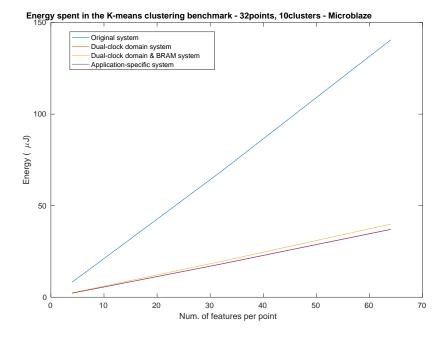

| A.9                                                                         | K-means clustering benchmark results - 32points, 10clusters - Microblaze                                                                    | 68                        |

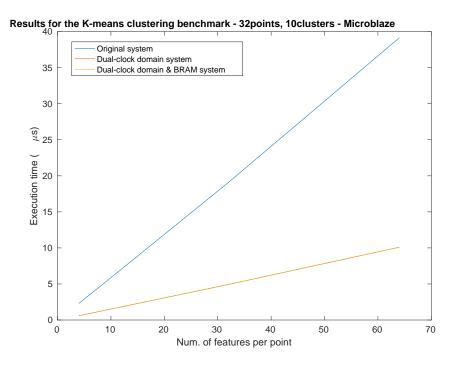

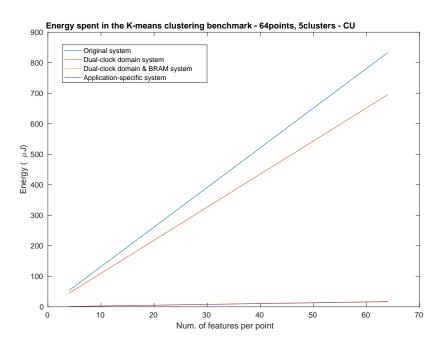

| A.10                                                                        | K-means clustering benchmark results - 64points, 5clusters - CU                                                                             | 68                        |

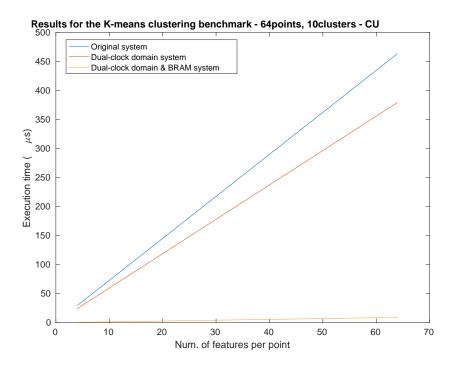

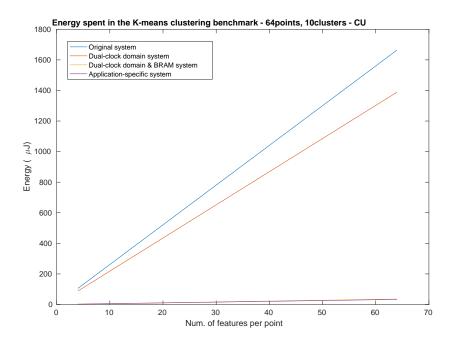

| A.11                                                                        | K-means clustering benchmark results - 64points, 10clusters - CU                                                                            | 69                        |

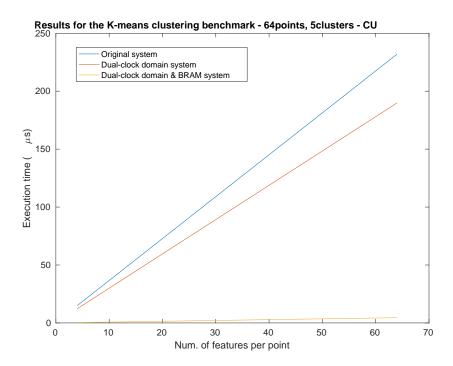

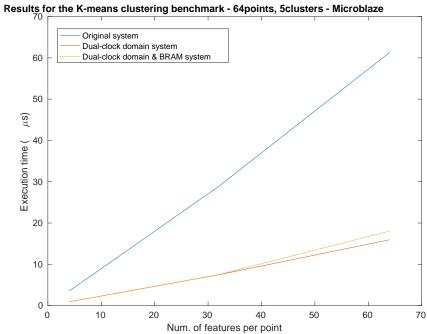

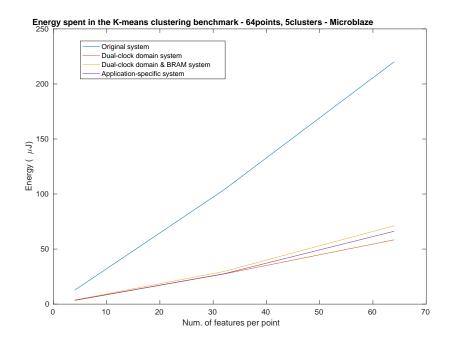

| A.12                                                                        | K-means clustering benchmark results - 64points, 5clusters - Microblaze .                                                                   | 69                        |

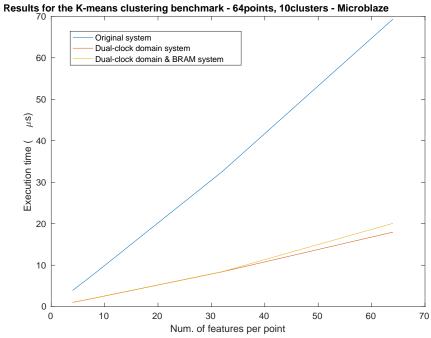

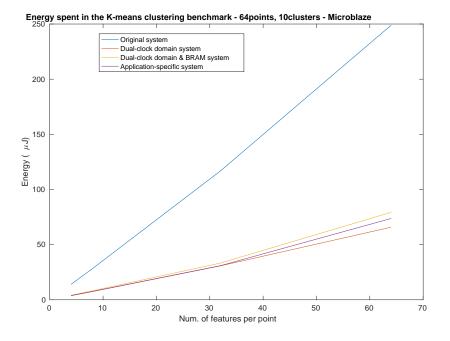

| A.13                                                                        | K-means clustering benchmark results - 64points, 10clusters - Microblaze                                                                    | 70                        |

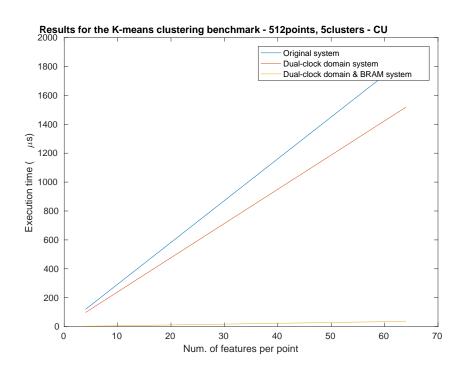

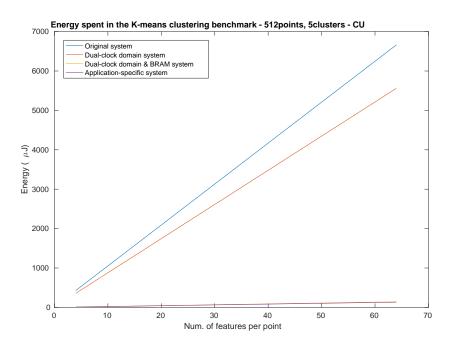

| A.14                                                                        | K-means clustering benchmark results - 512points, 5clusters - CU                                                                            | 70                        |

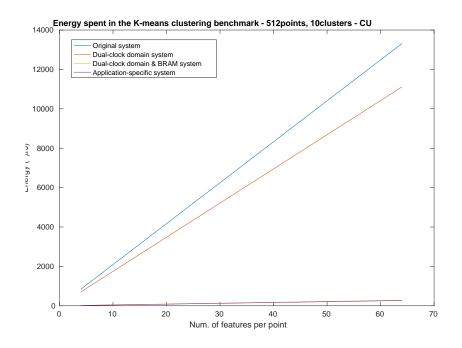

| A.15                                                                        | K-means clustering benchmark results - 512points, 10clusters - CU                                                                           | 71                        |

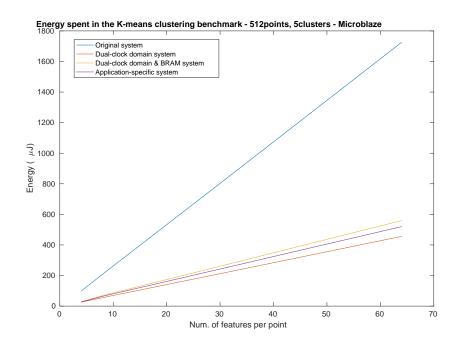

| A.16  | K-means clustering benchmark results - 512points, 5clusters - Microblaze  | 71       |

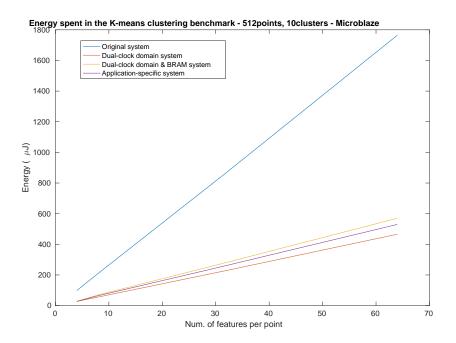

|-------|---------------------------------------------------------------------------|----------|

| A.17  | K-means clustering benchmark results - 512points, 10clusters - Microblaze | 72       |

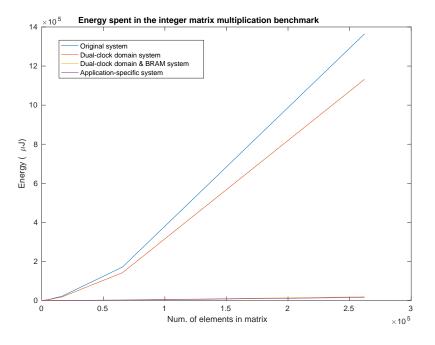

| B.1   | Energy spent in the integer matrix multiplication benchmark               | 74       |

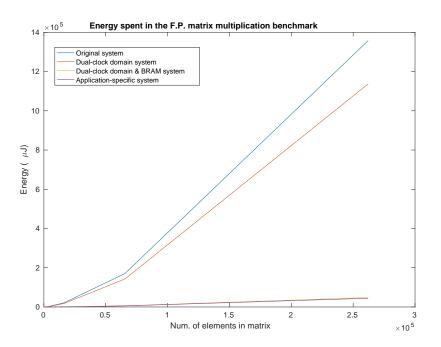

| B.2   | Energy spent in the floating-point matrix multiplication benchmark        | 74       |

| B.3   | Energy spent in the Gaussian elimination benchmark - Compute Unit (CU)    | 75       |

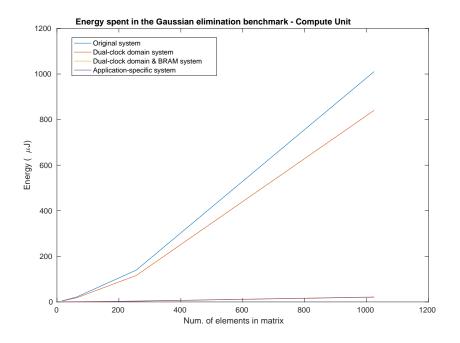

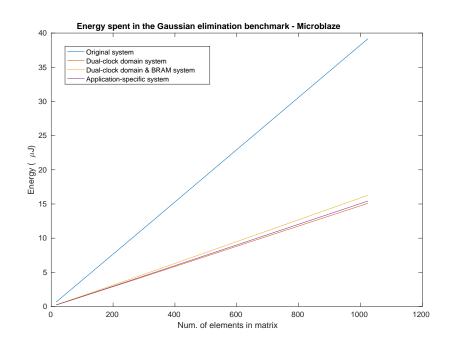

| B.4   | Energy spent in the Gaussian elimination benchmark                        | 75       |

| B.5   | Energy spent in the bitonic sort benchmark                                | 76       |

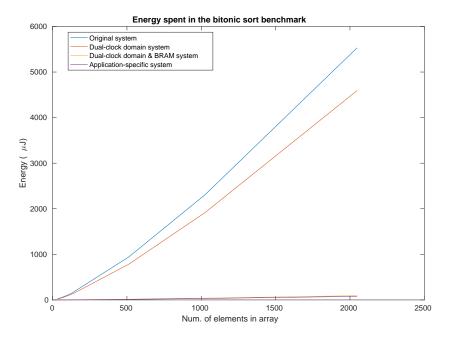

| B.6   | Energy spent in the K-means clustering benchmark - 32points, 5clusters -  |          |

|       | CU                                                                        | 76       |

| B.7   | Energy spent in the K-means clustering benchmark - 32points, 10clusters - |          |

|       | CU                                                                        | 77       |

| B.8   | Energy spent in the K-means clustering benchmark - 32points, 5clusters -  |          |

|       | Microblaze                                                                | 77       |

| B.9   | Energy spent in the K-means clustering benchmark - 32points, 10clusters - |          |

|       | Microblaze                                                                | 78       |

| B.10  | Energy spent in the K-means clustering benchmark - 64points, 5clusters -  |          |

|       | CU                                                                        | 78       |

| B.11  | Energy spent in the K-means clustering benchmark - 64points, 10clusters - |          |

|       | CU                                                                        | 79       |

| B.12  | Energy spent in the K-means clustering benchmark - 64points, 5clusters -  |          |

|       | Microblaze                                                                | 79       |

| B.13  | Energy spent in the K-means clustering benchmark - 64points, 10clusters - |          |

|       | Microblaze                                                                | 80       |

| B.14  | Energy spent in the K-means clustering benchmark - 512points, 5clusters - |          |

|       | CU                                                                        | 80       |

| B.15  | Energy spent in the K-means clustering benchmark - 512points, 10clusters  | ~ 4      |

|       | -CU                                                                       | 81       |

| B.16  | Energy spent in the K-means clustering benchmark - 512points, 5clusters - | <u> </u> |

| D 4 - | Microblaze                                                                | 81       |

| В.17  | Energy spent in the K-means clustering benchmark - 512points, 10clusters  | <b>.</b> |

|       | - Microblaze                                                              | 82       |

# **List of Tables**

| 3.1 | Type of instructions defined in Southern Islands' ISA                  | 21 |

|-----|------------------------------------------------------------------------|----|

| 3.2 | Possible instruction operands as defined in the Southern Islands' ISA  | 22 |

| 5.1 | Synthesized <i>instruction set architecture</i> (ISA)                  | 42 |

| 5.2 | Results for integer matrix multiplication.                             | 45 |

| 5.3 | Results for floating-point matrix multiplication.                      | 45 |

| 5.4 | Results for Gaussian elimination.                                      | 45 |

| 5.5 | Results for K-means clustering computation.                            | 46 |

| 5.6 | Results for bitonic sorting algorithm.                                 | 47 |

| 5.7 | Comparison in resource utilization between the original system and the |    |

|     | improved throughput performance systems, for Alpha Data's ADM-PCIE-    |    |

|     | 7V3 <sup>[1]</sup> board                                               | 48 |

|     |                                                                        |    |

List of Tables

# **List of Acronyms**

| ALU   | Arithmetic and logic unit                                     |

|-------|---------------------------------------------------------------|

| ΑΧΙ   | Advanced extensible interface                                 |

| BRAM  | Block RAM                                                     |

| BUFG  | Global buffer                                                 |

| CPU   | Central processing unit                                       |

| CU    | Compute unit                                                  |

| CUDA  | Compute Unified Device Architecture                           |

| DDR3  | Double data rate 3                                            |

| DMA   | Direct memory access                                          |

| DSP   | Digital signal processor                                      |

| ECC   | Error-correcting code                                         |

| EDA   | Electronic design automation                                  |

| FF    | Flip-flop                                                     |

| FGPU  | FPGA general-purpose GPU                                      |

| FIFO  | First-in first-out                                            |

| FPGA  | Field-programmable gate array                                 |

| GPGPU | General-purpose GPU                                           |

| GPIO  | General purpose input/output                                  |

| GPU   | Graphics processing unit                                      |

| юТ    | Internet of things                                            |

| IP    | Intellectual property (used in the context of hardware cores) |

| ISA   | Instruction set architecture                                  |

|       |                                                               |

## list of acronyms

| JTAG   | Joint test action group                            |

|--------|----------------------------------------------------|

| LED    | Light emitting diode                               |

| LSU    | Load store unit                                    |

| LUT    | Lookup-table                                       |

| MIAOW  | Many-core integrated accelerator of Wisconsin      |

| MIG    | Memory interface generator                         |

| MIPS   | Microprocessor without interlocked pipeline stages |

| ММСМ   | Mixed-mode clock manager                           |

| OCN    | On-chip network                                    |

| OpenCL | Open Computing Language                            |

| PC     | Program counter                                    |

| PE     | Processing element                                 |

| PLI    | Programming language interface                     |

| PLL    | Phase locked loop                                  |

| RAM    | Random-access memory                               |

| RTL    | Register-transfer level                            |

| RTM    | Runtime memory                                     |

| SALU   | Scalar ALU                                         |

| SDK    | Software development kit                           |

| SGPR   | Scalar general purpose register                    |

| SIMT   | Single-instruction multiple-thread                 |

| SM     | Stream multiprocessor                              |

| SP     | Scalar processors                                  |

| Tcl    | Tool command language                              |

| UART   | Universal asynchronous receiver/transmitter        |

| VALU   | Vector ALU                                         |

| VGPR   | Vector general purpose register                    |

| VHDL   | VHSIC hardware description language                |

|        |                                                    |

# List of listings

| 3.1 | Sample program flow used to test the compute unit            | 28  |

|-----|--------------------------------------------------------------|-----|

| App | pendix/full_instruction_testing/scalar_instruction_testing.c | 84  |

| App | pendix/full_instruction_testing/vector_instruction_testing.c | 104 |

| App | pendix/full_instruction_testing/mem_instruction_testing.c    | 130 |

List of listings

#

# Introduction

| Contents |

|----------|

|----------|

| 1.1 | Motivation         | 2 |

|-----|--------------------|---|

| 1.2 | Objectives         | 3 |

| 1.3 | Main Contributions | 4 |

| 1.4 | Outline            | 5 |

#### 1. Introduction

Over the years, major advances in *electronic design automation* (EDA) have greatly simplified embedded system design. From the introduction of the programmable microcontroller to the general-purpose microprocessor, while passing through many smaller dedicated circuits—which are readily available—, today's system designer is able to exploit applications intrinsic parallelism, instead of focusing solely on the specific implementation details of every module. However, when it comes to high performance computing capability, embedded design is still lacking good alternatives, which is becoming critical, especially considering the rise of the *Internet of things* (IoT) and its demand for big data processing in increasingly smaller and mobile gadgets<sup>[2]</sup>. To tackle such problems, the current trends in big data processing are focusing on *general-purpose GPUs* (GPGPUs) or on exploiting *field-programmable gate arrays* (FPGAs).

#### 1.1 Motivation

The recent evolution of *graphics processing units* (GPUs) to powerful multi-core accelerators with massive parallel processing capability created new programming paradigms, which resulted in two major frameworks, namely the *Compute Unified Device Architecture* (CUDA)<sup>[3]</sup> and *Open Computing Language* (OpenCL)<sup>[4]</sup>. With these tools, programmers can easily handle the processing of large amounts of data in relatively short periods of time. Accordingly, some manufacturers have recently released special embedded GPG-PUs<sup>[5][6]</sup> in order to bring some of this computational power to smaller devices. Although efficient and fast, hard GPGPUs still constrain flexibility when creating a hardware system as they have no room for customization. On the other hand, for many applicationspecific systems there is no need for most of the GPU's functions, which results in wasted power and circuitry area when standard solutions are used out of the box.

Moreover, while architectures have significantly evolved in order to efficiently and massively exploit parallelism, FPGAs grew bigger to the point where dozens of soft-core processors could be crammed inside a single chip<sup>[7]</sup>. Manufacturers were quick to realize the enormous parallel capability of FPGAs and it didn't take long for the appearance of complex synthesis tools, capable of transforming programs in OpenCL and create specialized hardware, which can then be readily implemented in an FPGA (e.g., Xilinx SDAc-cel<sup>[8]</sup> and Altera OpenCL SDK<sup>[9]</sup>). Although not having the same throughput performance as GPUs in most applications, FPGAs offer the ability to create a fully customized system which, in addition, results in significant power savings<sup>[10]</sup>. Reconfigurable systems come with two main drawbacks: the available resources—which, throughout this document, are referred to as area—, as it restricts the size of the project that can be implemented, and the time it takes from system design (either through *register-transfer level*

(RTL) or using a specialized OpenCL-to-hardware tool) to bitstream completion. Hence, a small change in the software implies changing the hardware, which may require hours (if not days) waiting for the new hardware bitstream to be generated.

Soft-GPUs<sup>[11][12][13]</sup>—the implementation of a GPU on an FPGA—, are set out to address some of the problems mentioned above, namely the GPU customization problem, as well as the need to re-synthesize every change in the original algorithm and implement in the target FPGA. However, this recent addition still faces the limited area problem, which affects the number of computational units that can be added to the design. To mitigate this problem, we propose application-specific soft-GPUs, a minimal GPU implementation to perform a given task without the need to re-synthesize the hardware if the problem's dimension is altered. The resulting area savings can then be used to increase parallelism and, thus, throughput performance for a given task, and help saving power by reducing the number of unused hardware resources. Accordingly, the final result of the proposed work is an area and power optimized GPU core.

## 1.2 Objectives

Considering the above, the proposed objective is to provide future embedded system designers with dedicated, ready to use, and highly optimized GPU cores. Therefore, the main focus of this work is in the development of application-specific GPGPU cores, providing not only these but also the means so that others can create their own applicationspecific soft-GPUs. Furthermore, the following objectives are proposed:

- Develop application-specific GPGPU cores;

- Improve state-of-the-art GPGPU cores, such as MIAOW, by increasing functionality and throughput performance;

- Develop a framework to test the synthesized *instruction set architecture* (ISA) implementation;

- Be compatible with state-of-the-art programming languages, such as OpenCL or CUDA, in order to easily allow offloading application computational kernels to the soft-GPGPU;

- Develop a framework for easily designing application-specific GPGPU cores;

- Show the area and power benefits of allowing an adaptation of the computing resources to the application characteristics.

#### **1.3 Main Contributions**

In this thesis, we propose the modification of GPGPU cores in order to provide an optimized system, in terms of area and power, for a given task. Thus, a selection of a few popular, widely used, and computationally intensive applications is made, and a pre-existent soft-GPGPU, namely MIAOW<sup>[12]</sup>, is re-engineered to be fully optimized for each application. Below, we highlight the main contributions of this work:

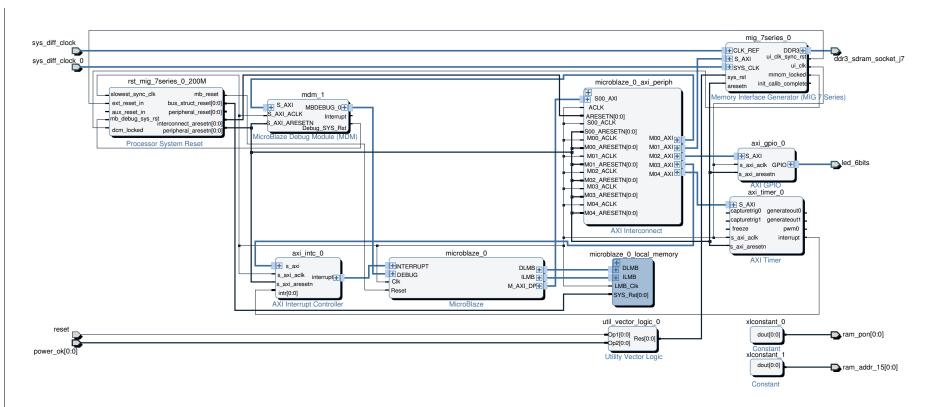

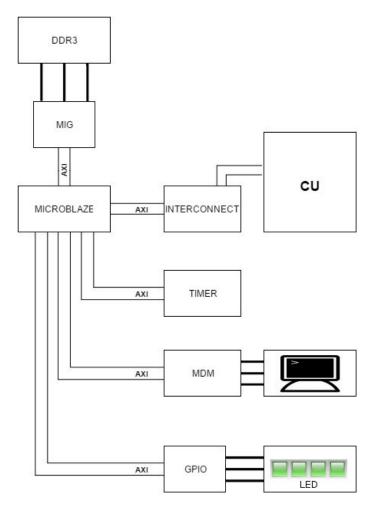

- *Designed system*: A Microblaze based system on a non-development board was developed, implemented, and validated. The board used in this work is primarily intended to serve as a data-center FPGA, meaning that it does not possess the features of development boards from Xilinx, which even have ready-to-use Microblaze systems. A detailed explanation on the design procedures for non-development boards is provided in Chapter 3.

- *Instruction testing script*: A comprehensive testing script was developed while validating the soft-GPGPU used in this work. This script lists the currently running instructions on the platform, and it can be seen in Appendices C, D, and E. A list of all working instruction is also provided in Chapter 5.

- *Corrections*: A number of corrections to the soft-GPGPU's functionalities were made in this work, which mostly focused in correcting broken instructions, or increasing the support for AMD's Southern Islands ISA. All the corrections were communicated to the original development team.

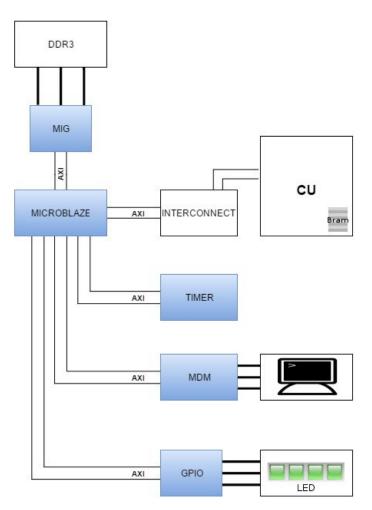

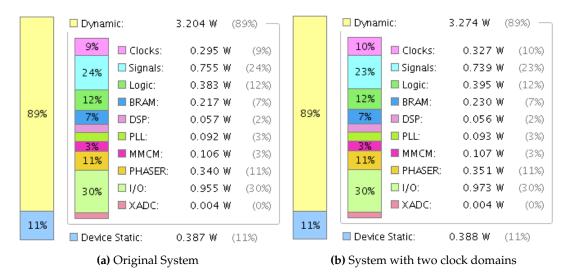

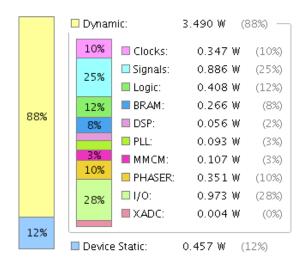

- *Improved Throughput Performance*: Modifications were made to the original soft-GPGPU with the intent of increasing throughput performance. These include separating the system into two clock domains—decreasing execution time by 1.22x—, and the addition of a *block RAM* (BRAM) module to the *compute unit* (CU), moving data closer to the processing cores—further decreasing execution time by, at least, 4x when compared to the original value. These changes are explained in detail in Chapter 4.

- *Benchmarks*: A timing profile for the implementation of the soft-GPGPU on the FPGA is also provided. This profile was obtained by benchmarking a set of well-known OpenCL applications. The results are provided in Chapter 5.

- *Application-Specific Cores*: Finally, the details behind the development of application specific soft-GPGPUs are provided in Chapter 4, explaining the changes made to the original core for each developed system. The resulting area and power savings

are displayed in Chapter 5, along with a consideration on the possibility of increasing the clock frequency to improve throughput performance, made on a per-system basis.

The enhancements proposed to the original compute unit resulted in a reduction of execution time of at least 76% (4x), reaching 98% (31x) in the most favorable scenario, while increasing the power requirement by only 10%. Furthermore, the cores' tailoring can result in power savings of up to 18%, leveraging the previous increase and releasing enough resources to instantiate a second CU on the design.

## 1.4 Outline

This thesis is organized in six chapters. After the introduction presented in this chapter, we discuss soft-GPUs, providing an insight into some of the most recent progresses in the area. Chapter 3 focuses on the details of the GPU architecture which is targeted in this work, as well as the FPGA design and validation procedures. We then focus on improving the existing cores, describing the architectural changes made in order to optimize the soft-GPGPU core for the chosen benchmarks, as detailed in chapter 4. Experimental results are presented in chapter 5 and the conclusions and future work directions are in chapter 6. 1. Introduction

# 2

# **Soft-GPGPUs Overview**

## Contents

| 2.1 | FlexGrip 8 |  |

|-----|------------|--|

| 2.2 | MIAOW 10   |  |

| 2.3 | FGPU       |  |

| 2.4 | Summary    |  |

#### 2. Soft-GPGPUs Overview

Over the years many high-performance computating accelerators have been proposed for *field-programmable gate arrays* (FPGAs). Initially, they mostly consisted of soft vector processors<sup>[14][15]</sup> which, although increasing the system's throughput for most tasks, lacked general support for conditional program execution. A few approaches of *graphics processing unit* (GPU)-like processors were also conceived<sup>[16]</sup>, grappling on to some of GPU's design concepts, but they mostly focused on extending a pre-existing processor's capability to support a few GPU-type instructions (for instance, vector arithmetic operations). Recently, efforts have been made to implement complete compute units for OpenCL platforms<sup>[12][13]</sup>, or *stream multiprocessors* (SMs) for CUDA platforms<sup>[11]</sup>, on FPGAs. These implementations bring the parallel computing capabilities of GPUs to reconfigurable systems.

Soft-GPUs present two main advantages. First, they possess the ability to be programmed with a new binary, instead of having to recompile the entire hardware system for every small change in the application, resulting in significant time savings since hardware synthesis can take hours to complete. Furthermore, they allow developing in-depth hardware configurations, leading to finely tuned architectures and implementations.

In this chapter we focus on these recently developed platforms, introducing the proposed architectures and describing them into some level of detail. Afterwards we select the best suited candidate on which we concentrate efforts and develop our work.

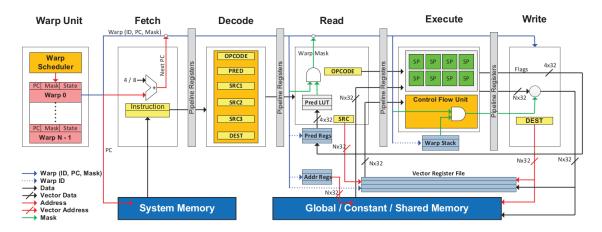

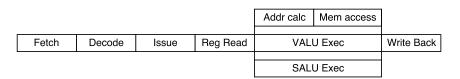

## 2.1 FlexGrip

The very first communicated implementation of a soft-general-purpose GPU (GPGPU) was FlexGrip (FLEXible GRaphIcs Processor)<sup>[11]</sup>. FlexGrip is a *register-transfer level* (RTL) implementation of an SM with multiple *scalar processors* (SP). Most of the system was written in *VHSIC hardware description language* (VHDL), while a few modules were created using MATLAB's Simulink and later converted to RTL. It is based on the *single-instruction multiple-thread* (SIMT) model, in which all SPs are running the same instruction on different threads of execution. The soft-GPGPU core features a five stage pipeline which can be observed in Figure 2.1. The stages are organized as Fetch, Decode, Read, Execute and Write.

The SM receives a program in warps, i.e., a collection of threads which share the same program counter. To dispatch these warps there is a warp unit (i.e., warp scheduler) coordinating instruction execution while maintaining information about each warp, such as a thread mask, responsible for controlling which threads are executed; a state register, indicating the current state of the warp, which can be either Ready, Active, Waiting or Finished; and the program counter. The warp scheduling is done based on a round-

**Figure 2.1:** FlexGrip Streaming Multiprocessor's pipeline. The 5 basic stages are 'Fetch', 'Decode', 'Read', 'Execute' and 'Write'. The warp unit is responsible for keeping information about warps. 'Fetch' grabs the instructions from memory and delivers them for decoding. The 'decode' stage extracts key information from the instruction, for instance the operation to be performed, the source and output operands and predicate data. 'Read' is responsible for delivering the data sources identified in the decode stage to the execute stage. 'Execute' performs the operation, providing the results to the 'write' stage, which is responsible for storing data. Image courtesy of the FlexGrip development team.

robin algorithm, i.e, attributing equal time slots to each warp and going through them using a circular mode. To start execution, the warp unit passes the base program counter to the 'fetch' stage causing an instruction load for the current warp, the instruction is then delivered for decoding in the next stage and the program counter is incremented, pointing to the next instruction. The 'decoding' stage has to break down the instruction in order to extract the opcode, operation to be executed, source operands, and the result's destination, as well as predicate data.

Upon receiving the details for the source operands the 'read' unit determines if the values should be obtained from the vector register file or from memory, either shared or global, and will perform loads accordingly, delivering the obtained data to the 'execute' stage. If the data is to be read from memory, a special set of registers, designated as address register file, is used to determine the address to access. Should the instruction include the optional predicate flags, these will be used to obtain a predicated instruction and the thread mask will suffer an update, resulting from the combination between the existing mask with the obtained value. After obtaining the source operands and updating the thread mask, these values arrive at the 'Execute' stage. Here, a number of SPs run the opcode, extracted in 'Decode', on the operators, obtained in 'Read'. This execution follows the control of the thread mask, which selects the SPs that should run the instruction. Apart from the SPs there is one control flow unit which is responsible for branch and barrier instructions. Finally, the 'write' stage is responsible for storing the results. As was the case with reads, writes can be performed in either the vector register file, for intermediate data, in the address register file, for addresses, in the predicate register file, for predicate flags, or in global memory, for final results.

The main novelty in FlexGrip is the support for direct GPU compilation, i.e., the binaries to program the system are generated by unmodified standard NVIDIA tools. The design is based on NVIDIA's G80 instruction set, which is compatible with CUDA 1.0, and has 27 working integer GPU instructions. With just these instructions FlexGrip is able to run 5 CUDA benchmarks, namely matrix multiplication, matrix correlation, matrix transpose, bitonic sort, and autocorrelation. All of these benchmarks are implemented using only integer operations as there are no floating-point arithmetical units, meaning that the core has reduced functionality for most real life applications.

In order to run, the SM needs to be connected to a MicroBlaze microprocessor, which acts as the host processor and supplies the SM with both instructions (program binary) and data, upon which processing will recall. It is worth noticing that in [11] the authors implemented an SM with eight SPs on an ML605 Virtex-6 board but were capable of creating a system with up to 32 SPs in simulation environment. This means that, had the board presented sufficient resources, a full Fermi SM (32 CUDA cores) could be implemented, which is a remarkable achievement, even if we consider the reduced functionality, like the lack of floating-point operations.

#### 2.2 MIAOW

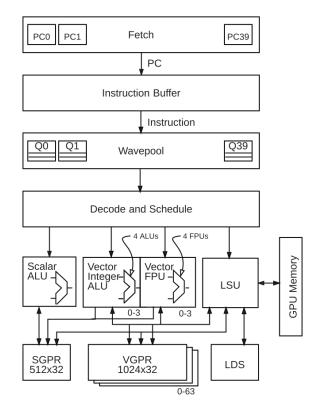

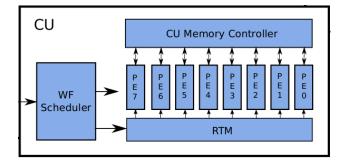

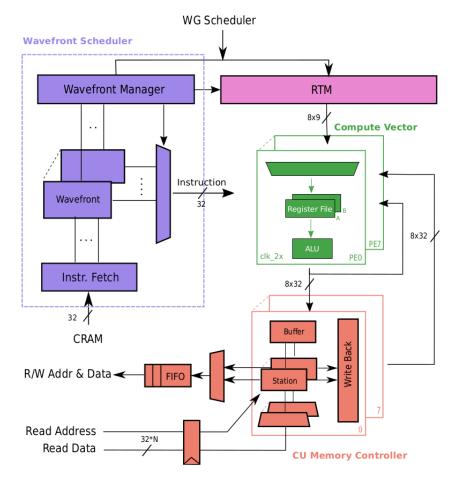

While FlexGrip focused on NVIDIA's architecture, a different approach was taken by *many-core integrated accelerator of Wisconsin* (MIAOW)<sup>[12]</sup>. MIAOW is based on AMD's notion of an OpenCL compute unit. Instead of presenting multiple SPs, OpenCL's compute unit has a single scalar *arithmetic and logic unit* (ALU) and multiple, up to four, *vector ALUs* (VALUs), which can operate in, up to, 64 scalar words at once. MIAOW was mostly developed in Verilog, utilizing a few C/C++ modules, through *programming language interface* (PLI), to model the memories, memory controllers and *on-chip network* (OCN). The *compute units* (CUs)' architecture can be seen in Figure 2.2.

One can visualize MIAOW's pipeline as being composed by six stages: 'Fetch', 'Decode', 'Issue', 'Register Read', 'Execute/Memory Access', and 'Write Back', where the fifth stage depends on the type of instruction being issued, since some of the stages can be decomposed in multiple sub-stages. A simplified scheme of the pipeline can be seen in Figure 2.3.

The CU receives a program in wavefronts, i.e., a collection of 64 work-items, known as threads in NVIDIA's terminology, which share the same program counter. Each wavefront has a set of associated data, such as the program counter, the wavefronts' identifier,

**Figure 2.2:** MIAOW's compute unit architecture. The architecture does not have a one on one correspondence with the pipeline. The blocks Fetch, Instruction Buffer, and Wavepool all belong to the Fetch stage of the pipeline. Decode and Schedule correspond to the Decode and Issue stages, respectively. Scalar ALU, Vector Integer ALU, Vector Floating Point ALU, and LSU all correspond to the Execute/Memory Access stage. All other modules are memory, either register files, SGPR and VGPR, local memory, LDS, or global memory, GPU Memory. Image courtesy of the MIAOW development team.

and the base address for both scalar and vector registers, and local memory. The 'Fetch' unit is the input port for instructions, therefore it has to receive the supra-mentioned data and place the wavefront on a queue, known as the 'Wavepool', where it waits until being selected for decoding. The selection process is done in round robin mode. At any given time, up to forty wavefronts can be present in the CU.

Upon selection, a wavefront is passed to the 'Decode' stage. There, a few parameters are extracted such as the opcode, operation to be executed; the source operands, which can range from one to three; the destination, and multiple flags, depending on the type of instruction. A few instructions use double word length, requiring two fetches and the

**Figure 2.3:** MIAOW's follows a six stage pipeline. The instruction is fetched and then decoded. After decoding it will wait until scheduling, or issuing, can be done. Once issued, the necessary operands will be read from the register file and the operation will be executed, ending with a register write back. The execution of a memory operation will require an address computation prior to the memory access.

#### 2. Soft-GPGPUs Overview

joining of the two halves, before the extraction process—decoding—can begin. Based on the extracted values, the 'Decode' unit will automatically select the type of execution unit to be used, either VALU, SALU, or *load store unit* (LSU); and translate logical register addresses into physical addresses. The decoded instruction then reaches the 'Issue' stage where it waits until all dependencies have been resolved, only starting execution when all operands are ready to be accessed. If the instruction happens to be a "barrier" or a "halt", the 'Issue' unit will handle it immediately, not requiring any intervention from the remaining stages. For all other instructions, as soon as the operands are ready, it is scheduled for execution, causing a read from the register files, 'Register Read'. According to the unit selected in the 'Decode' stage, one of three possible types of operation will be executed. If the instruction operates only on scalar operands, then SALU will be selected and an arithmetical or logical operation will be performed on the operands. A different scenario occurs for vector instructions, as VALU will be selected and multiple values will be operated at once, each value corresponding to a different thread. To determine which threads in the vector are executed, a mask, called "execute mask", will be read. This mask can be read and written to, by normal scalar operations, meaning that there can be a fine control over which threads execute at any given time. Finally, if a memory instruction is casted, the LSU will be activated and a memory access will be performed. Before issuing the memory access request, however, the LSU performs an address calculation. Once execution finishes, a 'Write-Back' will occur to either a result register, the execution mask or to the conditional control flags, which, among other things, serve as primary output for comparison instructions.

MIAOW is based on AMD's Southern Islands *instruction set architecture* (ISA)<sup>[17]</sup>, which has been used in a few of the brands' boards. The implemented CU supports 154 instructions from the ISA, being able to run unmodified OpenCL applications, i.e., it can run the kernel generated by the standard compiler without hand tuning. It is the first soft-GPGPU implementation to incorporate floating-point operations, thus considerably extending the range of possible applications.

To run a program, a system including a MicroBlaze soft-processor and DDR3 memory is required in order to supply the instructions and data to the compute unit.

In simulation, MIAOW can have up to four VALUs, each supporting 64 threads, which represents a full AMD Southern Islands CU. In the FPGA, however, developers could only implement a single VALU due to area limits on the board used, a VC707 Virtex-7<sup>[12]</sup>.

In summary, MIAOW presents a very realistic approach to GPGPU design on an FPGA since it is largely based on a real GPGPUs' ISA, and has support for a wide range

of instructions, but the lack of hardware resources available on the FPGA prevented the implementation of a full Southern Islands CU.

## 2.3 FGPU

The most recent addition to the soft-GPGPU repertoire is *FPGA general-purpose GPU* (FGPU)<sup>[13]</sup>. Unlike the previously presented MIAOW, FGPU implements its own ISA, a subset of MIPS assembly with extra, OpenCL-inspired, instructions, in order to create a soft SIMT processor. The RTL design was performed using VHDL and optimized for FPGA implementation.

Instead of presenting a single CU, or SM, as the previous two implementations, FGPU has multiple CUs, up to eight, each containing eight *processing elements* (PEs). Having multiple CUs requires an additional coordination effort, since there has to be a dispatcher which schedules jobs to the CUs, and a global memory access module, or controller, to coordinate the memory accesses from all the units. In FGPU, job dispatch to the CUs is done by a workgroup dispatcher, meaning that a whole block of wavefronts is assigned to a CU at once.

The CU is organized in four major types of blocks, the wavefront scheduler, the *runtime memory* (RTM), the processing elements, and the CU memory controller, as can be seen in Figure 2.4. Upon receiving a workgroup, the wavefront scheduler performs its

**Figure 2.4:** FGPU's Compute Unit main blocks. The CU has four major blocks, the wavefront scheduler, responsible for execution; the CU memory controller, responsible for memory accesses; the runtime memory, which holds data that can only be determined at runtime; and the processing elements, responsible for executing the instructions. Image courtesy of the FGPU development team.

division in wavefronts, composed of 64 work-items, or threads. A wavefront manager then controls which instruction is executed in the PEs, the current *program counter* (PC), and wakes up instructions, paused due to memory accesses, upon access completion. Before initializing execution, however, the wavefront scheduler also has to initialize the RTM. The RTM consists of a dual port *random-access memory* (RAM), which can be written by either the workgroup scheduler, when assigning a workgroup to the CU, or by the wavefront scheduler, when it schedules a wavefront for execution on the PEs. Its purpose is to hold data which can only be determined at runtime, such as local indices of workitems, and the global offset of scheduled workgroups. Once the RTM is initialized, the wavefront can be sent to the PEs. The PEs are responsible for executing instructions. As seen in Figure 2.5, each PE has a register file, which can contain 2048 words, and an ALU, which can perform operations with, up to, three operands. Each PE will repeat a given instruction eight times, resulting in the same operation being performed 64 times, one for each work-item in the wavefront. If a memory instruction is issued, the CU memory controller is called. An incoming request is placed in a *first-in first-out* (FIFO) buffer by a controller, called station. If the request is a write then the address and data are written in the FIFO and the controller can serve the next request. In case of a read operation, the address is placed in the FIFO and the station will listen to the data read until the request is fulfilled. After the read has been served, a write-back unit will place the data in the register file.

Differently from previous implementations where the host *central processing unit* (CPU) was a soft-CPU, in FGPU the programs are sent to the soft-GPGPU unit by an ARM processor, present in the ZC706 Zynq board used<sup>[13]</sup>.

FGPU's main novelty is the inclusion of multiple CUs on an FPGA. The design required not just the CUs but a control structure as well, in the form of a workgroup scheduler and a global memory controller. Designers implemented 18 assembly instructions, which, although limited, was sufficient to run four benchmarks, namely memcopy, vecmul and vecadd, FIR (5 taps), and cross correlation.

#### 2.4 Summary

This chapter introduced the currently known soft-GPGPU approaches and described their architectural characteristics. All these approaches differentiate from each other. The first approach, FlexGrip, focused on NVIDIA's SM and on the CUDA programming model, while the remainder two focused on OpenCL's description of a CU. In what concerns the last two options, while MIAOW focused on implementing an existing ISA, FGPU developers created their own.

MIAOW's use of a real world ISA is interesting as it supports AMD legacy code, which provides the means to use a more diverse set of benchmarks and also allows taking conclusions that are applicable to real systems. Moreover, the support of floating-point operations further broadens the scope of possible applications when compared to Flex-Grip. Furthermore, it also allows programs to be compiled using standard AMD tools, which means that no special compiler development is needed in order to test its functionality, as is the case with FGPUs' ISA. Since MIAOW has an extensive synthesized ISA, it features support for currently available programs. For these reasons, MIAOW has been selected as the base CU in this thesis.

To gain further insight into the workings of MIAOW, the next chapter focuses on the Southern Islands ISA, explaining in detail the inner architecture of a Southern Islands compute unit. It also describes in detail the system's design and validation procedures, focusing not only in the instantiation and connection of modules, but the testing procedures as well.

**Figure 2.5:** FGPU's Compute Unit main blocks internal organization. The wavefront scheduler receives complete workgroups, through the fetch, and divides them into wavefronts, these will later be dispatched by the wavefront manager. The RTM will receive data from both the workgroup scheduler and the wavefront scheduler and will allow executing wavefronts to access this data. A processing element will receive an instruction, gather the operands from the register file, and execute it in the ALU; if the instruction is a memory access it will create a request and pass it to the CU memory controller. In the CU memory controller, the controller, or station, receives memory requests placed in the buffer and dispatches them to a FIFO buffer; if a read is performed, when the requested data arrives a write back module will place this data on the register files. Image courtesy of the FGPU development team.

# 2. Soft-GPGPUs Overview

# 3

# **MIAOW Base Architecture**

### Contents

| 3.1 | Base Instruction Set Architecture 18 |

|-----|--------------------------------------|

|     | 3.1.1 Compute Unit Architecture      |

| 3.2 | NEKO 20                              |

| 3.3 | FPGA Design                          |

|     | 3.3.1 Base system                    |

|     | 3.3.2 Full system                    |

|     | 3.3.3 Simulation system              |

| 3.4 | FPGA Validation                      |

| 3.5 | Summary                              |

In the previous chapter the general characteristics of current soft-GPGPUs were reported, as well as their working mechanics in terms of pipeline organization. The most suitable candidate to work with was identified, and it consists of MIAOW, the implementation of a *compute unit* (CU) based on AMD's Southern Islands *instruction set architecture* (ISA)<sup>[17]</sup>. Taking this into consideration, and before delving into application-specific soft-GPGPUs, this chapter starts by describing key features of the selected ISA. Then, a few considerations are made on current limitations of the FPGA version of MIAOW, NEKO. Later, the bring-up procedures required to have a working system are outlined, detailing how the system is ported to the platform used in this work. The hardware validation process is described, along with a characterization of the instruction validation script developed, in terms of program flow. Finally, a list of corrections made to the original system is presented.

## 3.1 Base Instruction Set Architecture

MIAOW is based on AMD's Southern Islands ISA and its internal architecture is also inspired by the manufacturers corresponding device architecture. As with most other AMD *graphics processing units* (GPUs), MIAOW has three main modules responsible for kernel execution, namely, the host interface, the ultra-threaded dispatcher, and the compute unit. Hence, it operates as follows.

Initially, the host compiles a given kernel, which is meant to execute on the GPU, and loads it into memory. Afterwards, it specifies the memory region for the input data, and reserves space for the output. Finally, the host creates a command buffer to instruct the GPU, through the host interface, on how to execute the workload.

The host interface consists of a command processor. It is responsible for communicating with the host processor, and scheduling on-chip workloads. This interface is set to receive commands from the host through memory-mapped buffers. These can set pipeline state data, perform explicit dispatch/*direct memory access* (DMA) orders, or operations for memory/cache synchronization. After receiving the commands, the host interface acts by initializing state registers, scheduling the workloads received, performing the DMA operations required, or satisfying scheduled synchronizations.

The ultra-threaded dispatcher receives commands from the host interface, and is responsible for distributing work across the CUs. At the start of execution, this unit receives the workgroups—groups of threads which can belong to more than one wavefront—, and checks which compute unit has sufficient resources to accommodate the given wavefront. Upon finding a compute unit that can handle the workgroup, the dispatcher marks the resources as occupied, sends the workgroup and all related information, such as allocated memory buffer addresses, to the selected unit, and emits a command to start execution.

The CU is responsible for kernel execution. Upon receiving a workgroup, the CU begins dispatching instructions to the execution units, such as, the *load store unit* (LSU), the *scalar ALU* (SALU), or the *vector ALUs* (VALUs). A CU can operate in more than one wavefront at a time, using its available execution units to achieve parallelism. Once a given workgroup finishes execution, the CU waits until a new one arrives. Each CU is composed by instruction logic units, such as fetch, instruction buffer, decode, and issue; scalar and vector ALU units; scalar and vector register files; a high-bandwidth shared memory; and a one level cache, to increase memory access efficiency.

#### 3.1.1 Compute Unit Architecture

As explained when describing MIAOW's architecture (see Section 2.2), after receiving the start execution command, the CU starts filling its pipeline, fetching one instruction per cycle, until either all the execution units are busy, or the end of execution is reached. After fetching one instruction, the CU decodes it, extracting the operation code—which defines the type of instruction—, the operands, the results destination, among other information that depend on the type of instruction.

The Southern Islands ISA has two major types of instructions—scalar and vector. A scalar instruction operates on a single word (32-bit) which is shared between all the threads in the wavefront. A vector instruction, on the other hand, operates in up to 64 threads at the same time, applying the execution mask, a 64-bit vector in which each bit corresponds to a different thread. This mask marks the threads which are affected by the instruction, and which are not. Operations of either type are further subdivided according to the execution unit used, either the ALU, for computation, or the LSU, for memory access. The operations that use the ALU are named after either by the number or type of operands; or by the operation performed. For memory operations, division is made between the type of memory accessed, which can be local data share—local to the compute unit—, or external memory—through cache. The complete set of instruction types is described in Table 3.1.

After knowing the type of instruction to be performed and, consequently, the execution unit, the operands are fetched. The possible operands, as well as their number, depend on the specific instruction type. Scalar and vector instructions can use the general purpose registers available, either scalar or vector, respectively, as inputs for operations. Furthermore, scalar instructions can operate on masks, like the execution mask; the vector condition code, which stores results of vector comparisons; the scalar condition code, which stores either the results of comparisons between scalars, or the carry-out of SALU operations; the program counter; and on literal constants. Vector instructions can also access the *scalar general purpose registers* (SGPRs), the execution mask, and literal constants; apart from having access to the *vector general purpose registers* (VGPRs), and to the local data share memory. The possible operand list is summarized in Table 3.2.

Upon gathering the operands, the execution unit identified when decoding the instruction can begin executing, if it is available. The implemented compute unit has four types of execution units, they are the LSU, the SALU, the floating-point VALU, and the integer VALU. Since every execution unit can perform more than one instruction, a second decode is performed inside this unit, selecting the exact operation to execute. A typical ISA<sup>[17]</sup> implementation defines the CU as having a single LSU, a single SALU, and four of each VALUs, allowing multiple instructions to be performed simultaneously.

# 3.2 NEKO

MIAOW follows AMD's definition of a CU closely, but has a few major differences, due to either being a work in progress, and also because of physical FPGA limits.

For instance, MIAOW does not possess either the local data share or the level one cache, as of yet. This causes two major problems. First, there is no support for data share instructions—these access the local memory of the CU—, which reduces the scope of usable applications. Furthermore, without cache, all memory requests have to access slow external memory, which increases memory access delay.

Due to FPGA limits, MIAOW can not yet entirely fit in a single design and, therefore, a reduced version was developed and named NEKO. The main difference between NEKO and MIAOW lies in the number of VALUs. Although a full CU would have eight VALUs—four integer and four floating-point—, MIAOW's developers had to limit this number to one of each, in order to fit the system on an FPGA. This reduces the available parallelism, since the ability to execute more than one instruction using the same VALU type at once is lost. When choosing the applications to run on NEKO, the current limitations of the CU have to be considered. This work uses the FPGA version of MIAOW, NEKO, since it is intended to have a working system on existing platforms. This version is distributed across 189 files, including major, sub-modules, and sub-sub-modules, which roughly amount to 35 thousand lines of code.

# 3.3 FPGA Design

The work in this thesis uses an Alpha Data's ADM-PCIE-7V3<sup>[1]</sup> board. This board features a Xilinx 7 series FPGA<sup>[18]</sup>, specifically, XC7VX690T. The board used, and its FPGA,

| Operands | Туре             | Name             | Description                                                                                                                                                                 |

|----------|------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                  | SOP2             | Scalar instruction with two inputs and one output.                                                                                                                          |

|          |                  | SOPK             | Scalar instruction with one inline constant input and one output.                                                                                                           |

|          |                  | SOP1             | Scalar instruction with one input and one output.                                                                                                                           |

| Scalar   | Scalar ALU       | SOPC             | Scalar instruction with two inputs and producing a comparison result.                                                                                                       |

| Ñ        |                  | SOPP             | Scalar instruction with one in-<br>line constant input and perform-<br>ing a special operation (for exam-<br>ple: branch).                                                  |

|          | Scalar memory    | SMRD             | Scalar instruction performing a memory read from L1 memory                                                                                                                  |

|          |                  | VOP2             | Vector instruction taking two in-<br>puts and producing one output.                                                                                                         |

|          | Vector ALU       | VOP1             | Vector instruction taking one input and producing one output.                                                                                                               |

|          |                  | VOPC             | Vector instruction taking two in-<br>puts and performing one compari-<br>son.                                                                                               |

| Vector   |                  | VOP3             | Vector instruction taking three in-<br>puts and producing one output. Al-<br>lows redirecting comparison out-<br>puts to scalar registers (instead of<br>the vcc register). |

|          | Vector Memory    | Vector<br>memory | Vector memory instructions (read /<br>write) working on external mem-<br>ory.                                                                                               |

|          | Local Data Share | Data<br>share    | Vector memory instructions (read / write) working on local memory.                                                                                                          |

Table 3.1: Type of instructions defined in Southern Islands' ISA

| Туре   | Operand Name     | Description                                                                                                               |  |

|--------|------------------|---------------------------------------------------------------------------------------------------------------------------|--|

|        | SGPR0-SGPR103    | Scalar general purpose registers                                                                                          |  |

|        | VCC_LO           | Lower 32 bits of the vector condi-<br>tion code                                                                           |  |

|        | VCC_HI           | Upper 32 bits of the vector condi-<br>tion code                                                                           |  |

|        | TBA_LO           | Lower 32 bits of the trap handler base address                                                                            |  |

|        | TBA_HI           | Upper 32 bits of the trap handler base address                                                                            |  |

|        | TMA_LO           | Lower 32 bits of the pointer to data<br>in memory used by trap handler                                                    |  |

| ır     | TMA_HI           | Upper 32 bits of the pointer to data<br>in memory used by trap handler                                                    |  |

| Scalar | TMP0-TMP11       | Trap handler temporary registers                                                                                          |  |

| Ň      | M0               | Memory register 0                                                                                                         |  |

|        | EXEC_LO          | Lower 32 bits of the execution mask                                                                                       |  |

|        | EXEC_HI          | Upper 32 bits of the execution mask                                                                                       |  |

|        | -16-64           | Literal integer constants -16 to 64                                                                                       |  |

|        | 0.5              | Literal constant 0.5                                                                                                      |  |

|        | -0.5             | Literal constant -0.5                                                                                                     |  |

|        | 1.0              | Literal constant 1.0                                                                                                      |  |

|        | -1.0             | Literal constant -1.0                                                                                                     |  |

|        | 2.0              | Literal constant 2.0                                                                                                      |  |

|        | -2.0             | Literal constant -2.0                                                                                                     |  |

|        | 4.0              | Literal constant 4.0                                                                                                      |  |

|        | -4.0             | Literal constant -4.0                                                                                                     |  |

|        | VCCZ             | Result of the comparison between<br>VCC and zero. Automatically up-<br>dated with every change to VCC.                    |  |

|        | EXECZ            | Result of the comparison between<br>the execution mask and zero. Au-<br>tomatically updated with every<br>change to EXEC. |  |

|        | SCC              | Scalar condition code.                                                                                                    |  |

| -      | LDS direct       | Input read directly from local data share                                                                                 |  |

|        | Literal constant | 32-bit literal constant that follows the current instruction                                                              |  |

| Vector |                  | All of the above                                                                                                          |  |

| ,      | VGPR0-255        | Vector general purpose registers                                                                                          |  |

Table 3.2: Possible instruction operands as defined in the Southern Islands' ISA

Exception: According to the ISA<sup>[17]</sup>, SMRD instructions cannot receive literal constants as input.

are different from the ones used by MIAOW's original development team. Therefore, it was necessary to port their system, redesigning it to attend to the board's features.

System design was made using Xilinx's Vivado Design Suite<sup>[19]</sup>, which did not, originally, feature support for Alpha Data's board. To work around this issue, a modified version of the board support files from Xilinx SDAccel<sup>[8]</sup> was developed and used, effectively adding support to the board in Vivado<sup>[19]</sup>.

After adding the board support files to Vivado, system design could ensue. The following subsection addresses the composition of the system supporting the CU's execution. Afterwards, the instantiation of NEKO is described, focusing on how it connects to the base system.

#### 3.3.1 Base system

To design the system which supports the compute unit, Xilinx's tutorial for embedded design<sup>[20]</sup> was used. Since the board featured in the tutorial is different from the available one, it can not be followed directly. Nonetheless, the ideas behind system development remain valid and the work-flow is very similar to the one described in the tutorial.

The base system has four major components, which are a soft microprocessor, called Microblaze<sup>[21]</sup>, a DDR3 RAM memory controller<sup>[22]</sup>, a timer<sup>[23]</sup>, and a debug module<sup>[24]</sup> for Microblaze.