João António Batista Maria

# Accelerating the Processing of Neural Networks for Object Recognition Using Low-power Devices

Dissertação de Mestrado em Engenharia Electrotécnica e de Computadores

Setembro de 2014

Universidade de Coimbra

## Aceleração do Funcionamento de Redes Neuronais para Reconhecimento de Objectos em Plataformas de Baixa Potência

João António Batista Maria

Dissertação para obtenção do Grau de Mestre em **Engenharia Electrotécnica e de Computadores**

Orientador:Doutor Gabriel Falcão Paiva FernandesCo-Orientador:Doutor Luís Filipe Barbosa de Almeida Alexandre

#### Júri

| Presidente: | Doutor Vítor Manuel Mendes da Silva        |

|-------------|--------------------------------------------|

| Orientador: | Doutor Gabriel Falcão Paiva Fernandes      |

| Vogais:     | Doutor Fernando Manuel dos Santos Perdigão |

Setembro de 2014

## Agradecimentos

A vontade de avançar para uma dissertação de mestrado com o Professor Gabriel Falcão veio desde o 1º ano deste curso. Foi aí que primeiro tive contacto com a sua capacidade de educar, de abrir portas à nossa imaginação e nos motivar para darmos sempre o nosso melhor. Ao longo de todo este percurso académico, e em especial com a dissertação de mestrado, beneficiei do seu apoio e orientação, sem nunca impor barreiras de tempo ou paciência. Esteve sempre a meu lado, a acompanhar-me a cada passo e a dar-me sempre metas mais além, num constante desafio que me motivou mais e mais, e que tanto me fez crescer como aluno, como também como pessoa. Por tudo isto lhe estou eternamente grato, foi um orientador de mestrado e da vida.

Apesar da distância que nos separou, todo este trabalho seria impensável sem a experiência e apoio do Professor Luís Alexandre. A ele tenho a agradecer a sua disponibilidade para ensinar, arranjando forma de ultrapassar os obstáculos com que nos fomos deparando, sempre com paciência e um grande positivismo ao longo de todo o acompanhamento que me deu, numa área que me era desconhecida. Quero também agradecer ao Xavier Frazão, pelas bases de onde parti para a minha dissertação, e que estarão sempre ligadas a este projeto.

Agradeço à minha família, em especial aos meus pais, avós e sogros, por me terem suportado ao longo de todos estes anos académicos, por nunca terem duvidado de mim, por me terem apoiado em todas as minhas decisões. Graças a eles tive assim a oportunidade de explorar todo o meu potencial, com uma base de tranquilidade e apoio interminável.

Não há palavras que descrevam o incomensurável apoio da minha namorada, Nádia, ao longo de todos estes anos. Desde me motivar quando as coisas não corriam tão bem, até me tratar do jantar e não me deixar morrer à fome, devo-lhe tudo. O seu amor, carinho e entusiasmo, deu-me energia para vencer este desafio, para todos os dias dar o melhor de mim. A ti te agradeço por estes anos, mas acima de tudo por acreditares em mim mais do que eu mesmo.

Por fim, mas de todo não por último, agradeço também a todos os meus amigos e colegas. Graças à vossa amizade e apoio, estes anos passaram num instante, oferecendo memórias inesquecíveis. Foram muitas as noitadas de trabalho e diversão que tivemos juntos, cresci com vocês, e com vocês partilhei os anos mais importantes da minha vida. Obrigado por tudo.

## Abstract

Over the last years, deep learning architectures have gained attention by winning some of the most important international detection and classification competitions, but this comes at a cost: these models are computationally expensive and have been recently ported to Graphics Processing Units (GPUs) to allow faster deployment. However, desktop GPUs have their own shortcomings and seem to be quickly approaching the limits of power and heat dissipation walls, imposing high levels of energy consumption. This implies high deployment costs in applications that process big data volumes on a permanent basis, and also the inability to use these architectures, for example, in autonomous systems such as vehicles and robots, which can hardly provide low power supplies. Therefore, this thesis proposes another shift of paradigm, this time from GPU-based deep learning approaches to an Field-Programmable Gate Array (FPGA)-based context. We show how to implement a particular type of deep learning architecture, the Stacked Autoencoder (SAE), and compare both accuracy and energy consumption levels achieved against similar implementations both on desktop and mobile GPUs. The results show that similar classification and error performances can be obtained using the SAE proposed solution, with paid dividends in energy savings. Also important is the fact that the proposed SAE architecture is scalable, and FPGAs and mobile GPUs have probably better progress margin than desktop GPUs. These results also pave the way for adopting low-power devices in energy-constrained applications for big data classification.

## Keywords

Deep Learning, Neural Networks, Stacked Autoencoder, Parallel Computing, FPGAs, GPUs, OpenCL

## Resumo

Ao longo dos últimos anos, as arquitecturas de *deep learning* têm vindo a ganhar destaque ao vencerem algumas das mais importantes competições internacionais de detecção e classificação, mas isso tem um preço: estes modelos são computacionalmente exigentes e foram recentemente portados para execução em placas gráficas de modo a permitir o seu rápido desenvolvimento. Contudo, as placas gráficas de desktop têm as suas limitações e parecem estar rapidamente a aproximar-se dos limites de potência e de barreiras de dissipação de calor suportáveis, com elevados níveis de consumo energético. Isto implica elevados custos de desenvolvimento em aplicações que processem um elevado volume de dados em regime permanente, assim como a incapacidade para usar estas arquitecturas, por exemplo, em sistemas autónomos como veículos e robots, que dificilmente conseguem fornecer uma fonte de baixa potência com autonomia. Assim, esta tese propõe uma mudança de paradigma, de uma abordagem a *deep learning* baseada em placas gráficas para um contexto baseado em Field-Programmable Gate Arrays (FPGAs). Mostramos como implementar uma arquitectura de deep learning em particular, o Stacked Autoencoder (SAE), e uma comparação tanto ao nível da precisão como de consumo energético obtidos face a implementações similares em placas gráficas de desktop e de plataformas móveis. Os resultados mostram que desempenhos semelhantes na classificação e erro podem ser atingidos usando a solução de SAE proposta, com dividendos pagos em poupança energética. Também é importante o facto de que a arquitectura de SAE proposta é escalável, e que as FPGAs e placas gráficas móveis têm provavelmente uma maior margem de progresso do que as placas gráficas de *desktop*. Estes resultados abrem também o caminho à adopção de dispositivos de baixa potência para classificação de grandes volumes de dados, em aplicações com elevadas restrições energéticas.

## **Palavras Chave**

Deep Learning, Redes Neuronais, Stacked Autoencoder, Computação Paralela, FP-GAs, GPUs, OpenCL

# Contents

| 1 | Intro | duction 1                                               |

|---|-------|---------------------------------------------------------|

|   | 1.1   | Motivation                                              |

|   | 1.2   | Objectives                                              |

|   | 1.3   | Main contributions                                      |

|   | 1.4   | Dissertation outline                                    |

| 2 | Deep  | Learning using Neural Networks 5                        |

|   | 2.1   | Neuron                                                  |

|   | 2.2   | Artificial Neural Networks                              |

|   |       | 2.2.1 Perceptron                                        |

|   |       | 2.2.2 Multi-Layer Perceptron                            |

|   | 2.3   | State-of-the-Art: The Convolutional Neural Network      |

|   | 2.4   | Sub-optimal Neural Networks                             |

|   |       | 2.4.1 Autoencoder                                       |

|   |       | 2.4.2 Stacked Autoencoder                               |

|   | 2.5   | Softmax Classifier                                      |

|   | 2.6   | Neural Networks Hyper-parameters                        |

|   |       | 2.6.1 Learning Rate                                     |

|   |       | 2.6.2 Batch Size                                        |

| 3 | Har   | ware Parallelism with OpenCL Supported Architectures 17 |

|   | 3.1   | Desktop GPU                                             |

|   |       | 3.1.1 AMD R9 290X (Hawaii)                              |

|   |       | 3.1.2 Nvidia GTX Titan (GK110)                          |

|   | 3.2   | Mobile GPU                                              |

|   |       | 3.2.1 Qualcomm Adreno 330 (Snapdragon 800)              |

|   | 3.3   | FPGA                                                    |

|   |       | 3.3.1 Altera Stratix V GS D5 (5SGSD5)                   |

| 4 | Higł | n-Level Synthesis and OpenCL Structure for Neural Networks | 25 |

|---|------|------------------------------------------------------------|----|

|   | 4.1  | The OpenCL Programming Framework                           | 26 |

|   |      | 4.1.1 OpenCL Platform Layer                                | 26 |

|   |      | 4.1.2 OpenCL Runtime                                       | 28 |

|   | 4.2  | General OpenCL Optimizations for Neural Networks           | 31 |

|   | 4.3  | OpenCL Kernels for Neural Network Parallelism              | 33 |

|   |      | 4.3.1 Feed-Forward                                         | 34 |

|   |      | 4.3.2 Back Propagation - Output Layer                      | 35 |

|   |      | 4.3.3 Back Propagation - Hidden Layer                      | 35 |

|   | 4.4  | FPGA-Specific High-Level Optimizations                     | 35 |

|   |      | 4.4.1 Compute Units                                        | 36 |

|   |      | 4.4.2 SIMD Vectorization                                   | 37 |

|   |      | 4.4.3 Loop Unrolling                                       | 37 |

| 5 | Met  | hodology                                                   | 39 |

|   | 5.1  | The MNIST Dataset                                          | 40 |

|   | 5.2  | FPGA Hardware Resources Utilization                        | 40 |

|   |      | 5.2.1 Floating-Point Processing                            | 40 |

|   | 5.3  | Training Time                                              | 40 |

|   | 5.4  | Reconstruction/Classification Error                        | 41 |

|   |      | 5.4.1 Validation Set/Error                                 | 41 |

|   | 5.5  | Throughput Performance                                     | 42 |

|   | 5.6  | Power and Energy Consumption                               | 42 |

|   | 5.7  | Throughput per Power Ratio                                 | 42 |

|   | 5.8  | Apparatus                                                  | 42 |

| 6 | Exp  | erimental Results                                          | 47 |

|   | 6.1  | Training Hyper-parameters                                  | 48 |

|   | 6.2  | FPGA Optimizations and Hardware Utilization                | 48 |

|   | 6.3  | Evaluating the Neural Network                              | 49 |

|   | 6.4  | Throughput and Energy Analysis                             | 51 |

|   | 6.5  | Discussion                                                 | 53 |

| 7 | Con  | clusions                                                   | 55 |

|   | 7.1  | Future Work                                                | 57 |

| A | Арр  | endix A                                                    | 63 |

|   | A.1  | Autoencoder Flow                                           | 64 |

|   |     | Training Flow       Classification Flow |    |

|---|-----|-----------------------------------------|----|

| B | App | endix B                                 | 69 |

| С | Арр | endix C                                 | 77 |

Contents

# **List of Figures**

| 2.1  | A schematic of the biological neuron                                                                       | 6  |

|------|------------------------------------------------------------------------------------------------------------|----|

| 2.2  | A logical approach to the neuron: the artificial neuron                                                    | 7  |

| 2.3  | A collection of logical operations responses, with associated decision                                     |    |

|      | boundaries and hyperplanes (green for $0$ , white for $1$ )                                                | 8  |

| 2.4  | A graphical representation of a Multi-layer Perceptron                                                     | 8  |

| 2.5  | Topology of the Convolutional Neural Network (CNN) for the CIFAR-10                                        |    |

|      | dataset [1]                                                                                                | 10 |

| 2.6  | Example of an autoencoder (left) and of a stacked autoencoder (right)                                      | 11 |

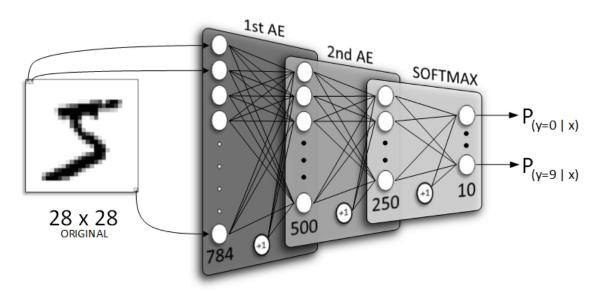

| 2.7  | Topology of the first autoencoder for the MNIST dataset                                                    | 12 |

| 2.8  | Topology of the stacked autoencoder for the MNIST dataset                                                  | 13 |

| 2.9  | Impact of different learning rates. A low $(0.1)$ learning rate gets caught in                             |    |

|      | a local minimum (slow error convergence), an ideal (0.45) learning rate                                    |    |

|      | achieves the lowest possible error, and a high (1.0) learning rate goes past                               |    |

|      | the ideal value (error divergence)                                                                         | 14 |

| 2.10 | Another example of the impact on the final result of a low $(0.1)$ , an ideal                              |    |

|      | $(0.45)$ and a high $(1.0)$ learning rate $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 15 |

| 3.1  | The AMD R9 290X (Hawaii) Graphics Processing Unit (GPU) block di-                                          |    |

|      | agram [2]                                                                                                  | 19 |

| 3.2  | A detailed view of the Graphics Core Next (GCN) Architecture Compute                                       |    |

|      | Unit in the AMD R9 290X (Hawaii) [2]                                                                       | 19 |

| 3.3  | The Nvidia GTX Titan (GK110) GPU block diagram [3]                                                         | 20 |

| 3.4  | A detailed view of the Streaming Multiprocessor (SMX) Architecture in                                      |    |

|      | the Nvidia GTX Titan (GK110) [3]                                                                           | 21 |

| 3.5  | The Qualcomm Adreno 330 GPU in the Snapdragon 800 System On Chip                                           |    |

|      | (SoC) [4]                                                                                                  | 22 |

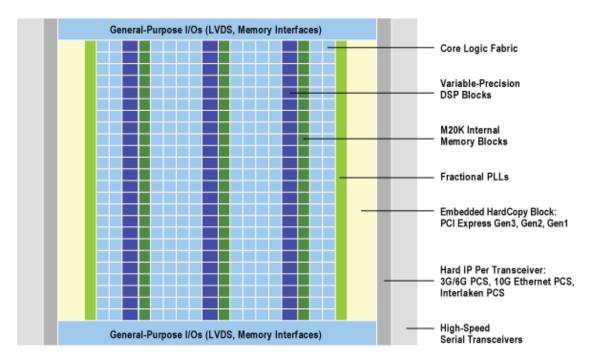

| 3.6  | Stratix V FPGA architecture and features [5]                                                               | 23 |

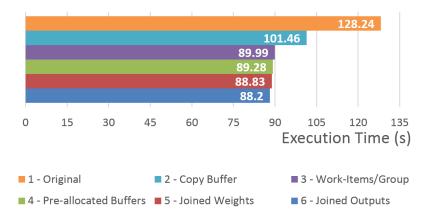

| 4.1  | Comparison of the five initial OpenCL optimizations performed                                              | 33 |

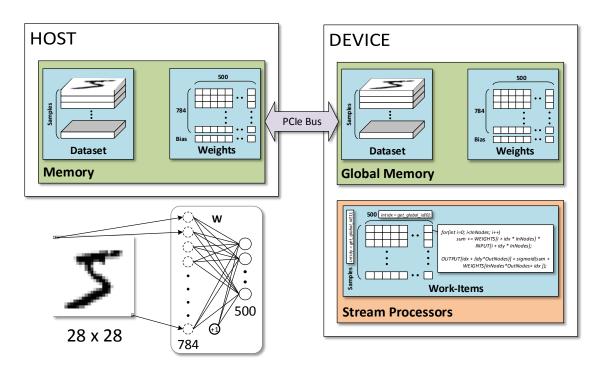

| 4.2  | Feed forward work-items spread across two dimensions                                                       | 34 |

|      |                                                                                                            |    |

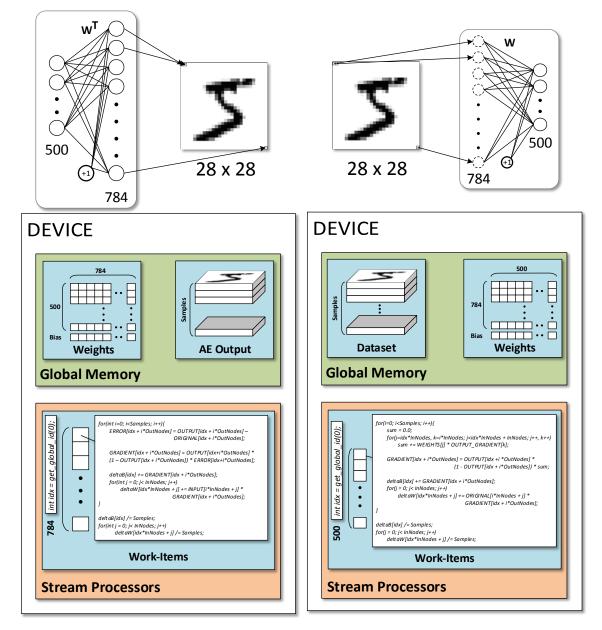

| 4.3 | Back propagation work-items for the output layer (decoder)                 | 36 |

|-----|----------------------------------------------------------------------------|----|

| 4.4 | Back propagation work-items for the hidden layer (encoder)                 | 36 |

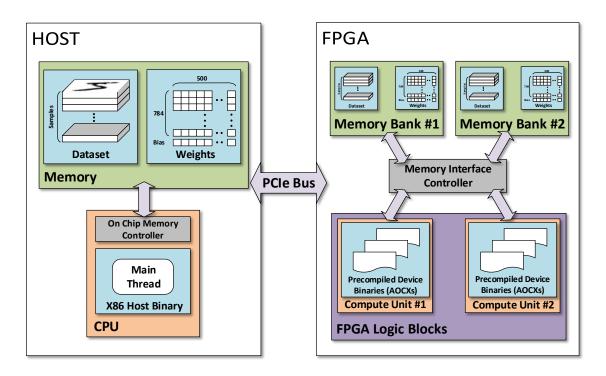

| 4.5 | Architecture of the FPGA running the Open Computing Language (OpenCL)      |    |

|     | kernels on two Compute Units (CUs)                                         | 37 |

| 5.1 | The AMD R9 290X from Gigabyte [6]                                          | 43 |

| 5.2 | The Nvidia GTX Titan from ASUS [7]                                         | 43 |

| 5.3 | The Snapdragon 800 DragonBoard from Qualcomm [8]                           | 44 |

| 5.4 | The Altera Stratix V D5 from Nallantech [9]                                | 44 |

| 6.1 | Reconstruction error comparison over 6 batch sizes and 4 learning rates .  | 48 |

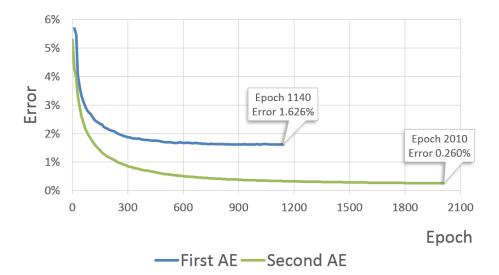

| 6.2 | SAE reconstruction error as function of the number of epochs               | 50 |

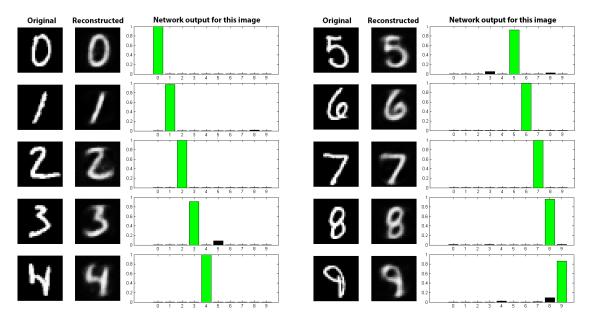

| 6.3 | Some of the images correctly classified (from MNIST)                       | 51 |

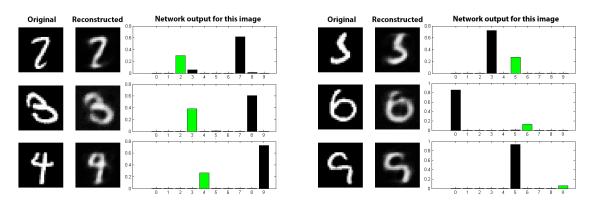

| 6.4 | Difficult cases and near misses (from MNIST)                               | 51 |

| 6.5 | A collection of misclassified images (from MNIST)                          | 52 |

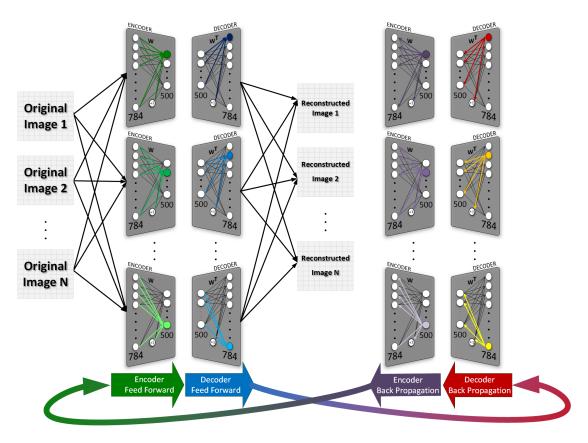

| A.1 | Detailed autoencoder flow diagram                                          | 64 |

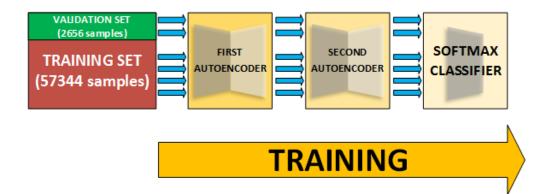

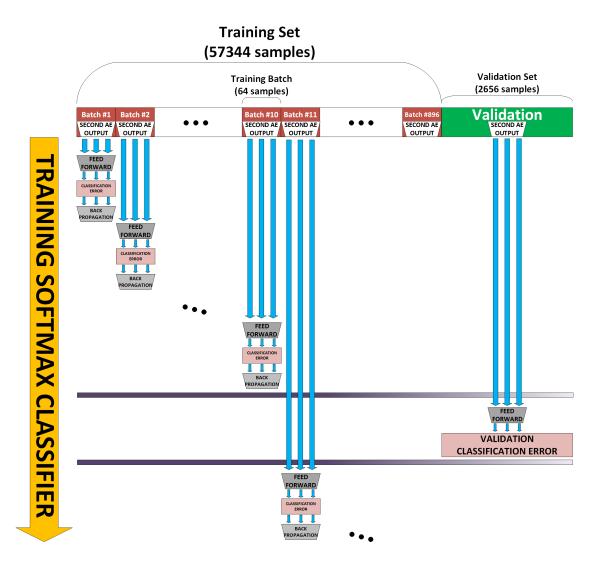

| A.2 | Training flow diagram. The training flow of the first autoencoder is ex-   |    |

|     | plained in more detail in Fig. A.3, the second autoencoder in Fig. A.4 and |    |

|     | the softmax classifier in Fig. A.5                                         | 64 |

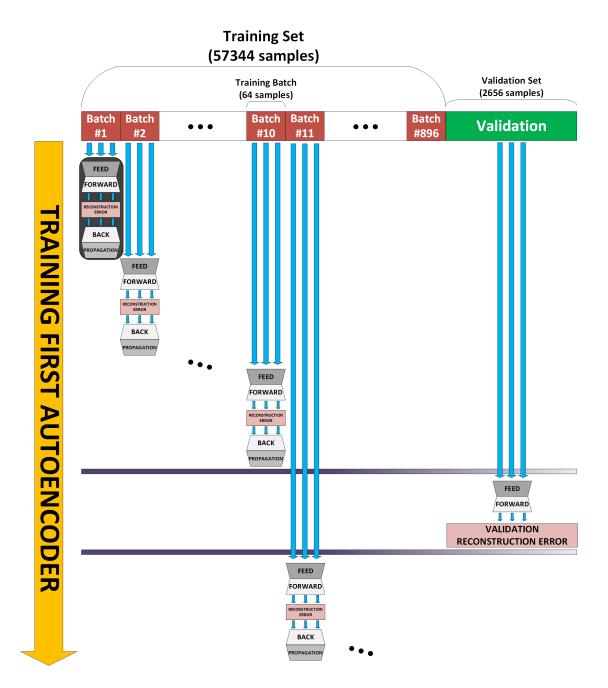

| A.3 | First autoencoder training flow diagram. The detailed execution flow of    |    |

|     | the autoencoder in the shadowed area below Batch #1 is explained in        |    |

|     | Fig. A.1                                                                   | 65 |

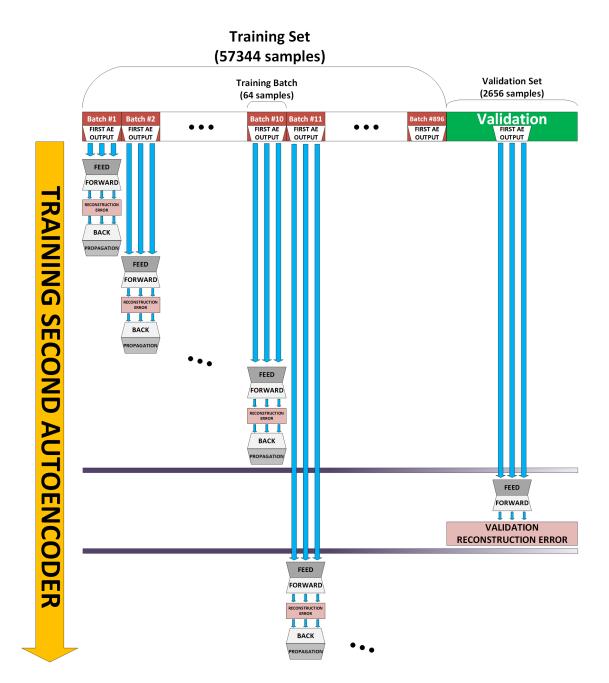

| A.4 | Second autoencoder training flow diagram                                   | 66 |

| A.5 | Softmax Classifier training flow diagram                                   | 67 |

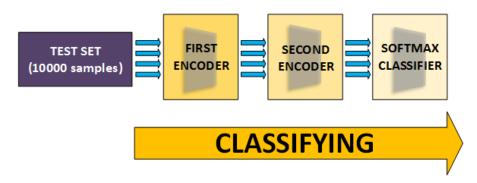

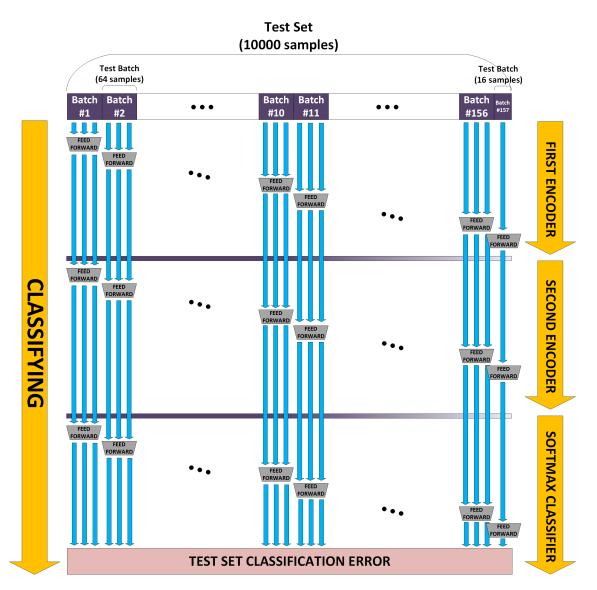

| A.6 | Test set classification flow diagram. The classification flow is explained |    |

|     | in more detail in Fig. A.7                                                 | 67 |

| A.7 | Test set classification flow diagram                                       | 68 |

# **List of Tables**

| 5.1 | Hardware overview of the computing platforms                                | 45 |

|-----|-----------------------------------------------------------------------------|----|

| 5.2 | Cost and power consumption for the OpenCL devices, as per indicated         |    |

|     | manufacturer data                                                           | 45 |

| 6.1 | FPGA hardware resources utilization as obtained by the Altera OpenCL        |    |

|     | SDK compiler                                                                | 49 |

| 6.2 | Final SAE training time for the four different platforms, with a batch size |    |

|     | of 64 images and initial learning rate equal to 0.45                        | 50 |

| 6.3 | Running time and throughput performance associated with four different      |    |

|     | computing platforms, while training the first AE with a batch size of 64    |    |

|     | images and initial learning rate of 0.45                                    | 52 |

| 6.4 | Running time and throughput performance associated with four different      |    |

|     | computing platforms, during the classification of a batch of 64 images      | 53 |

| 6.5 | Total SAE training time and energy consumption associated with four dif-    |    |

|     | ferent computing platforms, using a batch size of 64 images and learning    |    |

|     | rate of 0.45                                                                | 53 |

| 6.6 | Throughput per power ratio over four different computing platforms          | 53 |

# **List of Algorithms**

| 1 | Round Up to the Best Work-Group Size Performer | 32 |

|---|------------------------------------------------|----|

| 2 | Checkpoint and Cross-Validation                | 41 |

# **List of Acronyms**

| AE   | Autoencoder                                    |

|------|------------------------------------------------|

| ACE  | Asynchronous Compute Engine                    |

| AMD  | Advanced Micro Devices                         |

| ANN  | Artificial Neural Network                      |

| ΑΡΙ  | Application Programming Interface              |

| ARM  | Advanced RISC Machine                          |

| CNN  | Convolutional Neural Network                   |

| CPU  | Central Processing Unit                        |

| CU   | Compute Unit                                   |

| CUDA | Compute Unified Device Architecture            |

| DBN  | Deep Belief Network                            |

| DDR  | Double-Data Rate                               |

| DNN  | Deep Neural Network                            |

| DSP  | Digital Signal Processing                      |

| FPGA | Field-Programmable Gate Array                  |

| FPS  | Frames-per-second                              |

| GCN  | Graphics Core Next                             |

| GDDR | Graphics Double-Data Rate Random Access Memory |

| GPC  | Graphics Processing Cluster                    |

| GPU                  | Graphics Processing Unit                                                                                 |

|----------------------|----------------------------------------------------------------------------------------------------------|

| HLS                  | High-level Synthesis                                                                                     |

| LP                   | Low-Power                                                                                                |

| МС                   | Memory Controller                                                                                        |

| MLP                  | Multi-Layer Perceptron                                                                                   |

| MNIST                | Mixed National Institute of Standards and Technology                                                     |

| NN                   | Neural Network                                                                                           |

| OpenCL               | Open Computing Language                                                                                  |

| PCle                 | Peripheral Component Interconnect Express                                                                |

| RBM                  | Restricted Boltzmann Machine                                                                             |

| RTL                  | Register Transfer Level                                                                                  |

| SAE                  | Stacked Autoencoder                                                                                      |

| SDAE                 | Stacked Denoising Autoencoder                                                                            |

|                      |                                                                                                          |

| SDK                  | Software Development Kit                                                                                 |

| SDK<br>SDRAM         | Software Development Kit<br>Synchronous Dynamic Random Access Memory                                     |

| -                    | -                                                                                                        |

| SDRAM                | Synchronous Dynamic Random Access Memory                                                                 |

| SDRAM<br>SIMD        | Synchronous Dynamic Random Access Memory<br>Single Instruction Multiple Data                             |

| SDRAM<br>SIMD<br>SMX | Synchronous Dynamic Random Access Memory<br>Single Instruction Multiple Data<br>Streaming Multiprocessor |

#

# Introduction

#### Contents

| 1.1 | Motivation           | 2 |

|-----|----------------------|---|

| 1.2 | Objectives           | 3 |

| 1.3 | Main contributions   | 3 |

| 1.4 | Dissertation outline | 4 |

#### 1. Introduction

Associated to the processing of increasingly larger amounts of (big) data, machine learning and perception models aim at solving more complex and challenging tasks with lower classification errors. The number of samples used to train the algorithms now surpasses the hundreds of thousands, which poses severe constraints regarding the time and processing power necessary to train the networks.

Recently, deep learning architectures have gained some momentum because they have shown superior performance in some of the most important international image, sound / voice detection and classification competitions [10–12]. These typically deal with the automatic recognition of objects in images, whether these objects are in effect traffic signs, digits, objects or animals, and have been won by research teams exploiting deep neural networks of the convolutional type [10]. The current trend in machine learning / perception presently exploits the use of multiple representation levels, which can be achieved using deep belief networks, Stacked Denoising Autoencoder (SDAE) or Convolutional Neural Networks (CNNs), among others.

However, such current state-of-the-art implementations are known to consume high energy levels in order to produce the expected results, which directly impacts the processing costs of big data and also creates constraints in their utilization in autonomous vehicles / robots. Moreover, some of the powerful parallel computing devices under utilization, namely Graphics Processing Units (GPUs), are reaching power- and heatdissipation walls [13] (also known as utilization wall). Therefore, low power architectures and corresponding energy-saving strategies are required at this point of neural networks development.

#### 1.1 Motivation

In this thesis we propose Stacked Autoencoder (SAE) architectures for reconfigurable Field-Programmable Gate Array (FPGA) substrates, as a first step towards the implementation of more complex approaches to deep learning, such as CNNs. Even though modern FPGAs support a high number of hardware resources, the proposed approach of investigating a simpler Neural Network (NN) is justified by the fact that implementing, for example, a CNN with the complexity of the largely adopted framework [14], would require an FPGA with orders of magnitude more resources than those provided by current state-of-the-art devices.

We propose to lower the N-dimensionality representation of the problem and associated computational complexity of the parallel architecture developed, allowing for suboptimal results albeit making it more tractable and thus able to cope with the existing available hardware resources of modern FPGAs. These low-power FPGA architectures consume at least one order of magnitude less energy and are still able to provide real-time throughput and competitive classification error performance, when compared to existing clusters of other high-performance computational resources such as GPUs or Central Processing Units (CPUs). The objective is to conciliate the quality of object recognition with faster or even real-time execution capabilities at low-energy consumption budgets.

The main problems identified are the limited hardware resources available in recent FPGAs to support this type of NN-based algorithms; the bandwidth bottleneck to access global memory; and the long development times associated with Register Transfer Level (RTL) design / development. The former problems can be addressed by developing new algorithms based on less complex Autoencoder (AE) networks. The latter can be overcome using new High-level Synthesis (HLS) tools that are very effective for designing and prototyping hardware systems for reconfigurable devices in short periods of time [15].

#### 1.2 Objectives

In this thesis we show for the first time how we can train a type of NN, designated as the SAE, on low-power FPGAs architectures. In particular, we propose:

*i)* to develop a SAE architecture based on low-power processing using FPGA devices for classifying huge datasets that includes the training phase. For the best of our knowledge, these long training periods have never been processed on these devices before (they are usually processed on the GPU). To exemplify these scenarios we develop solutions for processing the well-known Mixed National Institute of Standards and Technology (MNIST) dataset.

and *ii*) to perform a power performance analysis by comparing the power and energy efficiency of these algorithms in several computing platforms, from desktop and mobile GPUs to FPGAs: we present experiments illustrating not only the accuracy obtained using these SAE architectures, but also the execution times and the respective power and energy consumption savings achieved when processing large amounts of images.

#### **1.3** Main contributions

This thesis proposes new solutions that advance the state-of-the-art of artificial intelligence, computer vision and parallel processing using the compute horse-power capabilities of FPGAs. We provide a scalable and multi-platform solution for training a SAEsbased NN, aimed at detecting objects, characters, or other type of structures in entire city

#### 1. Introduction

maps. As the technology in the FPGA progresses and more processing resources are made available, a shift to more robust types of NNs, such as the state-of-the-art CNNs, will be possible. Moreover, we pave the way for new applications in a diversity of areas that can benefit from the accurate real-time recognition of objects with lower consumption budgets. These areas include not only big data processing, as for example the identification and classification of large image data related to the visual information of entire city streets (modern infrastructures like Google need to process and classify such large amounts of data on a daily/permanent basis), but also robotics or autonomous vehicles, which all present severe low-power constraints.

This work resulted in the article "Energy-efficient Deep Learning: Stacked Autoencoders on FPGAs and Mobile GPUs", submitted to the ACM Transactions on Architecture and Code Optimization journal and in "Low-power Accelerated Architectures using Stacked Autoenconders for Object Recognition in Autonomous Systems", submitted to Neural Processing Letters - Special Issue on Neural Networks for Vision and Robotics. Both these articles are available in the Appendixes B and C, respectively.

#### **1.4 Dissertation outline**

This thesis is structured in seven chapters. After this brief introduction, the principles of Artificial Neural Networks (ANNs) and their relation to the biological model will be depicted in Chapter 2, followed by a detailed look over the SAE selected for our work. In Chapter 3 we describe the hardware architecture of the desktop and mobile GPUs and FPGA platforms. Chapter 4 explains the Open Computing Language (OpenCL) programming framework and the work developed to achieve efficient NN parallelism. Through Chapter 5 we explain the experimental metrics and the specific test systems and OpenCL devices used in our work. Regarding those metrics, in Chapter 6 we detail and analyze our experimental results, evaluating the network and the test platforms in question. Finally, in Chapter 7, we draw final conclusions of our work and discuss future improvements and goals.

# **Deep Learning using Neural Networks**

#### Contents

| 2.1 | Neuron                                               |

|-----|------------------------------------------------------|

| 2.2 | Artificial Neural Networks 7                         |

| 2.3 | State-of-the-Art: The Convolutional Neural Network 9 |

| 2.4 | Sub-optimal Neural Networks 10                       |

| 2.5 | Softmax Classifier                                   |

| 2.6 | Neural Networks Hyper-parameters                     |

The decisions we make in everyday life are based on personal experience, with knowledge acquired over the years, shaped by our personal view of the world. An immense amount of information helps us making those decisions. Things we saw, heard, smelled or touched, produce a weighted effect, coming together to help us forming an opinion.

In modern neuroscience, scientists from several fields have been studying the brain, formed by neural interconnections and responses, with the neuron acting as the basic unit of the nervous system as described in the early 20th century [16]. With visualization possible under optical microscopy, we now have a deeper understanding of the structure and operation of a neuron.

#### 2.1 Neuron

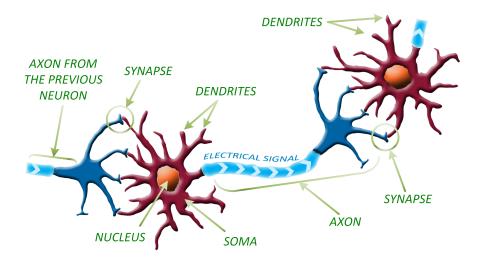

An abstract model of the biological neuron is comprised of a *soma* or neuron cell body, several *dendrites* that extend from the soma, and a single *axon*, a structure similar to dendrites but longer (as far as 1 meter in humans) [17]. A neuron axon can connect to dendrites in other neurons, communicating through electrical signals from *synapses*, hence forming a Neural Network (NN). A neuron is activated when a strong signal is received by the dendrite through the synapse, propagating it through the axon and potentially activating another neuron in the network [18]. An overview of the structure and connections of a neuron can be seen in Fig. 2.1.

Figure 2.1: A schematic of the biological neuron

#### 2.2 Artificial Neural Networks

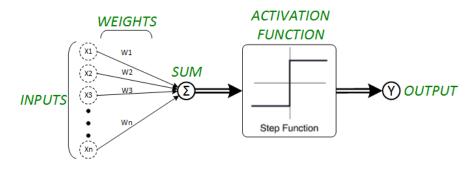

The operation and connections of a neuron can be logically modeled [19], thus producing an artificial neuron or combined together in an Artificial Neural Network (ANN). The model in Fig. 2.2 relates to the abstract biological model, containing a set of *inputs* as synapses, multiplied by the *weights* as the strength of the electrical signals, and combined in an weighted *sum* that goes to an *activation function*, representative of the threshold for activating the neuron. The computed *output* from the activation function relates to the signal propagating to the axon in the biological model.

Figure 2.2: A logical approach to the neuron: the artificial neuron

As before, the equal mathematical model is defined by the inputs  $X_i$ , the weights  $W_i$ and an activation function f (a step function in the original work [19]) resulting in the expression

$$Y = f(\sum_{i=1}^{n} W_i X_i)$$

(2.1)

where Y is the neuron output and n represents the number of input signals.

The weights value directly affects the output of the neuron given a said input. There is the possibility of changing these weights and thus obtain the desired output response, in a step by step process called learning or training.

#### 2.2.1 Perceptron

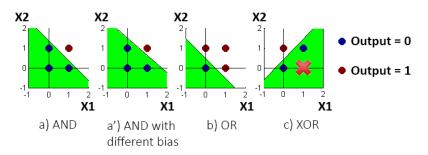

The first report on ANN training detailed a binary classifier, the perceptron, intended at mapping an input vector of real values to a binary output via a step activation function [20].

$$Y = f(b + \sum_{i=1}^{n} W_i x_i) = \begin{cases} 1 & \text{if } b + \sum_{i=1}^{n} W_i x_i > 0\\ 0 & otherwise \end{cases}$$

(2.2)

A bias b was introduced to provide a shift in the activation of the network output and more appropriately adjust the position of the decision boundary. The initial training algorithm does not distinguish input samples (vectors of input values) that are not linearly separable, causing some of them to be impossible to classify correctly as we can observe in Fig. 2.3. In a) and a') we can see a logical AND output correctly classified into two hyperplanes. The same happens in b) for the logical OR output, but for the logical XOR in c) a valid decision boundary cannot be set, always leaving at least one value out of the correct hyperplane.

Figure 2.3: A collection of logical operations responses, with associated decision boundaries and hyperplanes (green for 0, white for 1)

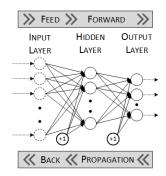

#### 2.2.2 Multi-Layer Perceptron

To solve the issue with the basic perceptron and its inability to correctly distinguish values that are not linearly separable, a new proposal was made in the form of the Multi-Layer Perceptron (MLP) [21]. The premise was that an added layer, the hidden layer between the input and output layers, could then perform a non-linear transformation via a sigmoidal function and thus obtain a linearly separable output space [22]. A new learn-ing algorithm was introduced, the error back propagation, computed after the data feeds forward through the network. A model of one of these MLPs, along with the direction of the feed forward and back propagation training phases, is depicted in Fig. 2.4.

Figure 2.4: A graphical representation of a Multi-layer Perceptron

The output signal is compared to the desired output and an error value and gradient is calculated for each of the output nodes. The error is then back propagated through the network, layer by layer, with the layer weights updated using a gradient descent algorithm. After the back propagation is concluded, a training iteration or epoch is over, and the process can start again from the feed forward, for as many epochs as needed until an ideal output error is achieved.

The use of more than two hidden layers in neural network supervised learning in what is called a Deep Neural Network (DNN), was seen as unnecessary until recently, given the proofs of the approximation capabilities of one [22] and two [23] hidden layer neural networks.

The exceptions to this rule were the neocognitron [24], which used several layers to emulate the human visual system, and Convolutional Neural Networks (CNNs) [25], both developed mostly for visual tasks.

Apart from the apparent unnecessary use of more than two layers, the other main issue with using deep networks was the difficulty that appeared when trying to train several hidden layers using standard back propagation: there were problems adjusting the weights as depth increased (vanishing gradients).

#### 2.3 State-of-the-Art: The Convolutional Neural Network

The efforts by Hinton and co-workers [26,27], resulted in the ability to train DNNs, in this case, Deep Belief Networks (DBNs) which took advantage of Boltzmann machines in a variant called Restricted Boltzmann Machines (RBMs). At the same time, other groups proposed a way to train deep networks based on stacking autoencoders [28,29].

From 2006 until today, the field of DNNs has received much attention. The potential advantages that come from using DNNs are the possibility of having increasingly more abstract levels of representation, the possibility of reusing the intermediate level representations across different tasks and also to obtain a more compact and efficient representation for certain types of problems [30].

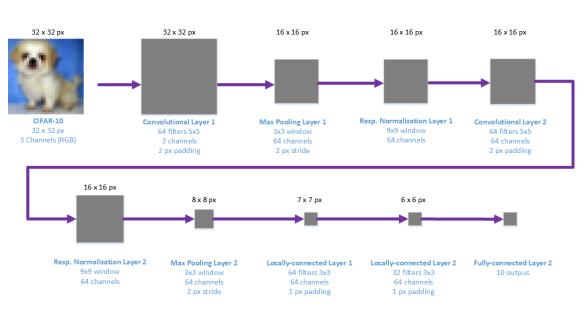

A novel form of DNN called CNN was then introduced, consisting in the simulation of how the brain's visual system works (or at least how we currently believe its first regions work). The CNN presented in [10] is in fact based on a combination of several individual CNNs, each applied to the same or different inputs and with the corresponding outputs combined and averaged.

This particular CNN presented the best results, by the time it was published, in 7 different datasets normally used for benchmarking similar algorithms, with improvements ranging from 30% to 80% with respect to previously best published results [10]. The main drawback of these approaches (CNNs) is their computational cost. These deep learning approaches use Graphics Processing Unit (GPU) clusters to cope with these large datasets [31]. But even using this type of powerful parallel computing engines, experi-

#### 2. Deep Learning using Neural Networks

Figure 2.5: Topology of the CNN for the CIFAR-10 dataset [1]

ments can still take several minutes or even hours to execute [10]. As an example, the LeNet convolutional neural network, working with the Mixed National Institute of Standards and Technology (MNIST) dataset takes 380min on a Central Processing Unit (CPU) (Core i7-2600K CPU at 3.40GHz) and 32min on a GPU (GeForce GTX 480) to run a single experiment (including training and testing) [32].

#### 2.4 Sub-optimal Neural Networks

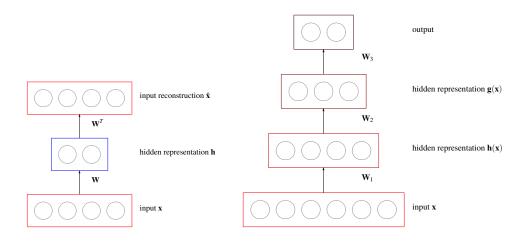

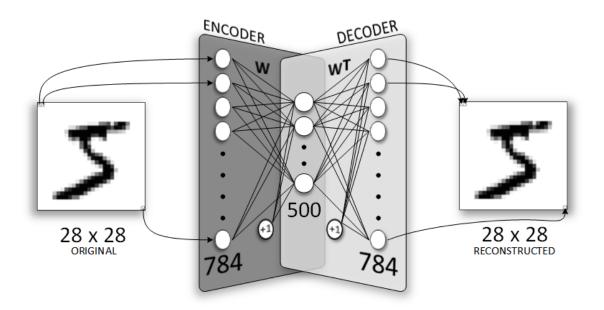

#### 2.4.1 Autoencoder

In this thesis we show the potential of implementing deep learning in Field-Programmable Gate Arrays (FPGAs) by using a Stacked Autoencoder (SAE). An Autoencoder (AE) consists of a simple network that tries to produce at the output what is presented at its input. The most basic AE is in fact an MLP that has one hidden and one output layer, with the following restrictions:

- The weight matrix of the last layer is the transposed of the weight matrix of the hidden layer (clamped weights);

- The number of output neurons is equal to the number of inputs.

Let's represent the input vector by  $\mathbf{x}$ , the weight matrix by  $\mathbf{W}$ , the input size by n. The hidden layer neurons output, called the encoding, is obtained with

$$h_j = s(a_j) \tag{2.3}$$

where

$$a_j = b_j + \sum_{i=1}^n W_{ij} x_i$$

(2.4)

and where  $b_j$  is the bias of the hidden layer neuron j and  $s(\cdot)$  is the sigmoid function. The output layer values, or the decoding, is given by

$$\hat{x}_j = s(\hat{a}_j) = s\left(c_j + \sum_{i=1}^{n_h} W_{ij}^T h_i\right)$$

(2.5)

where  $c_j$  is the bias of the output layer neuron j and  $n_h$  the number of hidden layer neurons.

A simplified way to write the previous expressions is

$$\mathbf{h} = s(\mathbf{a}) = s(\mathbf{b} + \mathbf{W}\mathbf{x}) \tag{2.6}$$

and

$$\hat{\mathbf{x}} = s(\hat{\mathbf{a}}) = s\left(\mathbf{c} + \mathbf{W}^T \mathbf{h}(\mathbf{x})\right)$$

(2.7)

where the sigmoid is applied to each element of its input (vector) argument.

Figure 2.6: Example of an autoencoder (left) and of a stacked autoencoder (right).

Since the goal is to obtain at the output the same thing that is in the input, an adequate cost function should compare these two vectors. The typical approach is to use (real-valued inputs)

$$C(\hat{\mathbf{x}}, \mathbf{x}) = \sum_{i=1}^{n} (\hat{x}_i - x_i)^2 .$$

(2.8)

For binary inputs, the cross-entropy can be used :

$$C(\hat{\mathbf{x}}, \mathbf{x}) = -\sum_{i=1}^{n} (x_i \log(\hat{x}_i) + (1 - x_i) \log(1 - \hat{x}_i))$$

(2.9)

Figure 2.7: Topology of the first autoencoder for the MNIST dataset

The weight changes will be done according to the gradient descent. Since the goal is to obtain in the output the same that is present in the input, an adequate cost function should compare these two vectors. In what follows, the index *i* runs from  $1, \ldots, n_h$  and the index  $j = 1, \ldots, n$ . For real-valued inputs, we use

$$C(\hat{\mathbf{x}}, \mathbf{x}) = \sum_{k=1}^{n} (\hat{x}_k - x_k)^2 .$$

(2.10)

When the activation function is the sigmoid, we have to update the weights (dropping constants that can be absorbed by  $\eta$ ) according to:

$$W_{ij} = W_{ij} - \eta \sum_{k=1}^{n} \left[ (\hat{x}_k - x_k) \hat{x}_k (1 - \hat{x}_k) \left( h_i + \sum_{z=1}^{n_h} \left[ W_{kz}^T h_z (1 - h_z) x_j \right] \right) \right]$$

$$b_i = b_i - \eta \sum_{k=1}^{n} \left[ (\hat{x}_k - x_k) \hat{x}_k (1 - \hat{x}_k) W_{ik} h_i (1 - h_i) \right]$$

$$c_j = c_j - \eta (\hat{x}_j - x_j) \hat{x}_j (1 - \hat{x}_j)$$

This process of adjusting the AE's weights in an unsupervised manner is called pretraining.

#### 2.4.2 Stacked Autoencoder

The process described so far is used to train a single AE, but a single AE is not deep: it only has depth 2. One possible way to obtain a deeper architecture using AEs is to stack them on top of each other such that the output of one AE is the input for the next. This stacking can produce a deep network: the stacked AE, or SAE.

Figure 2.8: Topology of the stacked autoencoder for the MNIST dataset

The SAE is obtained by the following procedure: first pre-train several AEs such that the first learns to approximate the inputs from the dataset, the second learns to approximate the hidden representations of the first and so on. Then place a final layer of neurons that represent the output layer and will have as many neurons as there are classes in the problem.

The idea is that the pre-training is used to bring the weights of the network near a good starting point for the fine-tuning procedure. Note that the pre-train is an unsupervised training procedure, whereas the fine-tunning that is performed on the complete SAE after the placement of the final layer is a typical supervised learning procedure that takes advantage of the class labels.

In the end, we obtain a deep network that receives input data from the dataset and produces a class label at the output.

#### 2.5 Softmax Classifier

The output layer of the SAE receives as input the last hidden layer representation produced by the AE on top of the stack, say **h**, and produces an output using the usual weighted product between the layer input (**h**) and its weights followed by the application of an activation function  $f(\cdot)$ .

The activation function used in this output layer can be any of several possibilities. We have chosen to use the softmax. So, for the activation of the output layer neuron i we get:

$$f(a_i) = \frac{e^{a_i}}{\sum_{k=1}^L e^{a_k}}$$

(2.11)

where *L* represents the number of classes (and output layer neurons) and  $a_i$  is the activation of neuron *i* obtained using an expression similar to (2.4) but where  $x_i$  are replaced by  $h_i$ .

#### 2.6 Neural Networks Hyper-parameters

#### 2.6.1 Learning Rate

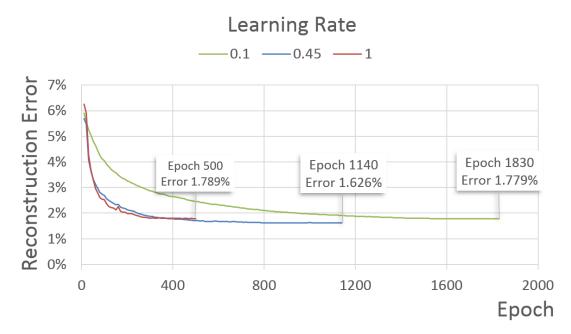

The learning rate selected at the start of the training phase is a high-impact parameter. If it's set too low, the resulting error convergence takes longer than necessary and the optimal final error may not be achieved, as the error may get 'stuck' on a local minimum. The opposite case, when the learning rate is set too high is also not ideal. With a value too high, as the first stages of training may present a faster error convergence, the error may start to diverge quickly, thus avoiding the targeted minimum. The ideal learning rate should be high enough to provide a rapid error convergence at the start, and then decrease to provide a finer rate and lower error in the end. An example of this problem can be observed in Figs. 2.9 and 2.10.

Figure 2.9: Impact of different learning rates. A low (0.1) learning rate gets caught in a local minimum (slow error convergence), an ideal (0.45) learning rate achieves the lowest possible error, and a high (1.0) learning rate goes past the ideal value (error divergence)

#### 2.6.2 Batch Size

During the training process an overall better performance and faster error convergence is obtained if we only present a small batch of images at each time. This problem size

Figure 2.10: Another example of the impact on the final result of a low (0.1), an ideal (0.45) and a high (1.0) learning rate

reduction dismisses the overhead impact of launching too many work-items in the device, at the same time decreasing the memory footprint of the application. Since the error verification and weight updates are computed at a quicker rate, the stopping criteria are achieved faster, thus improving the SAE training performance.

#### 2. Deep Learning using Neural Networks

# Hardware Parallelism with OpenCL Supported Architectures

Contents

| 3.1 | Desktop GPU | 18 |

|-----|-------------|----|

| 3.2 | Mobile GPU  | 20 |

| 3.3 | FPGA        | 22 |

#### 3.1 Desktop GPU

With the ubiquitous nature and power of currently available Graphics Processing Units (GPUs), there is high potential for computational acceleration. The trend in current GPU development is to provide the end user with an increased number of cores, benefiting the computational power and thus allowing more demanding applications to be addressed. The single-device GPUs in the gaming-driven market are headlined by the Advanced Micro Devices (AMD) R9 290X with 2816 Streaming Processors (SPs), and the Nvidia GTX Titan with 2668 Compute Unified Device Architecture (CUDA) cores. Their dual-GPU counterparts, the AMD R9 295X2 and Nvidia GTX Titan Z, are set to release with the double of SPs/CUDA cores and available memory.

#### 3.1.1 AMD R9 290X (Hawaii)

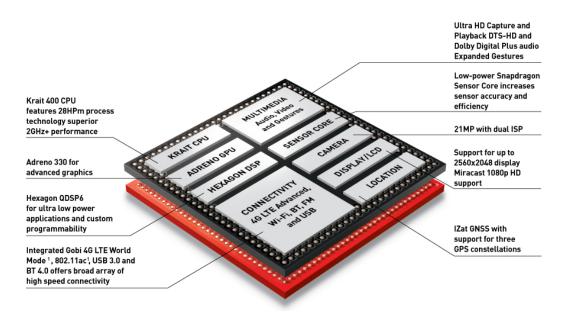

The AMD R9 290X GPU codename "Hawaii" was the first to be produced with AMD's own Graphics Core Next (GCN) version 2.0 architecture [33], with new takes on performance, image quality and energy efficiency. GCN 2.0 was designed with general-computing in mind and the increasing popularity of Open Computing Language (OpenCL) was considered during the development process.

The "Hawaii" block diagram in Fig. 3.1 details the integral GPU design [2]. At the top center of the design is the Graphics Command Processor, responsible for receiving the commands and state changes from the device's memory subsystem at the bottom of the diagram, and controlling the general flow of execution.

The memory subsystem is comprised of 1MB L2 Cache with 1TB/s L1/L2 bandwidth and capable of being partitioned into 16x64KB, and eight 64 bit Memory Controllers (MCs) resulting in the 512 bit bus interface to the 4 GB of GDDR5 memory, and 320 GB/s of memory bandwidth. Connecting to the host is the PCIe 3.0 Bus Interface with up to 15.75 GB/s for a 16-lane slot.

The GPU is intended to be a parallel computing platform and for maximum performance and less idle states, the Command Processor is aided by the 8 Asynchronous Compute Engines (ACEs) in this architecture. The ACEs perform in parallel with the Command Processor, independently managing the scheduling and workload dispatchment to each Compute Unit (CU) for processing.

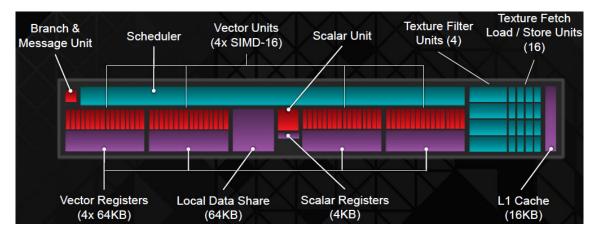

The computing core of the "Hawaii" GPU consists of 4 Shader Engines, each with its own parallel linked Geometry Processors and Rasterizers, but all sharing the same pool of 16x64KB L2 Cache. Each Shader Engine holds 11 CUs with 64 SPs each one, for a total of 44 CUs and a shader count of 2816 SPs. A more detailed view of a CU is depicted in Fig. 3.2.

| Clobal Data Share         Shader Engine       Shader Engine       Coomaty Processor       Coomaty Proc                                                                                                                                                                                                                                                                                                                                                                                                                     | ACE               | ACE                | ACE ACE       | Graphics Cor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | mmand Processor | ACE               | ACE       | ACE            | ACE          | Multimedia<br>Accelerators |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|-----------|----------------|--------------|----------------------------|

| Country Processor       Country Procesor       Country Processor       Cou | Giobal Data Share |                    |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                   |           |                | Accelerators |                            |

| Reserver       Reserver <td< td=""><td></td><td></td><td>Shader Engine</td><td></td><td>Shader Engine</td><td></td><td>Shader En</td><td>gine</td><td></td><td>VCE</td></td<>                                                                |                   |                    | Shader Engine |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Shader Engine   |                   | Shader En | gine           |              | VCE                        |

| L2 Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   | Geometry Processor | Ge            | ometry Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | G               | eometry Processor |           | Geometry Proce | essor        |                            |

| L2 Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8                 |                    |               | A CONTRACTOR OF A CONTRACTOR O | 8               |                   |           |                |              | UVD                        |

| L2 Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RB                |                    |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                   | RB        |                |              |                            |

| L2 Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |                    |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                   |           |                |              | TrueAudio                  |

| L2 Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | F 1               | CU                 |               | CU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 | CU                |           | CU             |              |                            |