João Filipe Marques Serra

# Multi-criticality Hypervisor for Automotive Domain

Master of Science in Electrical and Computer Engineering

July 2014

Universidade de Coimbra

Departamento de Engenharia Electrotécnica e de Computadores Faculdade de Ciências e Tecnologia Universidade de Coimbra

A Dissertation for Graduate Study in MSc Program Master of Science in Electrical and Computer Engineering

# Multi-criticality Hypervisor for Automotive Domain

### João Filipe Marques Serra

Work Developed Under Supervision of Prof. António Paulo Mendes Breda Dias Coimbra (DEEC-UC), Prof. Tony Richard de Oliveira de Almeida (DEEC-UC), Eng. Jorge Manuel Simões de Almeida (CSW)

Jury Prof. Jaime Batista dos Santos (President) Prof. António Paulo Mendes Breda Dias Coimbra (Vowel) Prof. Mário Gonçalo M. V. Silveirinha (Vowel)

Partially supported by the ARTEMIS-JU CONCERTO project (n.333053). Work developed at Critical Software S.A., Coimbra.

# Thanks

Never explain yourself. Your friends don't need it and your enemies won't believe it. (Belgicia Howell)

At the end of so important stage for me, I can not let pass this opportunity to thank all the people that helped and supported me over the last years.

Thus, I want to thank all the colleagues I have worked with, both during the course and in Critical Software and iTGROW. Without them, many battles would have been harder and less pleasant to pass by than they actually were.

Then I extend my warmest thanks to my coordinators, Prof. Paulo Coimbra, Prof. Tony de Almeida and Eng. Jorge Almeida, whose support has been crucial to the achievement of this work.

Finally, I leave my deepest gratitude to my family and my friends, who are the people that supported me everyday, in the good and bad moments.

# Abstract

It is wise to keep in mind that neither success nor failure is ever final. (Roger Babson, American educator)

xLuna is a real-time kernel technology that enables concurrent mixed-criticality applications running simultaneously on the same hardware platform, bridging a safety critical application, hard-real-time task set and certifiable real-time operating system alongside a feature rich, nonsecure, non-critical, non-real-time general purpose operating system.

The xLuna program, an hypervisor originally developed by Critical Software for space applications, has now a new development focused on the automotive domain extending the principles of its predecessor to new, multi-core hardware. To showcase this new approach, a certifiable real-time operating system is responsible to handle an eCall application, which is an European in-vehicle emergency call service, while running simultaneously with the general purpose operating system Android OS on the same hardware platform. This is done by sandboxing Android into a hardware enforced container. Space and time resource constrains are predefined, such as core affinity and static memory allocation.

The motivation of xLuna for automotive domain is to reduce the number of Electronic Control Units present in cars without reducing the number of features that they offer, by using a multi-core platform, allowing both critical and non-critical systems to run together in the same hardware platform.

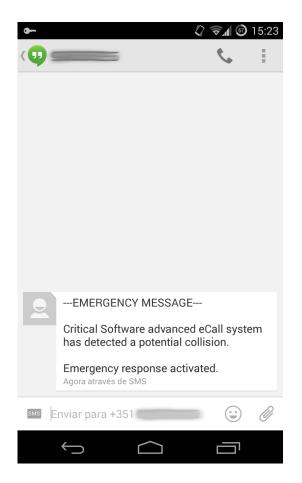

This work focused on the solutions presented by the hardware used, and how xLuna takes advantage of the technologies it brings to enforce software and resource partitioning. It was accomplished to have Android running simultaneously alongside the real-time operating system FreeRTOS, each one running on only one core. While Android is responsible to offer an automotive infotainment experience, one FreeRTOS's task is responsible to simulate the eCall system, sending a SMS to a pre-determined mobile phone number when high acceleration values are detected. The use of a modern multi-core platform running a mixed-criticality system is a emerging need for today's automotive domain. Integrating the eCall system with a system like this makes xLuna for automotive domain a great solution for this market.

**Keywords:** Embedded systems, mixed-criticality, multi-core, hypervisor, automotive, infotainment, eCall.

# Resumo

É sábio ter em mente que sucesso e fracasso nunca são definitivos. (Roger Babson, educador Americano)

xLuna é uma tecnologia de *kernel* de tempo-real que permite que aplicações com criticidade mista corram em simultâneo na mesma plataforma de *hardware*, juntando um sistema operativo de tempo-real certificável, contendo um conjunto de *tasks* de tempo-real rígido e aplicações de segurança crítica, com um sistema operativo não crítico, não seguro, rico em funcionalidades e que não é de tempo-real.

O programa do xLuna, um *hypervisor* originalmente desenvolvido pela Critical Software para aplicações destinadas para o espaço, tem agora uma nova abordagem focada no domínio automóvel, extendendo os princípios do seu antecessor para um novo *hardware* com um processador *multi-core*. Para dar a conhecer esta nova abordagem, um sistema operativo de tempo-real certificável é responsável por gerir uma aplicação eCall, que é um serviço de emergência europeu para veículos, enquanto que este corre simultaneamente com o sistema operativo Android na mesma plataforma. Isto é feito sendo o Android seguramente contido num *container* criado por auxílio do *hardware* presente na plataforma usada. Restrições aos recursos de tempo e de espaço são pré-definidas, tal como a afinidade aos *cores* do processador e a alocação da memória estática.

A motivação do xLuna para automóveis é reduzir o número de Unidades de Controlo Eletrónicas presentes nos automóveis sem reduzir as funcionalidades que elas oferecem, recorrendo à plataforma *multi-core*.

Este trabalho focou-se nas soluções fornecidas pelo *hardware* usado, e como o xLuna tira vantagem das tecnologias fornecidas para forçar o particionamento do *software* e dos recursos. Foi conseguido ter o Android a correr em simultâneo com o sistema operativo de tempo-real FreeRTOS, cada um deles a correr num só *core*. Enquanto que o Android é responsável por oferecer uma experiência rica em aplicações de multimédia, entertenimento e navegação, uma

*task* do FreeRTOS é responsável por simular o sistema eCall, enviando uma SMS para um destinatário pré-definido assim que são detectados elevados valores de aceleração.

O uso de uma plataforma *multi-core* moderna a correr um sistema de criticidade mista é uma necessidade emergente para o domínio automóvel dos dias de hoje. Integrando o sistema eCall com um sistema deste tipo torna o xLuna para automóveis uma excelente solução para este mercado.

**Palavras-chave:** Sistemas embebidos, criticidade mista, *multi-core, hypervisor*, automóvel, *infotainment*, eCall.

# Contents

| 1 | Intr | Introduction                          |    |  |  |  |  |  |  |

|---|------|---------------------------------------|----|--|--|--|--|--|--|

|   | 1.1  | Motivation                            | 2  |  |  |  |  |  |  |

|   | 1.2  | Objectives                            | 3  |  |  |  |  |  |  |

|   | 1.3  | Summary Of The Work Developed         | 3  |  |  |  |  |  |  |

|   | 1.4  | Structure Of The Thesis               | 4  |  |  |  |  |  |  |

| 2 | Tec  | chnical Background                    |    |  |  |  |  |  |  |

|   | 2.1  | Introduction of xLuna                 | 5  |  |  |  |  |  |  |

|   | 2.2  | xLuna Automotive Architecture         | 7  |  |  |  |  |  |  |

|   |      | 2.2.1 Initial architecture            | 7  |  |  |  |  |  |  |

|   |      | 2.2.2 QNX Neutrino RTOS               | 9  |  |  |  |  |  |  |

|   |      | 2.2.3 ARM TrustZone                   | 10 |  |  |  |  |  |  |

|   |      | 2.2.4 Final architecture              | 11 |  |  |  |  |  |  |

|   | 2.3  | eCall                                 | 12 |  |  |  |  |  |  |

|   | 2.4  | State of the art                      | 14 |  |  |  |  |  |  |

|   |      | 2.4.1 CONCERTO                        | 14 |  |  |  |  |  |  |

|   |      | 2.4.2 Existing competitors solutions  | 16 |  |  |  |  |  |  |

| 3 | Har  | dware, Software and Technologies Used | 27 |  |  |  |  |  |  |

|   | 3.1  | AUTOSAR                               | 27 |  |  |  |  |  |  |

|   | 3.2 | CAN F  | Protocol                                                                                                 | 28        |

|---|-----|--------|----------------------------------------------------------------------------------------------------------|-----------|

|   | 3.3 | Hardw  | are Used                                                                                                 | 28        |

|   |     | 3.3.1  | Freescale i.MX 6Quad                                                                                     | 28        |

|   |     | 3.3.2  | ARM TrustZone dedicated hardware                                                                         | 28        |

|   |     | 3.3.3  | FlexCAN                                                                                                  | 29        |

|   |     | 3.3.4  | IOMUX Controller                                                                                         | 29        |

|   |     | 3.3.5  | Universal Asynchronous Receiver/Transmitter                                                              | 29        |

|   |     | 3.3.6  | Join Test Action Group and Open On-Chip Debugger                                                         | 30        |

| 4 | Dev | elopme | ent and Implementation                                                                                   | <b>31</b> |

|   | 4.1 | Prepar | ation                                                                                                    | 31        |

|   |     | 4.1.1  | OpenOCD set-up for debugging via JTAG                                                                    | 31        |

|   |     | 4.1.2  | UART set-up for providing a console                                                                      | 32        |

|   | 4.2 | The Re | eal-time Operating System – FreeRTOS <sup>TM</sup> $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 33        |

|   |     | 4.2.1  | Vector table and exceptions handlers set-up                                                              | 33        |

|   |     | 4.2.2  | EPIT set-up for providing timer and tick capabilities to the OS $\ldots \ldots$                          | 34        |

|   |     | 4.2.3  | I2C (Inter-Integrated Circuit) and accelerometer set-up                                                  | 35        |

|   |     | 4.2.4  | USB drivers and stack                                                                                    | 36        |

|   |     | 4.2.5  | 3G USB modem set-up for sending a SMS                                                                    | 37        |

|   |     | 4.2.6  | FlexCAN module set-up                                                                                    | 38        |

|   |     | 4.2.7  | Develop a ring buffer for UART                                                                           | 39        |

|   |     | 4.2.8  | TZASC module set-up                                                                                      | 40        |

|   |     | 4.2.9  | Code conventions and comments                                                                            | 42        |

|   | 4.3 | The No | on Real-time Operating System – Android                                                                  | 42        |

|   |     | 4.3.1  | Modify Linux kernel source code to print via monicalls                                                   | 42        |

### 5 Results

|              | 5.1                             | xLuna Automotive's Prototype Demonstrations                        | 45  |  |  |  |  |  |

|--------------|---------------------------------|--------------------------------------------------------------------|-----|--|--|--|--|--|

|              | 5.2                             | FlexCAN Demonstration                                              | 48  |  |  |  |  |  |

| 6            | Con                             | Conclusions and Future Work                                        |     |  |  |  |  |  |

|              | 6.1                             | Conclusions                                                        | 51  |  |  |  |  |  |

|              | 6.2                             | Future Work                                                        | 53  |  |  |  |  |  |

| Re           | References                      |                                                                    |     |  |  |  |  |  |

| $\mathbf{A}$ | A Long lists and other material |                                                                    |     |  |  |  |  |  |

|              | A.1                             | AUTOSAR                                                            | 61  |  |  |  |  |  |

|              | A.2                             | CAN Protocol                                                       | 63  |  |  |  |  |  |

|              | A.3                             | Freescale i.MX 6Quad                                               | 64  |  |  |  |  |  |

|              | A.4                             | FlexCAN                                                            | 66  |  |  |  |  |  |

|              | A.5                             | IOMUX Controller                                                   | 67  |  |  |  |  |  |

|              | A.6                             | Universal Asynchronous Receiver/Transmitter                        | 68  |  |  |  |  |  |

|              | A.7                             | Tutorial to build Android                                          | 69  |  |  |  |  |  |

|              | A.8                             | Tutorial to develop an <i>Hello World!</i> application for Android | 74  |  |  |  |  |  |

|              | A.9                             | Tutorial to develop an <i>Hello World!</i> application for QNX     | 77  |  |  |  |  |  |

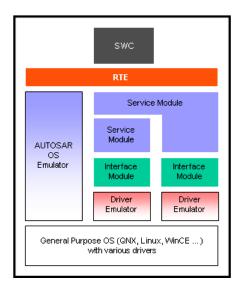

|              | A.10                            | AUTOSAR OS and RTE emulator research                               | 81  |  |  |  |  |  |

| •            |                                 | 1 1 1                                                              | 101 |  |  |  |  |  |

### Acronyms and symbols

# Chapter 1

# Introduction

If you have an apple and I have an apple and we exchange apples then you and I will still each have one apple. But if you have an idea and I have one idea and we exchange these ideas, then each of us will have two ideas. (George Bernard Shaw, Irish dramatist)

This dissertation is based on an internship in business environment, more specifically at Critical Software S.A. (CSW) through iTGROW A.C.E.. Firstly, I had to apply for it and after an interview, a few tests and group activities, I was chosen. The internship opportunity that I had applied for was for the Mars Robotic Exploration Preparation (MREP) project where I would have to develop and perform benchmarks to a microprocessor that will integrate a rover designed to explore Mars. Because of some problems unrelated to CSW, this project was delayed for almost a year. This situation forced CSW to change my internship plan. Nevertheless, I stayed a few weeks at CSW studying and researching on this subject.

The new internship subject was related with a new approach of a CSW's product, the xLuna (described is section 2.1). Initially, this new approach xLuna was supposed to be an hypervisor<sup>1</sup> of type 2 for automotive domain. It would run within a real-time operating system (RTOS),

<sup>&</sup>lt;sup>1</sup>Hypervisor is a piece of computer software, firmware or hardware that creates and runs virtual machines. They are classified into two types: type 1, which runs directly on the host's hardware to control the hardware and to manage guest operating systems, and type 2, which runs within a conventional operating system environment. More information please refer to [1].

responsible to handle the eCall system (described is section 2.3), and it would manage a guest operating system (OS), responsible for automotive infotainment<sup>2</sup>, both running simultaneously on the same multi-core hardware (HW) platform. These OSs were planned to be QNX® Neutrino® RTOS (section 2.2.2) and Android [2], respectively the RTOS and the guest OS. But after some work and research on the HW and on the OSs chosen, some initial ideas were dropped leading to the choice of a new RTOS, the FreeRTOS<sup>TM</sup> [3], and a change of type of hypervisor, now a type 1 hypervisor, for xLuna. In addition to this, xLuna also implements the eCall system. The first full working version of xLuna was accomplished at the end of last February. From that date on, the development team was reduced and those who stayed started working on new features and others details for better performance and security provided by xLuna.

This project allowed me to consolidate the knowledge acquired throughout the course by exploiting the concepts of operating systems and real-time operating systems to the limit.

In addition, this project was also very enriching for me regarding the first-job and team-work experience in the business environment but also regarding the automotive domain, which is a very interesting business area and that I will like to get involved into in the future.

### 1.1 Motivation

Nowadays, embedded systems are present everywhere. In cars, for example, there are dozens of ECUs (Electronic Control Units) that control one or more electronic safety systems, such as Antilock Braking System (ABS) or collision avoidance system, i.e., real-time safety critical systems. Now, with the introduction of in-car multimedia, navigation, web and social capabilities, the number of ECUs tends to increase even further, creating an ever growing need to reduce that number, minimizing production costs, cars' weight and energy consumption, without impacting performance, number of features offered and, above all, safety.

Multi-core processors can be a solution for that need, providing that systems with different safety integrity level (e.g., ABS and the Radio) do not coexist at the same processing unit. For this, it is necessary to isolate systems that would put human life at risk and, as such, have an higher level of certification requirements (such as ISO26262), from systems where a failure would

<sup>&</sup>lt;sup>2</sup>Automotive Infotainment, or In-Vehicle Infotainment (IVI), is a collection of hardware devices present in nowadays' cars, or other kinds of vehicles, to provide audio-visual entertainment and automotive navigation systems.

not pose any threat to safety (e.g., the multimedia system). This isolation is usually provided by containing the non-critical system through the use of an hypervisor, allowing both critical and non-critical systems to run together in the same hardware (HW) platform.

## 1.2 Objectives

My role in this project was to develop some device drivers, like UART (Universal Asynchronous Receiver/Transmitter) and FlexCAN (Flexible Controller Area Network), and to deal with interrupts, by mapping and handling them. Furthermore, I supported the others members of the project whenever they needed me to. These tasks required a lot of knowledge about computer science, C programming language and assembly, more specifically ARM®<sup>3</sup> assembly.

The objectives of this dissertation were based on the xLuna project unique milestone. This milestone was to have a demonstrator of xLuna, which would run Android on one core and FreeRTOS on another, and simulate an eCall application, ready to be presented at BMW Supplier Event 2014, in February 2014.

## **1.3 Summary Of The Work Developed**

At the beginning, it was written three tutorials – two that explained how to create an *Hello World!* application for both QNX and Android, and the other that explained how to build the Android source-code files. These tutorials are present in appendix (chapter A).

After that, when the development team of xLuna was complete, it started to be done the development and implementation of xLuna for automotive domain, in order to have the demonstrator ready for the milestone. This work included the development of the UART device drivers and the mapping and handling of the interrupts. The development of the device drivers of FlexCAN was done after the milestone, because this module did not entered in the demonstrator.

The work done by the others members of the development team had focused on the allocation of the static memory, the development of others device drivers and USB stack, etc. Apart from me and the *Project Manager*, the development team was composed by two senior engineers and

$<sup>^{3}</sup>$ ARM is a very popular family of computer processors based on a reduced instruction set computing (RISC) architecture. More information can be found in [4].

one junior engineer.

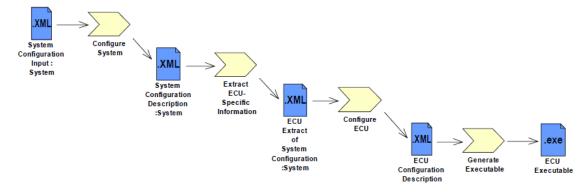

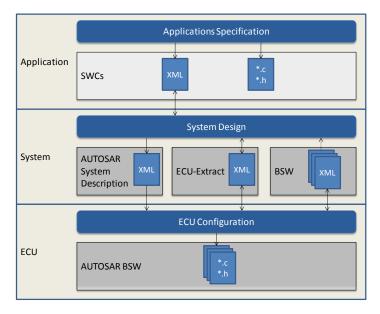

When the milestone was reached, a research work about AUTOSAR software architecture (described in section 3.1) started in order to study the integration of an AUTOSAR application in xLuna. A document that describes this study is presented in appendix (chapter A).

It was also written a paper about the xLuna for automotive domain (Multi-criticality Hypervisor for Automotive Domain). This article was submitted to INForum 2014, an event dedicated to Portuguese scientific works related with computer science. This paper is currently under evaluation.

## 1.4 Structure Of The Thesis

In addition to the current chapter, this document is split in five different chapters. They are the following:

- *Technical Background* it is described the architecture of the xLuna for automotive domain and the projects that are related with it, as well as a market research;

- *Hardware, Software and Technologies Used* in this chapter, the most relevant hardware, software and other technologies used in this work are properly detailed;

- Development and Implementation this chapter contains all the work done related with the development and implementation of xLuna, as well as the problems found and its solutions;

- Results in this chapter, it is showed the results of the work done in the latter chapter;

- *Conclusions* it is commented the results obtained and described what future work can be done.

# Chapter 2

# **Technical Background**

An investment in knowledge pays the best interest. (Benjamin Franklin)

In this chapter, it is described all the theory and background that supported the development and the implementation of xLuna Automotive, as well as the first xLuna architecture based on xLuna Space.

## 2.1 Introduction of xLuna

xLuna [5] is a real-time kernel technology that enables concurrent mixed-criticality applications running simultaneously on the same HW platform, bridging a safety critical application, hardreal-time (HRT) task set and certifiable RTOS, alongside a feature rich, non-secure, non-critical, non-real-time general purpose OS. The xLuna program, an hypervisor originally developed by CSW for space applications, has now a new development focused on automotive domain that extends the principles of its predecessor to new HW. In this new approach, the RTOS is responsible for simulating the eCall system, and it runs simultaneously with Android on the same platform, removing privileges of Android to access the memory space of the RTOS and splitting the cores of a multi-core processor to each OS.

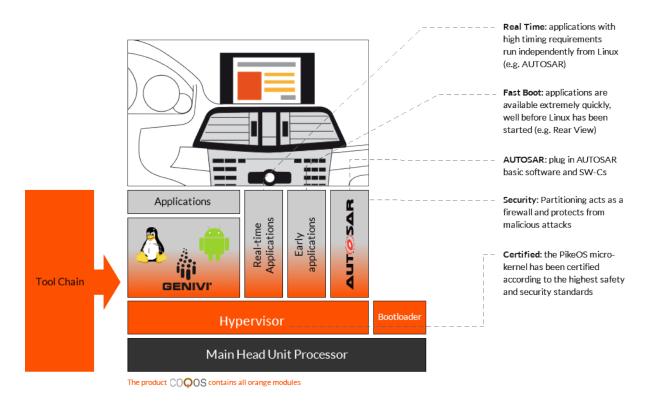

This new approach of xLuna consists on an hypervisor of type 1 with a small footprint and uses ARM TrustZone® technology (section 2.2.3) to integrate FreeRTOS with Android to run on a Freescale<sup>TM</sup>'s i.MX 6 Quad (section 3.3.1), an ARM Cortex<sup>TM</sup>-A9 [6] based system-onchip (SoC), platform. FreeRTOS is a free version of the certifiable RTOS<sup>1</sup> SAFERTOS® that provides HRT applications and interface with vehicle networks. Android brings a well-known platform for easier and faster application deployment as well as vendor supplied HW drivers for proprietary non-critical components, such as wireless communications, 3D graphics and sound interfaces, for a richer infotainment experience (Figure 2.1).

Figure 2.1: Preview of xLuna Automotive implementation in-car.

Furthermore, xLuna will hereafter implement an eCall application. eCall is a pan-European in-vehicle emergency call service based on 112, the common European Emergency number. It was created to improve the time response of emergency teams to car accidents all over European Union and it will be mandatory in all new cars commercialized in the European Union after October 2015 [7]. More information please refer to section 2.3.

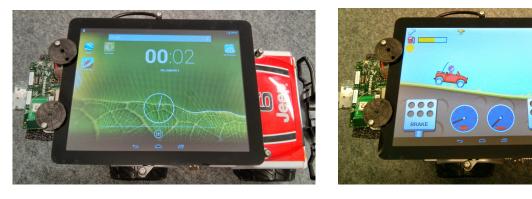

The first and only milestone of xLuna was to have a demonstrator ready to be presented at BMW Supplier Event 2014, in München, Germany, in February 2014. This demonstrator would run Android on one core and FreeRTOS on another, and simulate a car accident and the eCall system, by sending a SMS for a predetermined mobile phone number when high accelerations were detected by a 3-axis accelerometer. Figure 2.2 shows the CSW's stand dedicated to xLuna Automotive.

This work has been partially supported by the ARTEMIS-JU CONCERTO project (n.333053) (section 2.4.1). This project aims to create a reference multi-domain architectural framework for complex, highly concurrent and multi-core systems. The work developed in xLuna has the objective to implement one of the Run Time Environments for the CONCERTO modelling language.

<sup>&</sup>lt;sup>1</sup>A certifiable RTOS, in this case, it a RTOS that is pre-certified with safety and real-time standards.

Figure 2.2: Stand of xLuna Automotive in BMW Supplier Event 2014.

## 2.2 xLuna Automotive Architecture

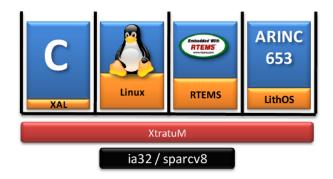

The xLuna Automotive emerged from the idea of applying the xLuna Space ideology to the automotive domain. In xLuna Space, the xLuna hypervisor places itself alongside the RTOS RTEMS<sup>2</sup> with the purpose to virtualize the well-known OS Linux, on an HW platform with a LEON2<sup>3</sup> processor.

### 2.2.1 Initial architecture

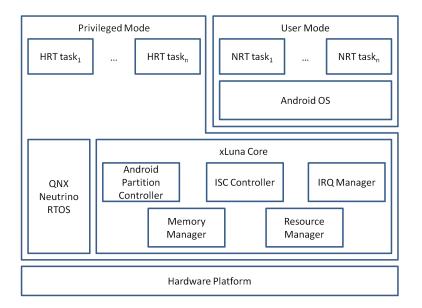

In the beginning, xLuna Automotive was supposed to have the same ideology of xLuna Space but with different OSs and HW – the QNX® Neutrino® RTOS (section 2.2.2) instead of RTEMS, Linux replaced by Android OS and, finally, the i.MX6Q processor instead of the LEON2.

<sup>&</sup>lt;sup>2</sup>The Real-Time Executive for Multiprocessor Systems (RTEMS) is an open source fully featured RTOS that supports a variety of open standard application programming interfaces and interface standards such as POSIX and BSD sockets [8].

<sup>&</sup>lt;sup>3</sup>LEON2 is a synthesisable VHDL model of a 32-bit processor compliant with the SPARC V8 architecture. The model is highly configurable, and particularly suitable for SoC designs [9].

Figure 2.3: xLuna Automotive based on xLuna Space.

In Figure 2.3, it is represented the xLuna Space architecture modified for this new approach of xLuna. With this architecture, xLuna could be classified as an hypervisor of type 2, because it would use the RTOS features in order to provide its own functionalities, so that Android could be virtualized inside a task of the RTOS. These functionalities would be implemented in xLuna core, which would be composed by five different modules. These modules are described below:

- Android Partition Controller the purpose of the Partition Controller would be to manage the partitioning service by using the needed QNX resources (like tasks) and by catching the needed interrupts to produce the necessary events to be delivered to Android;

- ISC (Inter-Systems Communication) Controller the ISC Controller would provide synchronous/asynchronous bi-directional communication between HRT tasks, in the QNX space, and NRT (Non-Real-Time) tasks, in the Android space;

- IRQ Manager the main purpose of the IRQ manager would be to process the interrupts from and to the Android kernel;

- Memory Manager this module's purpose would be to satisfy the requirements of memory protection between QNX and Android, between Android kernel and Android processes, and among Android processes;

- Resource Manager this module, which would be based on QNX's Resource Manager module, would allow the Android kernel to access additional hardware that would not be

managed neither by the Memory Manager module, neither by the Partition Controller.

This approach for the architecture of xLuna Automotive required more SW development and greater amount modifications in the RTOS kernel source code than the ideology adopted (section 2.2.4).

### 2.2.2 QNX Neutrino RTOS

QNX Neutrino RTOS [10] is a RTOS very used along the cars manufactures [11], which was the main reason why it was chosen to be the RTOS of the xLuna Automotive. As a micro-kernelbased OS, it is based on the idea of running most of the OS in the form of a number of small tasks. This allows developers to turn off any functionality they do not require without having to modify the OS itself – the tasks responsible for that functionalities simply will not run. In addition, QNX Neutrino RTOS is a message-passing-based OS, which means that the tasks communicate with each others through message-passing.

The QNX kernel only contains CPU scheduling, IPC (Inter-Process Communication), interruption redirection and timers, which means that everything else is done by user-space tasks. There is a special task within user-space task set known as proc(), which performs task creation and memory management by operating in conjunction with the kernel.

There is no device drivers in the kernel. In this case, the developers need to use QNX's Resource Manager (RM) module, whose goal is to present an abstract vision of some device. It consists on using standard POSIX<sup>4</sup> function calls that get translated to messages and then sent to RM.

QNX also allows the developers to create the interrupt handlers, or ISRs. The ISRs are a piece of code that determines what should happen when a specific interrupt is detected. They are called by the kernel and when they have finished, they tell the kernel what should it do by returning NULL if nothing is required to be done or an event otherwise. This event is then delivered to a new task.

Regarding the xLuna's approach considered until the time that this research was made, xLuna required a great amount of modifications in the RTOS source code in order to be possible to

<sup>&</sup>lt;sup>4</sup>POSIX (Portable Operating System Interface) defines the application programming interface, along with command line shells and utility interfaces, for software compatibility with variants of Unix and other OSs [12].

implement the xLuna core. What is described above allowed the xLuna's development team to understand that QNX could not allow that modifications to be done or even provide the features that xLuna needed.

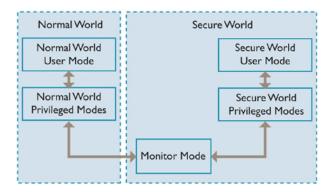

#### 2.2.3 ARM TrustZone

Nowadays, there is an emerging use of multi-core in every kind of embedded systems, such as smartphones, tablets, TVs, cars, etc.. These systems handle highly sensitive data or information, like banking credentials of theirs users, for example. In addition, they are also becoming open software (SW) platforms that allow users to download and use third-party applications that can put these devices, and the data that are handled by these, in risk. In order to a device like these become a secure open SW platform, both HW and SW must work together to robustly secure the device from different types of attack.

The ARM TrustZone technology [13], which is present in ARM Cortex-A series processors, was developed to accomplish this security need. It provides the ability to create two environments or worlds, as referred in TrustZone terminology, with different privileges – the secure world and the normal world – providing a new HW assisted SW separation solution, splitting the already existing privileged/unprivileged domains (Figure 2.4).

Figure 2.4: TrustZone technology architecture [13].

TrustZone also avoids the performance penalty of a world switch every time an exception occurs in a different context of its destination world because each world contains its own exception handlers. The world switching is done by a CPU exception mode called *monitor*. This mode is entered by calling ARMv7A 'smc' (Secure Monitor Call) instruction. This instruction can be called from either the secure or normal worlds or by a secure IRQ (Interrupt Request)/FIQ (Fast

IRQ)<sup>5</sup> that would require a world switch by saving the current world context and restoring the context of the other world.

Contextualizing TrustZone into the xLuna's ideology, the development team noticed that TrustZone could have a major role on xLuna Automotive, because it can provide almost all of the features of the xLuna core modules.

### 2.2.4 Final architecture

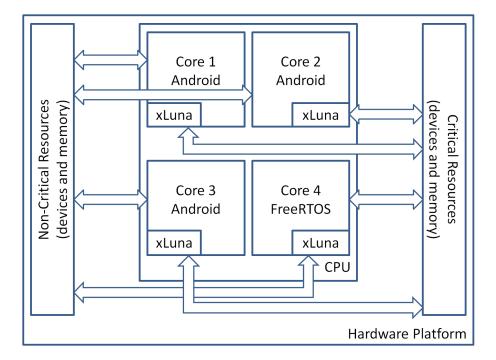

Regarding sections 2.2.1, 2.2.2 and 2.2.3, it was decided to drop the idea for the xLuna Automotive architecture and the RTOS. Thus, xLuna is now using ARM TrustZone and an open-source RTOS. It was chosen the FreeRTOS because of its simplicity and, consequently, the fact that it is a certifiable RTOS. Therefrom, Figure 2.5 depicts the final architecture of the xLuna Automotive.

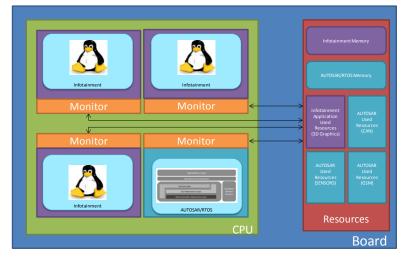

Figure 2.5: xLuna hypervisor implementation on a multi-core hardware platform.

xLuna thrives from TrustZone technology (section 2.2.3) placing itself in the monitor exception routines. It manages a fast, secure and certifiable entry point enabling non-critical SW to be sandboxed<sup>6</sup> into this HW enforced container, while ensuring the safety-critical environment has

<sup>&</sup>lt;sup>5</sup>An FIQ is a feature of the modern ARM processors and it consists on an higher priority interrupt request. It is prioritized by disabling IRQ and other FIQ handlers during request servicing.

<sup>&</sup>lt;sup>6</sup>In computer security, a Sandbox is a security mechanism for separating running programs. It is often used to execute untested code, or untrusted programs from unverified third-parties, suppliers, untrusted users and

no impact whatsoever. The fact of being an HW implemented container makes the SW required for managing this container substantially less than other virtualization options. Regarding that, xLuna can be easily converted into a certifiable solution while avoiding any performance penalties of SW emulations.

In order to manage the context switch and to pass the control from one world to the other, a secure Application Programming Interface (API) provides system calls, or monicalls (Monitor Calls) as referred in xLuna terminology, with a specific register set to pass as arguments. Setting these registers, followed by the 'smc' instruction, will make the current core to jump to the monitor exception handler where xLuna will then securely switch that core from non-secure to secure worlds and call the corresponding handling code to process the requested monicall and arguments.

xLuna also implements an Inter-Core Communication (ICC) mechanism that allows the secure SW to perform a secure request to a target core. It can for example stop/halt the non-secure SW in the target core specified by sending a call to that core.

As it is shown in Figure 2.5, in xLuna Automotive three cores of the processor are dedicated to Android and the fourth is dedicated to FreeRTOS. This attribution was made due the fact that Android needs more computation resources than FreeRTOS. It can be changed any time by using xLuna's ICC to stop an Android core and then to start it again dedicated to FreeRTOS. Memory is also split into two regions – a larger one for Android and the other for FreeRTOS.

### 2.3 eCall

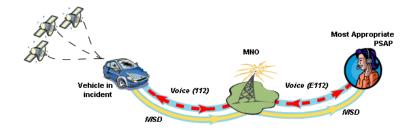

eCall is an electronic safety system that calls automatically the emergency services in case of a serious car accident, which is going to work all over the European Union (EU) plus Iceland, Norway and Switzerland.

An eCall event can be triggered automatically, when a car accident happens, or manually by simply pushing a button. Then, it is immediately established an 112 emergency call to the nearest emergency centre, Public-Safety Answering Point (PSAP) (Figure 2.6). It is also transmitted a Minimum-Set-of-Data (MSD) message over IP to that centre containing the geographic coordinates of the accident scene, the time of the occurrence, vehicle description, and others

untrusted websites [14].

eCall details, such as message ID, the trigger mode, etc.

Figure 2.6: eCall system [15].

There are three participants involved in an eCall event – the car, the Mobile Network Operator (MNO) and the PSAP. Each one of them has to be prepared to support the eCall system by following a set of standards. So, xLuna will need to follow the standards dedicated to the cars' manufacturers – CEN EN 15722, 16072 and 16062.

The general benefits of eCall are the following:

- Faster response to the rescue;

- Faster implementation of the Traffic Incident Management process;

- Reductions in secondary incidents;

- More accurate information;

- Increased information for first responders provided by the MSD.

Furthermore, eCall will also result in faster treatment of injured people, by giving accident victims better recovery prospects. In financial terms, every year the EU's economic loss caused by road accidents amounts to more than  $\in 160$  billion, but if all cars were equipped with the eCall system, up to  $\in 20$  billion could be subtracted to that value [16].

In numbers, it is expected that eCall saves several hundred lives in the EU each year by reducing emergency services' response time by 50% in rural and 40% in urban areas [16].

eCall system is developed by the HeERO (Harmonised eCall European Pilot) project. Its main objective is to prepare for the deployment of the necessary infrastructure in Europe with the aim of making the eCall a reality. This project, which is partially funded by the European Commission, was divided in two phases – HeERO 1 and HeERO 2. The first lasted for three

years, from January 2011 to December 2013, and it was composed by a nine European countries consortium. The second phase is currently on going and it is composed by six new countries plus the other nine pilot countries of HeERO 1. For more information, please refer to [17].

All EU member states are invited to be represented at the European eCall Implementation Platform (EeIP) in order to report on their national status of eCall deployment. Portugal entered the eCall pan-European project in 18 September 2007 [18]. In January 2011, it was created a implementation platform for eCall system in Portugal (PIeCall.pt) but apparently it was dropped because it could not be found any more information about it since its creation. Portugal did not entered in HeERO 1 neither in HeERO 2.

For more information about eCall, please refer to [15].

### 2.4 State of the art

This section will present and contextualize the other project related with xLuna. Furthermore, it will be listed and analysed the concurrence of xLuna, specially in automotive domain, and their main features. It will be also discussed the entrance of xLuna in the market and its strengths and weaknesses.

### 2.4.1 CONCERTO

As mentioned in sections 1.1 and 2.2.3, embedded systems are present everywhere and they are starting to use processors with a multi-core architecture. This kind of architecture can have a very important rule in the future of safety-critical real-time systems. To make it possible, across-the-board advances are demanded in all areas of design and development. CONCERTO will combine component-based design with model-driven development in order to deliver a reference multi-domain architectural framework for these systems, without compromising real-time, dependability and energy consumption restrictions.

CONCERTO (Content and cOntext aware delivery for iNteraCtive multimEdia healthcaRe applicaTiOns) is an European project partially funded by the ARTEMIS Joint Undertaking and composed by a European consortium. It aims to improve Model Driven Engineering<sup>7</sup> practices

<sup>&</sup>lt;sup>7</sup>Model-Driven Engineering (MDE) is a software development methodology which focuses on creating and exploiting domain models, rather than on the computing concepts. For more information, please refer to [19].

and technologies for embedded systems. It consists on the creation of a framework to elevate the abstraction of increasing embedded systems complexity in automotive, aerospace, medical, petroleum and telecom domains. This can be done by following the next three aspects:

- Providing reference designs and architecture to enable a compositional approach to system construction for high performance multi-core platforms with monitoring at run-time;

- Providing a modelling framework developed to support a multi-view, hierarchical design space, with incremental development and early verification of extra-functional properties;

- Developing computing platforms for embedded systems to increase cross-domain reuse and interoperation through platform-independent compositional development of highly concurrent, complex multi-core systems.

The big impact of CONCERTO in the market is to provide the above mentioned capabilities to enable SW developers to take advantage of the power of newer and more advanced HW platforms without substantial increases on the complexity of system design. Therefore, European technology providers will benefit from reduced time-to-market despite the increasing contribution of embedded systems and SW and their increasing size and complexity. Advanced HW modelling capabilities to capture the full potential of new multi-core platforms will also increase the quality and reliability of European embedded systems based products and services, as well as they will provide new and innovative functionalities for the user, while providing tools to ensure high quality and highly reliable systems.

The main focus of CSW in CONCERTO project is to research on the extension of CON-CERTO to the automotive domain, in particular to study the use of hypervisors for mixedcriticality multi-core systems. Regarding these, CSW will leverage on knowledge obtained in the aerospace domain and re-apply it to the automotive market. In addition, the development of a small demonstrator for a use case related to the automotive domain is also responsibility of CONCERTO's partners that have strong automotive domain experience, which includes CSW. This use case will encompass infotainment systems and safety-critical functionalities in the same ECU, in order to demonstrate the possibilities of having mixed-criticality environments running simultaneously on the same HW platform without interferences.

For more information about CONCERTO, please refer to [20].

### 2.4.2 Existing competitors solutions

In this subsection it is presented a market analysis of multi-core virtualization solutions, with a greater focus on the automotive related ones. The main goal of this analysis is to compare xLuna Automotive with its competitors in order to know what are its advantages and disadvantages.

#### **Continental Higher System Integration**

This product was developed by Continental, together with Sysgo Continental, aiming to integrate vehicle systems with multimedia applications, mobile entertainment technology, internet and cloud computing in a single vehicle domain. This product consists on an hypervisor that control different SW worlds, like AUTOSAR systems, GENIVI<sup>8</sup> or/and Android applications, running together on only one HW platform. To do this, these worlds are distributed into several virtual machines (VMs) and the hypervisor manages the resources requested by these VMs.

Figure 2.7: Continental and SYSGO integrate vehicle control electronics for instrument clusters and infotainment [22].

The increasing number of ECUs in today's cars is an aspect that was taken in to count <sup>8</sup>The GENIVI Alliance is a non-profit automotive industry alliance committed to driving the broad adoption of an In-Vehicle Infotainment (IVI) open-source development platform. The GENIVI Alliance was founded on March 2, 2009 by BMW Group, Delphi, GM, Intel, Magneti-Marelli, PSA Peugeot Citroen, Visteon, and Wind River Systems [21]. by this partnership. Regarding that, it is also wanted to display every different, but relevant information, of all the ECUs present in the car using a user-friendly interface as well as all the GENIVI and/or Android applications in different screens, such as in the instrument cluster or in the middle console display.

Figure 2.8: Integration via multi-core-hardware and Hypervisor [22].

To accomplish these, it is generated three VMs on a multi-core processor, which means that three SW technologies can run in parallel but completely independent for each other.

### **COQOS** Operating System

This product was developed by OpenSynergy to provide user-friendly applications, internet and other infotainment funcionalities to the user without compromising the real-time/automotive requirements. The COQOS OS is composed by an hypervisor, which is based on the certified PikeOS micro-kernel, a Linux based OS to run the infotainment applications, AUTOSAR, which will run independently from Linux, and a bootloader.

According to COQOS's website, its benefits are:

- Possibility to run on compact microprocessors as well as high-performance multi-core processors;

- Assign different partitions to one core or several cores to one partition;

- Hypervisor certified with the highest requirements in terms of safety and security;

- Isolation between guest OSs;

- Integrating AUTOSAR seamlessly;

- Reduce time-to-market and low costs.

Figure 2.9: System containing COQOS OS [23].

#### Evidence® open-source platform for automotive systems

This solution developed by Evidence combines Linux for human-machine interactions and a reliable certified RTOS based on OSEK developed by Erika Enterprise, specifically designed for automotive and industrial control, to run on the same multi-core processor. The hard real-time requirements are guaranteed by running control on a dedicated core, and the safety of the access to shared data is accomplished using mutual exclusion mechanisms. This solution was presented in Edinburgh at Automotive Linux Summit event, that occurred last October, where a demo running on a Freescale i.MX6 multi-core ARM SoC proved the feasibility and effectiveness of it.

A presentation of this solution can be found in [24].

#### fentISS XtratuM

XtratuM is a secure, reliable and efficient hypervisor created to enter the markets of aerospace, aeronautics, automotive and transportation and more, by Fent Innovative Software Solutions S.L.. This hypervisor provides a framework to run several OSs in a partitioned environment and it can be used to build a multiple independent levels of security, always meeting safety critical real-time requirements. It supports four different processor architectures, such as ARM and x86, and its main features are:

- Para-virtualization technology;

- Designed to have a small footprint;

- Multi-plan support;

- Advanced monitoring and error reporting;

- Configuration and validation tool available;

- ARINC-653<sup>9</sup> flavour;

- Smart I/O multi/demultiplexing.

Figure 2.10: XtratuM partitions and execution environments [26].

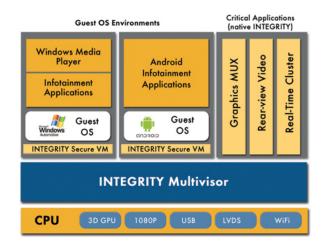

#### Green Hills Software's INTEGRITY® Multivisor

INTEGRITY Multivisor was developed to consolidate disparate systems onto dedicated VMs running on the same platform. This means one HW platform can host arbitrary guest OS alongside a suite of real-time applications and they are flexibly scheduled across one or multiple cores. When available, INTEGRITY Multivisor will use the processor's hypervisor mode assistance to minimize modifications to guest OSs. Otherwise, intrusive modifications to the guest OS will

<sup>&</sup>lt;sup>9</sup>ARINC 653 (Avionics Application Standard Software Interface) is a software specification for space and time partitioning in safety-critical avionics real-time OSs [25].

be the minimum as possible to maximize performance without sacrificing ease of migration and portability.

Figure 2.11: Virtualization architecture for Android infotainment systems [27].

The benefits of using INTEGRITY Multivisor as referred in Green Hills Software's website are, besides those in common with this kind of products:

- HW consolidation that decreases production costs;

- The ease of porting OSs to new HW gets faster time-to-market products;

- Better time-in-market by reusing legacy OSs and SW;

- Eliminating the need to port existing applications to new OSs;

- Hypervisor power management that turns this product a green one;

- EAL6<sup>10</sup> plus High Robustness-certified OS technology.

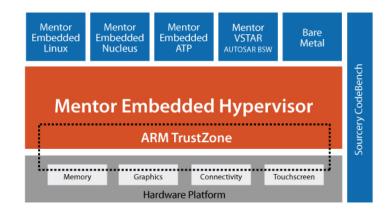

#### Mentor Embedded Hypervisor

This is a product developed by Mentor Graphics<sup>®</sup> and it consists on an hypervisor of type 1, with a small footprint and high performance, which uses the ARM TrustZone to control HW access and supports several OSs including the Linux distribution Yocto, Android, Mentor's Automotive

<sup>&</sup>lt;sup>10</sup>The Evaluation Assurance Level (EAL1 through EAL7) of an IT product or system is a numerical grade assigned following the completion of a Common Criteria security evaluation, an international standard in effect since 1999. The increasing assurance levels reflect added assurance requirements that must be met to achieve Common Criteria certification [28].

Technology Platform, Nucleus RTOS and AUTOSAR. According to Mentor Graphics<sup>®</sup>, this hypervisor has the following key benefits for developers:

- Build secure and high-performance embedded systems at the highest privilege level in a system;

- Reduce test and debug times by consolidating multiple functions on a single multi-core platform;

- Take advantage of asymmetric multiprocessing (AMP) and symmetric multiprocessing (SMP), or a combination of both, to provide flexible scheduling algorithm that allows for a single Virtual Machine (VM) to run on a multiple cores, or a multiple VMs to run on a single core or multiple VMs to run on multiple cores;

- Partition memory and devices to prevent unauthorized access to sensitive resources;

- Support for ARM TrustZone secure system architecture that allows normal and secure applications to run within the same embedded system.

Figure 2.12: Mentor Embedded Hypervisor architecture [29].

A video of Mentor Embedded Hypervisor demonstrator can be seen in [30].

#### NI Real-Time Hypervisor

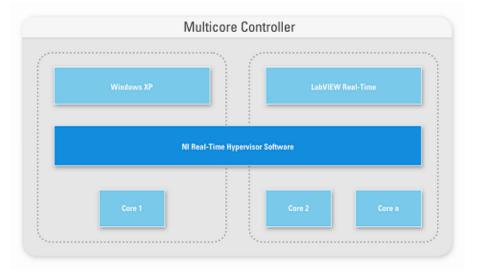

This is a National Instruments product and it has two different versions: one version that runs on a single multi-core PXI and other versions that runs on an industrial controller. The NI Real-Time Hypervisor uses virtualization to run both LabVIEW Real-Time and either Windows XP or Red Hat Enterprise Linux OSSs simultaneously in parallel on a single processor.

Figure 2.13: NI Real-Time Hypervisor for Windows SW runs Windows XP on one or more processor cores and LabVIEW Real-Time on the remaining cores [31].

The NI Real-Time Hypervisor is a bare-metal hypervisor which means that it is a virtualization SW package that runs immediately on the HW platform. Actually it can be divided into two SW packages: one where the host OS is Windows and other where the host OS is Linux. The NI Real-Time Hypervisor partitions I/O devices, RAM and CPU cores between OSs. Regarding that, when one of the OSs tries to access to shared resources or to the resources of the other OS, the hypervisor is automatically called to manage and control that access. This hypervisor also has a SW utility called NI Real-Time Hypervisor Manager that allows the user to assign individual I/O devices, RAM and CPU cores to either LabVIEW Real-Time or the host OS.

#### Red Bend's vLogix Mobile®

As the latter, this is also a type 1 hypervisor that runs directly on HW and schedules access to shared platform services by partitioning and allocating RAM and flash memory, for example, and separating VMs from one another. Virtual devices is a concept regarded in vLogix Mobile, and by this it is intended to say that devices, such as Wi-Fi, GPS and the screen, are virtualized so that the guest OSs can have access to a virtual view of them without being able to access them physically.

Some of the benefits announced by Red Ben of the vLogix Mobile are:

- Achieve faster time-to-market at lower costs;

- Porting capabilities;

- A optional module that provides absolute separation between VMs;

- A small footprint hypervisor (about 40000 lines of code);

- Pre-integrated with Android and available for multiple platforms for fast deployment.

This hypervisor was already integrated to a system for automotive purposes. Red Bend, Texas Instruments, QNX and Crack joined to create a demo (Figure 2.14) that illustrates a solution of virtualization to the automotive domain. This demo was composed by TI's Jacinto 6 board, QNX CAR Platform for infotainment, a QNX Neutrino RTOS based instrument cluster developed by Crank Software's Storyboard<sup>TM</sup> Suite, and vLogix Mobile. This demo was presented in the International CES of 2014.

Figure 2.14: Demonstrator of the Red Bend, Texas Instruments, QNX and Crack joint [32].

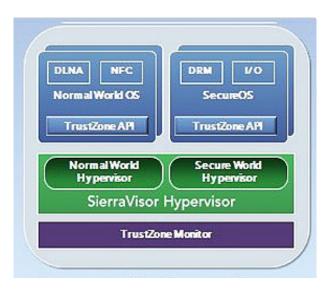

#### SierraVisor Hypervisor

This Sierraware product is another hypervisor based on ARM architecture and, consequently, ARM TrustZone. It allows multiple OSs and RTOSs to run on a single multi-core processor in parallel using para-virtualization and full HW virtualization. Regarding the para-virtualization, it is inserted into the guest OSs non-intrusive hypercalls to minimize the modifications on them and the impact on performance, but also to allow the access to the secure OS for specific secure functionalities and data. The SierraVisor Hypervisor also provides both AMP and SMP for managing system utilization.

Figure 2.15: SierraVisor architecture diagram [33].

Besides the hypervisor, Sierraware also provides a utility that brings to equipment manufacturers the possibility to choose the right solution for their virtualization requirements and target architecture called SierraVisor Hypervisor Development Toolkit.

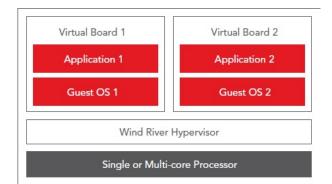

#### Wind River Hypervisor 2.0

The Wind River Hypervisor 2.0 is a type 1 hypervisor that was built for low latency, determinism and multi-core performance in the smallest footprint possible. It aims to consolidate multiple applications onto the same multi-core platform to increase capacity and reduce the size, weight, power and cost of embedded systems. It uses Wind River's VxWorks® to obtain a secure partition capability designed to separate applications of different levels of criticality in critical systems. Wind River Hypervisor supports six different processor architectures (Intel® Core<sup>TM</sup>, Intel Xeon®, Intel Atom<sup>TM</sup>, PowerPC e500 and e500mc, and ARM Cortex<sup>TM</sup>-A9) and any OS that will be integrated with VxWorks and Wind River Linux.

The main features of this product according to Wind River are:

- Consolidate multi-criticality applications by, at the same time, complying with safety and security regulations;

- Meet real-time performance requirements even with non real-time applications running on

the same platform by using multiple OSs on multi-core processors supporting SMP and AMP;

• Migrate legacy SW with minimal requesting by isolating legacy applications into a single virtualized partition.

Figure 2.16: Virtualized system with Wind River Hypervisor 2.0 [34].

A video of Wind River Hypervisor 2.0 demonstrator can be seen in [35].

#### Summary

Comparing all the competitors of xLuna with xLuna itself, it can be said that xLuna and the existing solutions more related with the automotive domain are very similar. Almost all of them consist on an hypervisor of type 1 and introduce a multi-core processor solution, exactly as xLuna.

The use of ARM TrustZone technology is not so usual, but it seems to be the best approach to ensure that a non-critical system is sandboxed successfully, which means that the non-critical system does not impact the performance of the critical-real-time system. Considering this, only two competitors are at the same level of xLuna Automotive regarding the security of the whole system – Mentor Embedded Hypervisor and SierraVisor Hypervisor. Just note that the SierraVisor Hypervisor is not so focused in the automotive domain than Mentor Embedded Hypervisor and xLuna Automotive.

The fact of the xLuna's RTOS, the FreeRTOS, be a certifiable RTOS is also an advantage. There are competitors that also mention this feature, but not all of them.

In addition to this, xLuna Automotive will have implemented an eCall application, which,

being eCall mandatory in all new cars commercialized in the European Union after October 2015, is a great advantage of xLuna when compared with its competitors.

The disadvantages that can be found when comparing xLuna with its competitors are mainly the lack of OS porting capabilities and the fact that xLuna Automotive does not support the AUTOSAR SW architecture. But in both cases, these are only disadvantages depending on the client, i.e., only if the client requires a different OS or support to AUTOSAR, the two disadvantages mentioned can be considered as that.

Concluding, xLuna Automotive has the potential to be on top of the market of the automotive multi-core automotive infotainment systems.

## Chapter 3

# Hardware, Software and Technologies Used

Make no little plans: they have no magic to stir men's blood... Make big plans: aim high in hope and work. (Daniel Burnham, American architect)

In this chapter it will be mentioned the hardware, the software and technologies that had contributed significantly to the work developed. It will be detailed the ones which had specific and important features for this work.

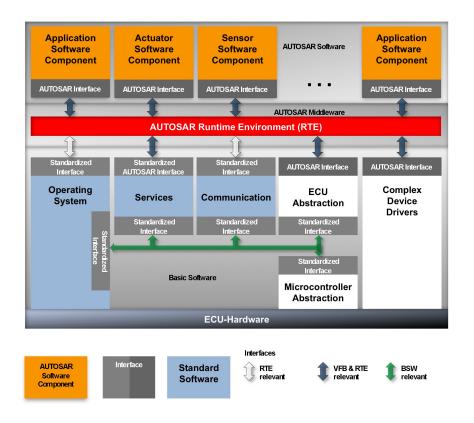

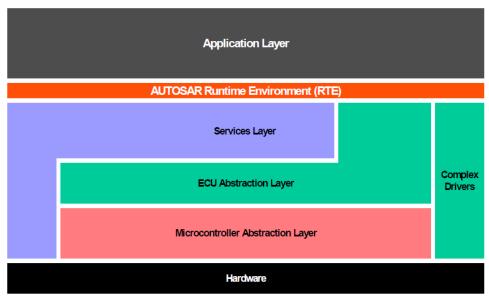

### 3.1 AUTOSAR

With the increasing complexity of automotive applications, a group of automotive industry  $OEMs^1$  created a joint group in order to develop and establish an open industry standard for automotive Electrics/Electronics (E/E) architecture. This joint group was created in 2012 and it is called AUTOSAR (AUTomotive Open System ARchitecture).

For more information related to AUTOSAR, please refer to section A.1.

<sup>&</sup>lt;sup>1</sup>An Original Equipment Manufacturer (OEM) manufactures products or components that are purchased by another company and retailed under that purchasing company's brand name. More information can be found in [36].

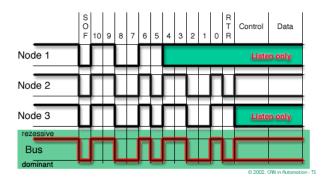

### 3.2 CAN Protocol

CAN protocol is a vehicle bus protocol designed to allow different ECUs to communicate with each other without the control of an host computer and meeting the specific requirements of the automotive domain: real-time processing, required bandwidth, reliable operation in the EMI environment and cost-effectiveness.

For more information about CAN protocol, please refer to section A.2.

#### 3.3 Hardware Used

In this section, it is presented the HW used in this work.

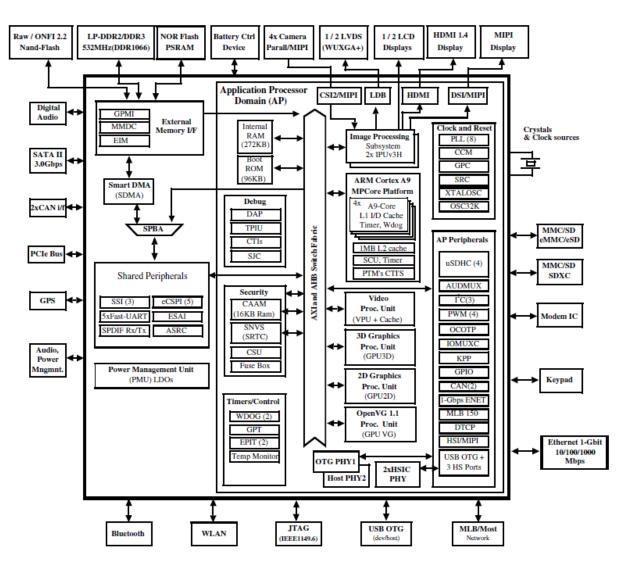

#### 3.3.1 Freescale i.MX 6Quad

As mentioned in section 2.1, xLuna Automotive uses a multi-core SoC – the Freescale i.MX 6Quad processor [37].

For more information about i.MX 6Quad processors, please refer to section A.3.

#### 3.3.2 ARM TrustZone dedicated hardware

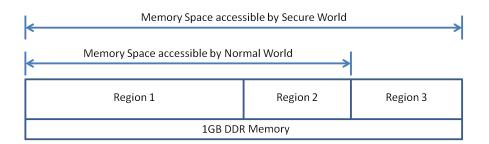

Regarding the TrustZone technology, the ARM Cortex-A9 processors introduce a set of devices that brings support to what was described in section 2.2.3. These devices – TrustZone Address Space Controller (TZASC), Central Security Unit (CSU) and Secure Generic Interrupt Controller (GIC) – are aware of the access requesting world and so they can provide a set of specific functionalities that allows to create a safer and more secure container.

The TZASC device enables to configure the system memory up to 16 regions. Each region can be configured as read-only (RO), write-only (WO) or read-write (RW) to each world, in order to ensure secure memory access. In case of unauthorized access, either read or write, the transaction is denied, a secure IRQ is triggered and the interrupt handler, or interrupt service routine (ISR), is called to handle the situation.

The security enhanced GIC provides the capability to secure interrupts by blocking any configuration attempts from normal world SW, as well as the possibility to configure a secure interrupt to trigger a FIQ, instead of normal IRQ, that would jump to monitor mode.

The CSU controls the access to bus masters and slaves that are not aware of the currently running world, e.g., the CAN (Controller Area Network) bus interface device, the GPU or the USB. This controller sets what devices are authorized to be accessed by each world and, when an unauthorized access is detected, a secure interrupt is triggered calling the respective ISR to give back control to the secure world SW.

In addition to the latter devices, the TrustZone Watchdog triggers a secure interrupt if the non-secure SW monopolizes the core for a predetermined amount of time, forcing a switch to the secure world. This time interval, being configurable, allows the scheduler of the secure world OS to adjust the amount of computational time it will give to the normal world environment.

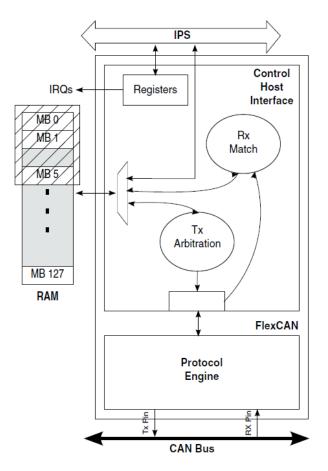

#### 3.3.3 FlexCAN

The Flexible Controller Area Network (FlexCAN) module is a communication controller that implements the interface to the CAN protocol according to the CAN 2.0B protocol specification, which supports both standard and extended message frames. FlexCAN supports up to 64 Message Buffers (MBs) and each of them can be configured to receive (Rx) or to transmit (Tx).

For more information, please refer to section A.4.

#### 3.3.4 IOMUX Controller

The IOMUX (I/O Muxing) Controller (IOMUXC) enables the SoC to share one pin's pad to several functional blocks by multiplexing the pad's I/O signals.

For more information about IOMUXC, please refer to section A.5.

#### 3.3.5 Universal Asynchronous Receiver/Transmitter

The UART module is responsible to translate data between parallel and serial forms. It takes bytes of data and transmits them bit by bit sequentially. On the other side of the connection, a second UART re-assembles the bits into complete bytes. The *universal* term indicates that the developer can configure the bitrate and the data format which varies with the modes of operation of this module. For more information about UART, please refer to section A.6.

#### 3.3.6 Join Test Action Group and Open On-Chip Debugger

This section is dedicated to the HW and SW used for debugging purposes. Starting with JTAG (Join Test Action Group), which is implemented in a great part of the most modern processors, it is a standard for testing printed circuit boards and integrated circuits using boundary-scan, and electrical signals to communicate with the target. JTAG allows debuggers to communicate with a processor, letting developers to perform operations like single stepping and adding breakpoints. The debugger used in xLuna development was the well known Unix-like systems and C debugger, the GNU Debugger (GDB).

In order to be possible to use JTAG, it is needed an interface between the machine/PC which is debugging and the target. During xLuna development, it was used a Luminary Micro BD-ICDI-B, which is an In-Circuit Debug Interface (ICDI) board. This board has a Mini-USB port to connect to the PC and JTAG pins to connect to the target.

As GDB can not control the signalling of JTAG to the ICDI board, it was needed an extra SW to make the bridge between GDB and the drivers of the ICDI board. This bridge is done by Open On-Chip Debugger (OpenOCD). The OpenOCD interprets the GDB protocol and transforms it to JTAG signals. In order to run OpenOCD, two configurations files are needed – one for using with the ICDI board and another for the target processor – which are responsible to configure OpenOCD to the specific HW used. These configurations files are written in TCL/TK programming language.

For more information regarding JTAG and OpenOCD, please refer to [38] and [39], respectively.

## Chapter 4

## **Development and Implementation**

An expert is a man who has made all the mistakes which can be made in a very narrow field. (Niels Bohr, Danish physicist)

In this chapter it will be explained all the work developed, as well as all the main decisions that were made, their consequences on the development part of the project and the difficulties that crossed in the way.

### 4.1 Preparation

The purpose of this section is to describe all the steps took to set-up all the tools and functionalities needed to provide a stable and consistent working base to the main work.

#### 4.1.1 OpenOCD set-up for debugging via JTAG

The debug infrastructure for a project of this nature is crucial. The need of having the capability of debugging and accessing the registers in a very complex SW like this is huge, so that it is why this is the first step took in xLuna development.

Initially OpenOCD was installed and configured. To install it, it was needed to build it with a specific configuration to support the ICDI board (section 3.3.6). After that, OpenOCD needs two configuration files written in TCL/TK programming language – one for the interface/JTAG board and other for the target chip/board to debug. In the case of the ICDI board, it was needed to provide the ID of the board and initialize the values of FTDI registers. Regarding the configuration file for the target chip, the Debug Access Port (DAP) and the memory base addresses of the JTAG controller and of the target core to debug are used as parameters by OpenOCD functions that configure the SoC for JTAG debugging. These two configuration files are called every time the OpenOCD starts. The instructions followed can be found in [40], where it is explained how to install OpenOCD and configure it for ARM Cortex-M3.

When the project was near reaching the milestone, referred in section 2.1, a new need emerged to debug all cores simultaneously. To accomplish that, OpenOCD needed to be capable of doing that, and theoretically it was. It was spent exactly two weeks on trying to configure OpenOCD to debug all cores without the desired results. What was accomplished was the ability to read the value of two predetermined cores' registers but only one of them could be debugged with all the features provided by GDB. It was also discovered that the OpenOCD development team were still working on the multi-core debugging capabilities of OpenOCD for ARM based processors. Concluding, it was not possible to debug all cores with the full features of GDB at that time. This fact limited a lot the work being preformed.

#### 4.1.2 UART set-up for providing a console

The debugging is not enough if the development team does not have an human-machine interface, like a console or a terminal. To provide one, there was only one possibility in this case, which was using an UART line.

Before starting the development work, it was needed to know how UART works and all information about its registers for this specific SoC. This kind of information is located in chapter 64 of i.MX6Q Reference Manual [41]. There, it could be found that UART has a Tx (Transmission) FIFO which holds the characters to print. These characters need to be write in a specific bit-field of UART Transmitter Register but only if Tx FIFO has free space. The others registers allow to configure UART as needed and check its working status.

Then, the development work started with a small function in ARM assembly that worked directly on the UART registers. It was resorted to Reference Manual to configure them but the function was not printing anything at first. After trying several different configurations, it was considered to use the configurations present in U-Boot<sup>1</sup> code but it was still not working. Then, it was realized that the problem was not in UART configurations. It was needed to configure the IOMUXC (Input/Output Multiplexing Controller) for a specific port to work in GPIO mode so that the CPU and the UART could be connected correctly. It was resorted to U-Boot source code again to discover how to configure the IOMUXC.

Later, with the integration of FreeRTOS, it was developed the device drivers for UART in C for future use in the project, but in this case it was followed the instructions and the information present in i.MX6Q Reference Manual.

## 4.2 The Real-time Operating System – FreeRTOS<sup>TM</sup>

This section is reserved to the work done directly related with FreeRTOS. Most of the work done by all the development team of xLuna was on FreeRTOS domain. Thus, in this section most of the work is described.

#### 4.2.1 Vector table and exceptions handlers set-up

The first task related with FreeRTOS that was needed to be done was to map the exception vector table. The exception vectors map all the ARM exceptions. In this case, they are the following:

- Reset;

- Undefined instruction;

- Supervisor call (SVC);

- Prefetch abort;

- Data abort;

- *IRQ interrupt*;

<sup>&</sup>lt;sup>1</sup>The U-Boot (Universal Boot loader) utility is a multi-platform, open-source, universal boot loader with comprehensive support for loading and managing boot images, such as the Linux kernel. For more information, please refer to [42].

#### • FIQ interrupt.

To accomplish this, it was necessary to implement a set of instructions, the vector table. Each instruction call the handler of the respective exception. This piece of code works like an if..else statement in C. When an exception occurs, the Program Counter (PC) go to 0x0 memory address by default and then the correct handler is called. Thus, in the initialization of xLuna, the vector table is copied to the initial memory address of the SABRE SD memory space. All the handlers used are provided by the FreeRTOS except the *reset* handler, which is the initialization code of all the system.

With the exception vector table mapped, the xLuna gained the capability of handling all kind of exceptions, including IRQs, which are essential to the correct functioning of FreeRTOS. But for the CPU to be able to receive IRQs it was needed to configure the GIC (section 3.3.2). Initially, it was used the assembly code from FreeRTOS to make GIC work but later in the project it was developed xLuna's own GIC device drivers in C. This work was based on chapter 3 of Cortex-A9 MPCore® Technical Reference Manual [43].

#### 4.2.2 EPIT set-up for providing timer and tick capabilities to the OS

After xLuna had the ability to handle interrupts, it was necessary to implemented the tick<sup>2</sup> handler for FreeRTOS clock. To do that, it was needed to choose one timer from the two available in the SABRE SD – the General Purpose Timer (GPT) and the Enhanced Periodic Interrupt Timer (EPIT). The development team decided to go for EPIT because it is a timer that is capable of providing precise interrupts at regular intervals with minimal processor intervention, which is just perfect for a tick timer. So what it was needed to do was to develop the EPIT drivers and invoke the tick handler of FreeRTOS in the tick ISR, in order to provide the tick timer to the RTOS.

The drivers were developed following the code present in i.MX6Q SDK [45] and the guidelines present in chapter 24 of the i.MX6Q Reference Manual [41]. Then, it was developed a simple ISR that only printed a small debug message.

Initially the EPIT was working well but the IRQs were not getting caught or fired. After

<sup>&</sup>lt;sup>2</sup>In computer science, a clock tick is the smallest unit of time recognized by a device. For personal computers, clock ticks generally refer to the main system clock, which runs at 66 MHz. This means that there are 66 million clock ticks (or cycles) per second [44].

analysing the value of the EPIT's registers, it could be concluded that the IRQs were not getting fired. So it was checked the configurations of EPIT and tried others configurations but the problem was on the wrong mapping of EPIT's registers structures in the code, i.e., the wanted values for the configurations were being written on different memory addresses than those that were supposed. After this task was accomplished with success, xLuna was ready to provide the tick timer to the RTOS and I changed the ISR to the FreeRTOS's tick handler. Then it was needed to test the work done by using the scheduler of FreeRTOS.

Initially it was created the main() function of FreeRTOS. In this initial phase, the main() just needed to have initialized the basic HW, create the OS's tasks desired and start the FreeRTOS's scheduler. Resorting to FreeRTOS's documentation [46], it was created two different tasks with different priority that would print different debug messages such that it is possible to distinguish them. To accomplish this task, it was needed to be sure that IRQs were enabled in secure world and disabled in normal world, which could be done using GIC (chapter 3 of the Cortex-A9 MPCore Technical Reference Manual [43]). After correcting some code mistakes, it was accomplished to have two RTOS's tasks running concurrently. This was a very important step for xLuna.

#### 4.2.3 I2C (Inter-Integrated Circuit) and accelerometer set-up

This section is reserved for the development of I2C device drivers as well as the accelerometer drivers, which is an I2C peripheral. The main goal of using the accelerometer is to simulate a car accident by catching high acceleration values of the board in any direction. The accelerometer incorporated in SABRE SD board is a Freescale MMA8451Q, which is a smart low-power, three-axis capacitive micro-machined accelerometer with 14 bits of resolution.

From the i.MX6 Reference Manual (chapter 35) [41], it was known the need to configure the pads of the CPU I/O pins and the clocks for I2C device first. After consulting the SABRE SD's schematics [45], it was known what pins it was needed to use. Starting on IOMUXC, it was configured two pins in order to establish the connection between the CPU and the I2C device – one for bus clock and the other for bus data. Then, it was enabled the I2C clock that is controlled by Clock Controller Module (CCM) (chapter 18 of i.MX6 Reference Manual [41]).

In I2C device drivers it was implemented three public functions. One of them to initialize the device, which also configures IOMUXC and CCM like described above, another to read from a

peripheral and the last one to write to a peripheral. The accelerometer drivers consisted in the initialization of the device and the data collection to get the acceleration values. As expected, all operations done directly with the device were made by using I2C functions to read and write. Both of these drivers' code were based on i.MX6 SDK.

This task lasted exactly two weeks. The troubles found were mainly related with making I2C bus working properly, because it was occurring an I2C arbitration lost error. It was taken a couple of days to understand the reason of I2C arbitration lost error. This error was occurring because, to make I2C bus work, all the peripherals present in the I2C bus must be powered on, which was not happening due the fact that IOMUXC was not configured properly. Some code mistakes, derived from the high complexity of the code used to access the registers of the devices, were also responsible for the long duration of this task.

After accomplish to get the acceleration values, it was created a FreeRTOS's task that was always getting the acceleration values and when high values were detected a LED blinked.

#### 4.2.4 USB drivers and stack

As referred in section 2.1, for the milestone of xLuna, it has to be implemented an eCall application simulation, by sending a SMS to a pre-determined mobile phone number. So, a mobile communication modem was required. There were three options: (i) a 3G Mini-PCIe modem; (ii) a 3G plus WIFI Mini-PCIe modem; or (iii) a 3G USB modem. In this case, it was chosen the option (iii), a 3G USB modem. When compared to the others options, the option (iii) was the cheaper and the quicker to get because 3G USB modems are very common today. In terms of complexity of the work required, the option (iii) seemed the simplest one of the three options available. In fact, since the i.MX6Q SABRE SD supports to be the USB host, it was just necessary to develop the USB Stack, which is composed by, the USB Communication Device Class<sup>3</sup> module, the USB Host module and the device drivers for the USB 2.0 controller.

The i.MX6Q has four USB 2.0 controller cores, but only two are used in SABRE SD board – USB 2.0 Controller Core 0 and USB 2.0 Controller Core 1. The Controller Core 1, or Host1 Core, is only used by the CPU to communicate with the Mini-PCIe adapter. The Controller

<sup>&</sup>lt;sup>3</sup>USB Communications Device class (CDC) is a composite Universal Serial Bus device class which is used primarily for modems, but also for ISDN and fax machines and telephony applications for performing regular voice calls [47].

Core 0, or OTG Core, has the only USB port available for external USB devices or hosts. Thus, the OTG Core supports working in Host mode or Device mode.

This task lasted about one week. The work related with it was mainly research on USB stack and reading the chapter 65 of the i.MX6Q Reference Manual [41] in order to understand the working manner of the USB 2.0 Controller of the SoC.

Furthermore, it was necessary to protect the USB Controller. So, the normal SW's attempts to access this device were blocked in CSU device and the Linux kernel was modified in order not to initialize and use the USB Controller.

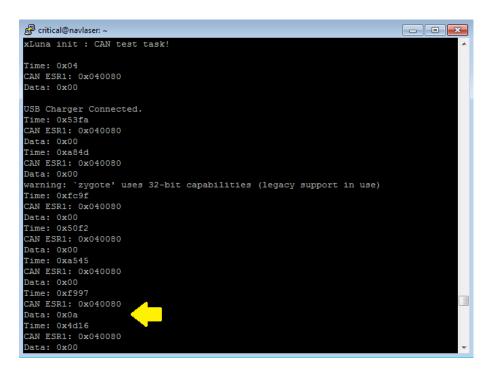

#### 4.2.5 3G USB modem set-up for sending a SMS