João Maria Duarte Andrade

## Design Space Exploration of LDPC Decoders on Programmable and Reconfigurable Architectures

Tese de Doutoramento em Engenharia Electrotécnica e de Computadores, ramo de especialização em Telecomunicações, orientada pelo Professor Doutor Vitor Manuel Mendes Silva e Professor Doutor Gabriel Falcão Paiva Fernandes, e apresentada ao Departamento de Engenharia Electrotécnica e de Computadores da Faculdade de Ciências e Tecnologia da Universidade de Coimbra

Setembro de 2015

Universidade de Coimbra

Background of cover image source: Earth Observatory, NASA.

### UNIVERSIDADE DE COIMBRA FACULDADE DE CIÊNCIAS E TECNOLOGIA departamento de engenharia electrotécnica e de computadores

### **Design Space Exploration of LDPC Decoders on Programmable and Reconfigurable Architectures**

João Maria Duarte Andrade

(Mestre)

### Dissertação para a obtenção do Grau de Doutor em Engenharia Electrotécnica e de Computadores

Tese de Doutoramento em Engenharia Electrotécnica e de Computadores, ramo de especialização em Telecomunicações, orientada pelo Doutor Vitor Manuel Mendes da Silva e pelo Doutor Gabriel Falcão Paiva Fernandes, e apresentada ao Departamento de Engenharia Electrotécnica e de Computadores da Faculdade de Ciências e Tecnologia da Universidade de Coimbra.

> Coimbra Setembro 2015

João Maria Duarte Andrade: *Design Space Exploration of LDPC Decoders on Programmable and Reconfigurable Architectures,* Tese de Doutoramento em Engenharia Electrotécnica e de Computadores, ramo de especialização em Telecomunicações, Faculdade de Ciências e Tecnologia, Universidade de Coimbra © Setembro 2015

This Thesis was supported by Instituto de Telecomunicações under the grants PEst-OE/ EEI/LA0008/2011, PEst-OE/EEI/LA0008/2013 and UID/EEA/50008/2013, and by Fundação para a Ciência e Tecnologia doctoral scholarship grant SFRH/BD/78238/2011 under the QREN - POPH - Type 4.1 - Advanced Formation programmes financed by the Fundo Social Europeu (FSE) and the national funding of MEC.

## Acknowledgments

Aos meus orientadores, Professor Vitor Silva e Professor Gabriel Falcão, tenho a agradecer toda a ajuda, apoio e discussões que melhoraram o meu trabalho. Tenho de lhes reconhecer a disponibilidade em rever e melhorar as minhas contribuições científicas. Graças ao Vitor pude contornar sempre mais uma parede quando nelas embatia e manter em vista o caminho a percorrer. Devo ao encorajamento do Gabriel várias viagens Mundo fora, e as estadias no EPFL e na Xilinx Research Labs.

Agradeço ao Professor Marco Gomes, bem como ao João Amaro, ao Sinédoque, e colegas de laboratório, a ajuda prestada, procrastinação activa e sanidade proporcionadas. Aos investigadores do INESC-ID, Frederico Pratas, Professor Pedro Tomás e Professor Leonel Sousa, agradeço a hospitalidade demonstrada e colaborações realizadas. Ao Filipe Silva devo a disponibilidade do seu sofá no 16ème, ao João Nunes uma desculpa para voltar a Verbier e ao Carlos Oliveira o regresso à minha *alma mater* desportiva.

I thank David Novo, Nithin George, Kimon Karras and Professor Joseph R. Cavallaro, for their kindness, support, influence and academic collaboration. To Chantal Schneeberger I owe "mille mercis" for her effortless way to integrate people at LAP, making my life much easier. I would like to acknowledge Professor Paolo Ienne and Michaela Blott for hosting me at LAP, EPFL and at Xilinx Research Labs. Professor Shinichi Yamagiwa has granted access to the GPU-cluster without which simulations would still be running now.

Sem o apoio incondicional da minha família não seria possível ter chegado aqui. Aos meus Pais, Dá e Jasa, agradeço o permanente incentivo para aprender mais e maximizar o meu capital humano, bem como todo o apoio e incessante comunicação no meu ano fora. À Nanã e ao JotaPê, tenho a agradecer os magníficos momentos que me proporcionaram com o João Pequenino e a Maria Rita. Agradeço também à família Beldroega toda a ajuda prestada e cuidados dispensados, em especial à Margarida na minha ausência.

Last, but not the least, estou eternamente endividado para com a Margarida, o meu maior pilar de sanidade e amor. Dedicar-lhe estas poucas linhas é o mínimo, embora parca recompensa, para alguém sem cuja presença teria sido impossível concluir o que se iniciou há já longo tempo.

A todos, muito obrigado,

Aos meus Avós, Luísa e João, Inha e João Maria, E, à Margarida,

Everyday life is like programming, I guess. If you love something you can put beauty into it.

- Donald Knuth

## Abstract

Low-density parity-check (LDPC) codes are capacity-approaching linear block codes widely employed for digital communication systems and storage. However, the realization of LDPC decoders is a very challenging process due to the numerical complexity associated with binary, and especially, with non-binary LDPC codes. Whereas very large scale integration (VLSI) technology provides the necessary means to allow the realization of efficient LDPC decoders that meet both low latencies and high decoding throughputs, the development process behind application-specific integrated circuit (ASIC) and field-programmable gate array (FPGA) decoders is error-prone, protracted and is an endeavor captured by low-level micro-architecture and silicon details that pose high non-recurring engineering (NRE) costs.

In this Thesis, we explore efficient ways to overcome the challenges associated with the development of binary and non-binary LDPC decoders on both programmable and reconfigurable hardware. We propose methodologies that leverage on the immense computational power of multicore *graphics processing unit* (GPU) architectures applied to binary and non-binary LDPC decoders, not only for achieving the very high data rates required for nowadays communications, but also for very fast Monte Carlo *bit error rate* (BER) simulation, essential for the study of new LDPC codes.

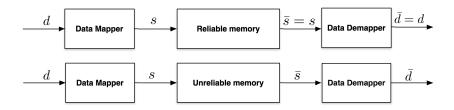

Having exploited the potential of parallel computing on programmable hardware and identified its shortcomings, we extend our proposed methodology to reconfigurable hardware. The developed FPGA-decoders explore different *high-level synthesis* (HLS) programming models, based on dataflow, loop-annotated and wide-pipeline architectures. From the performance analysis of these accelerators, we identify the key guidelines to the design of efficient LDPC decoders under each approach. Finally, we propose algorithmand silicon-level procedures to boost the LDPC decoders energy efficiency. Namely, we propose *gear-shift* techniques, and incorporation of unreliable memory storage along with BER degradation mitigation strategies.

### Keywords

LDPC codes, Galois field, Reconfigurable computing, Parallel computing, High-level synthesis, Unreliable memory storage

## Resumo

Os códigos definidos por matrizes de teste de paridade esparsas (LDPC) são bastante poderosos em sistemas de comunicação digital e armazenamento de dados, por operarem quase à capacidade do canal. No entanto, a realização de descodificadores LDPC é um processo desafiante devido à complexidade associada aos códigos LDPC binários e, em particular, aos não-binários. Apesar de a *tecnologia de integração em larga escala* (VLSI) ter capacidade para a realização de descodificadores LDPC que cumpram a baixa latência e o elevado ritmo de transmissão de dados, os processos de desenvolvimento em *circuitos integrados de aplicação específica* (ASIC) ou em *circuitos lógicos programáveis* (FPGA) são morosos, conduzem facilmente a erros e são pautados por detalhes minuciosos ao nível do silício e da micro-arquitectura que elevam os custos não *recorrentes de engenharia* (NRE).

Esta tese aborda estratégias para superar os desafios inerentes ao desenvolvimento de descodificadores binários e não-binários em arquitecturas programáveis e reconfiguráveis. Deste modo, são propostas metodologias que exploram a imensa capacidade computacional de arquitecturas *multicore*, como *processadores gráficos* (GPUs), aplicadas a descodificadores binários e não-binários, não só atingindo os elevados ritmos de dados necessários aos sistemas de comunicação actuais, mas também permitindo rápida simulação de Monte Carlo para a caracterização da *taxa de erros* (BER), essencial para o estudo de novos códigos e algoritmos.

A metodologia proposta para arquitecturas programáveis é extendida a arquitecturas reconfiguráveis. Os descodificadores FPGA desenvolvidos tiram partido de síntese de alto-nível (HLS), baseada em modelos *dataflow*, *loop-annotated* e *wide-pipeline*. Através da análise da performance obtida em cada abordagem, propõem-se linhas orientadoras para o desenvolvimento de descodificadores de elevados desempenhos. Finalmente, são propostos métodos ao nível algorítmico e do silício de melhoria da eficiência energética dos descodificadores propostos. As técnicas desenvolvidos utilizam técnicas de *gear-shift* e de armazenamento de dados em memórias não-fiáveis, para as quais são introduzidas estratégias de diminuição da degradação de BER.

### **Palavras Chave**

Códigos LDPC, Campos de Galois, Computação reconfigurável, Computação paralela, Síntese de alto-nível, Armazenamento em memória não-fiável

## Contents

#### Page

| 1 | Intr | oductior       |                                                                                                                                         |

|---|------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------|

|   | 1.1  | Motiva         | ition                                                                                                                                   |

|   | 1.2  | Objecti        | ves                                                                                                                                     |

|   | 1.3  | Main C         | Contributions                                                                                                                           |

|   | 1.4  | Outline        | e                                                                                                                                       |

| 2 | LDF  | PC Code        | es Fundamentals 11                                                                                                                      |

|   | 2.1  | Linear         | Block Codes                                                                                                                             |

|   |      | 2.1.1          | Generator Matrix                                                                                                                        |

|   |      |                | Parity-Check Matrix 13                                                                                                                  |

|   |      |                | Coding Rate                                                                                                                             |

|   |      |                | Syndrome and Error Detection                                                                                                            |

|   | 2.2  |                | Codes over GF(2)         16                                                                                                             |

|   |      |                | Tanner Graph         17                                                                                                                 |

|   | 2.3  |                | Decoding Algorithms over GF(2)                                                                                                          |

|   |      |                | Sum-Product Algorithm                                                                                                                   |

|   |      |                | Logarithmic Sum-Product Algorithm                                                                                                       |

|   |      |                | Min-Sum Decoding Algorithm                                                                                                              |

|   | 2.4  |                | Codes over GF(q)                                                                                                                        |

|   |      | 2.4.1          | Factor Graph 23                                                                                                                         |

|   | 2.5  | LDPC I         | Decoding Algorithms over GF(q)                                                                                                          |

|   |      |                | Sum-Product Algorithms                                                                                                                  |

|   |      |                | Extended Min-Sum Algorithm                                                                                                              |

|   | 2.6  | Decodi         | ing Schedules                                                                                                                           |

|   |      | 2.6.1          | Two-phased Message-passing                                                                                                              |

|   |      | 2.6.2          | Turbo-decoding Message-passing 37                                                                                                       |

|   | 2.7  |                | ew of the Complexity                                                                                                                    |

|   |      | 2.7.1          | Binary Decoding Algorithms                                                                                                              |

|   |      | 2.7.2          | Non-binary Decoding Algorithms 39                                                                                                       |

|   | 2.8  | Summa          | $\operatorname{ary} \ldots 40$ |

| 3 | LDF  | PC Deco        | der Architectures Overview 41                                                                                                           |

|   | 3.1  | Decodi         | ing on Programmable Architectures                                                                                                       |

|   |      |                | Programmable LDPC Decoder Mapping 44                                                                                                    |

|   |      |                |                                                                                                                                         |

|   |      | 3.1.2          | Tanner Graph Indexing Schemes   45                                                                                                      |

|   |      | 3.1.2          | Tanner Graph Indexing Schemes45                                                                                                         |

|   |      | 3.1.2<br>3.1.3 | Tanner Graph Indexing Schemes45                                                                                                         |

|   |      | 3.1.6 Decoding Algorithms                                        | 59  |

|---|------|------------------------------------------------------------------|-----|

|   |      | 3.1.7 Decoding Schedules                                         | 60  |

|   | 3.2  | Decoding on Reconfigurable Architectures                         | 61  |

|   |      | 3.2.1 Programming Models                                         | 62  |

|   |      | 3.2.2 Parallelism                                                | 62  |

|   | 3.3  | Summary                                                          | 63  |

| 4 | Prog | grammable LDPC Decoders                                          | 65  |

|   | 4.1  |                                                                  | 66  |

|   |      | 4.1.1 Parallel Computing Principles                              | 67  |

|   |      | 4.1.2 General-purpose x86 multicore CPU                          | 70  |

|   |      | 4.1.3 General-purpose Computing on CUDA and OpenCL GPUs          | 72  |

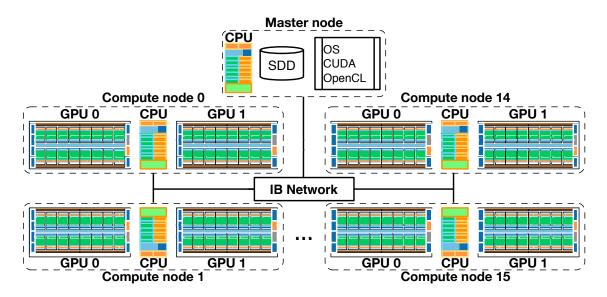

|   |      | 4.1.4 Distributed Computing on multicore Fermi Dual-GPU Clusters | 76  |

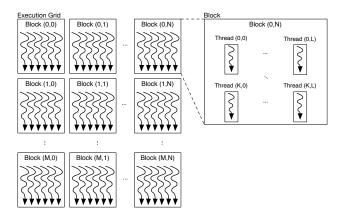

|   |      | 4.1.5 CUDA Programming Model                                     | 78  |

|   |      | 4.1.6 OpenCL Programming Model                                   | 79  |

|   |      | 4.1.7 MPI Programming Model                                      | 81  |

|   | 4.2  | Programmed LDPC Decoder Accelerators                             | 82  |

|   | 4.3  | Single-GPU Decoders                                              | 83  |

|   |      | 4.3.1 Data-parallelism                                           | 84  |

|   |      | 4.3.2 Thread-parallelism                                         | 87  |

|   |      | 4.3.3 Optimized Tanner Graph Indexing                            | 88  |

|   |      | 4.3.4 Binary LDPC Decoding                                       | 93  |

|   |      | 4.3.5 Non-binary LDPC Decoding                                   | 103 |

|   | 4.4  | GPU-cluster Decoders                                             | 112 |

|   |      | 4.4.1 Fast BER Monte Carlo Simulation                            | 112 |

|   |      | 4.4.2 GPU Cluster Execution                                      | 116 |

|   | 4.5  | Hybrid CPU/GPU Decoders                                          | 122 |

|   |      | 4.5.1 Potential of the CPU Co-accelerator                        | 123 |

|   |      | 4.5.2 Experimental Results                                       | 123 |

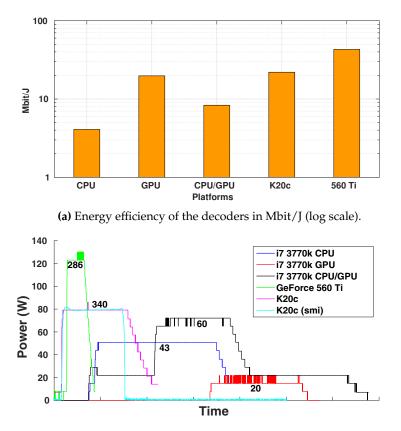

|   |      | 4.5.3 Energy efficiency of the CPU/GPU decoder                   | 126 |

|   | 4.6  | Summary                                                          | 128 |

| 5 |      | onfigurable LDPC Decoders                                        | 129 |

|   | 5.1  | Reconfigurable Computing                                         | 130 |

|   |      | 5.1.1 Reconfigurable Architectures                               | 130 |

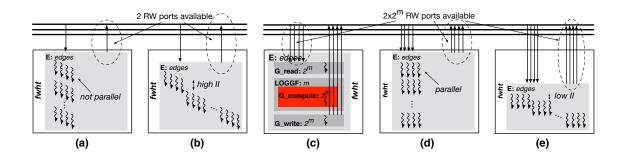

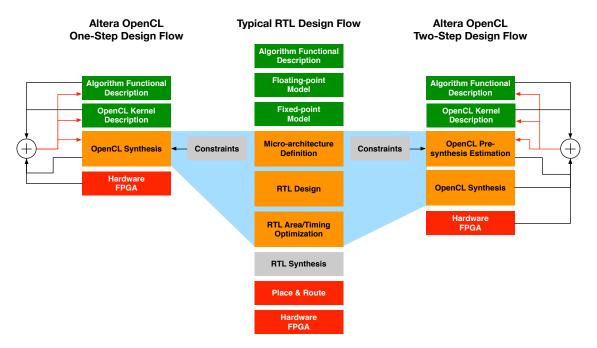

|   |      | 5.1.2 High-level Synthesis Programming Models                    | 134 |

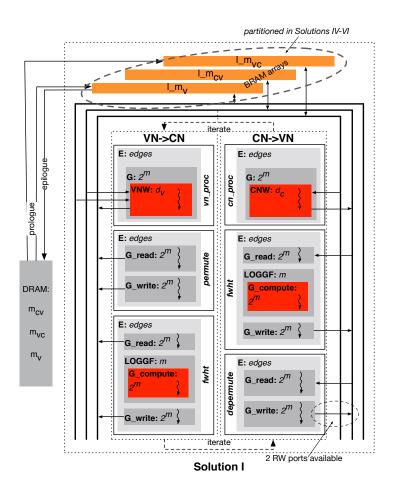

|   | 5.2  | Synthesized LDPC Decoder Accelerators                            | 140 |

|   | 5.3  | Dataflow LDPC Decoder                                            | 141 |

|   |      | 5.3.1 M-modulo dataflow LDPC decoder                             | 143 |

|   |      | 5.3.2 Pipelined FU Execution                                     | 146 |

|   |      | 5.3.3 Experimental results                                       | 149 |

|   | 5.4  | Loop-annotated LDPC Decoder                                      | 155 |

|   |      | 5.4.1 LDPC decoder isomorphic mapping to hardware                | 158 |

|   |      | 5.4.2 Loop-acceleration                                          | 160 |

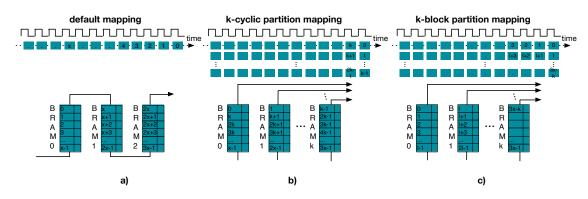

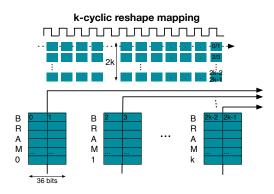

|   |      | 5.4.3 Memory mapping                                             | 161 |

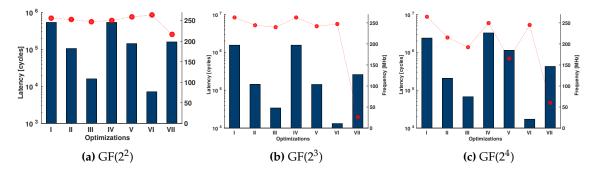

|   |      | 5.4.4 Experimental results                                       | 164 |

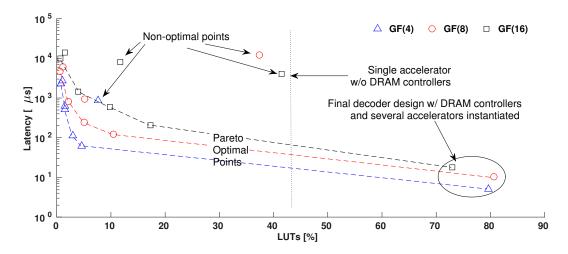

|   | 5.5  | Wide-pipeline LDPC Decoder                                       | 176 |

|   |      | 5.5.1 Altera OpenCL LDPC Decoder                                 | 177 |

|   |      | 5.5.2 Experimental results                                       | 189 |

|   |      |                                                                  |     |

|   |      | 5.5.3    | SOpenCL LDPC Decoder                                  | 199 |

|---|------|----------|-------------------------------------------------------|-----|

|   |      | 5.5.4    | Experimental results                                  | 203 |

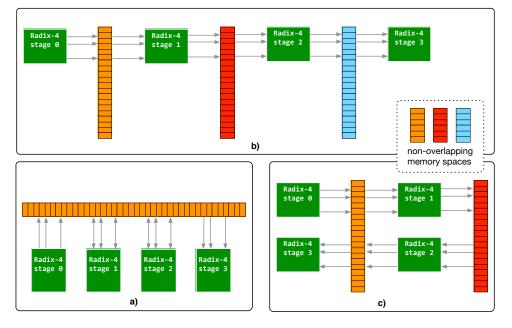

|   |      | 5.5.5    | Operational Transform FFT/FWHT                        | 212 |

|   |      | 5.5.6    | Experimental results                                  | 217 |

|   | 5.6  | Summ     | nary                                                  | 221 |

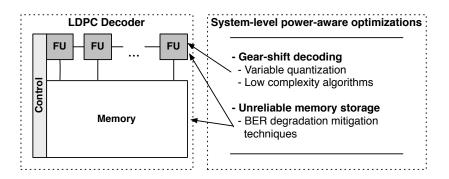

| 6 | Рои  | ver-awa  | re LDPC Decoders                                      | 223 |

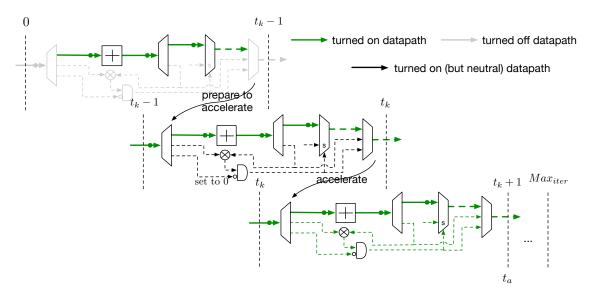

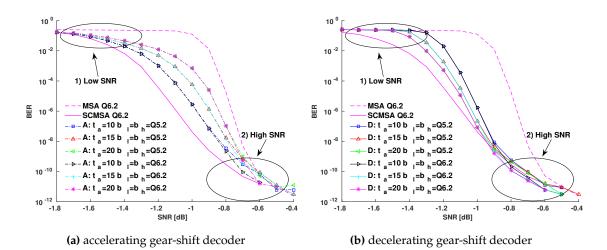

|   | 6.1  | Gear-S   | Shift LDPC Decoders                                   | 225 |

|   |      | 6.1.1    | Gear-shift strategies                                 | 226 |

|   |      | 6.1.2    | MSA-based gear-shift decoder                          | 228 |

|   |      | 6.1.3    | Variable quantization bits and compact representation | 230 |

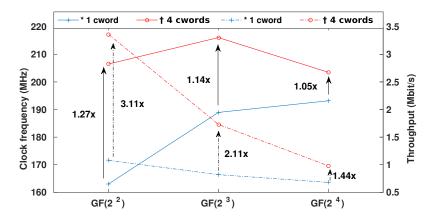

|   |      | 6.1.4    | Experimental Results                                  | 232 |

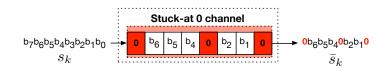

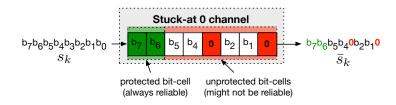

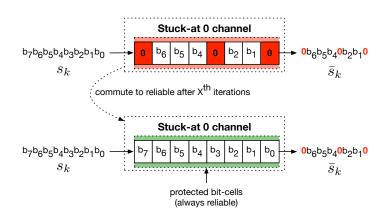

|   | 6.2  | LDPC     | Decoder under Unreliable Memory Storage               | 237 |

|   |      | 6.2.1    | Unreliable arithmetic and control silicon             | 238 |

|   |      | 6.2.2    | Unreliable Memory Storage                             | 239 |

|   |      | 6.2.3    | Error Mitigation Strategies                           | 242 |

|   |      | 6.2.4    | BER degradation mitigation strategies                 | 243 |

|   |      | 6.2.5    | Experimental Results                                  | 248 |

|   |      | 6.2.6    | Power savings for the eDRAM case                      | 251 |

|   | 6.3  | Summ     | nary                                                  | 256 |

| 7 | Con  | clusior  | ns and Future Work                                    | 259 |

| - | 7.1  |          | e Work                                                | 263 |

|   | _    |          |                                                       |     |

| Α | Sur  | vey of t | he LDPC Decoders on Programmable Hardware             | 267 |

| B | Gal  | ois Fiel | d Arithmetic                                          | 278 |

|   | B.1  | Fields   |                                                       | 280 |

|   |      | B.1.1    | Primitive Polynomials                                 | 282 |

|   |      | B.1.2    | Matrix-Representation of Fields                       | 284 |

|   |      | B.1.3    | Fourier Transform                                     | 284 |

| С | List | of Har   | dware Employed                                        | 287 |

# **List of Figures**

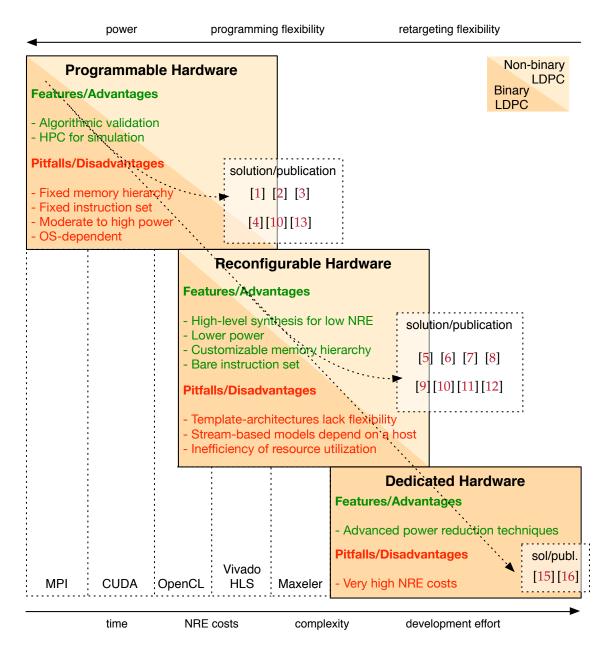

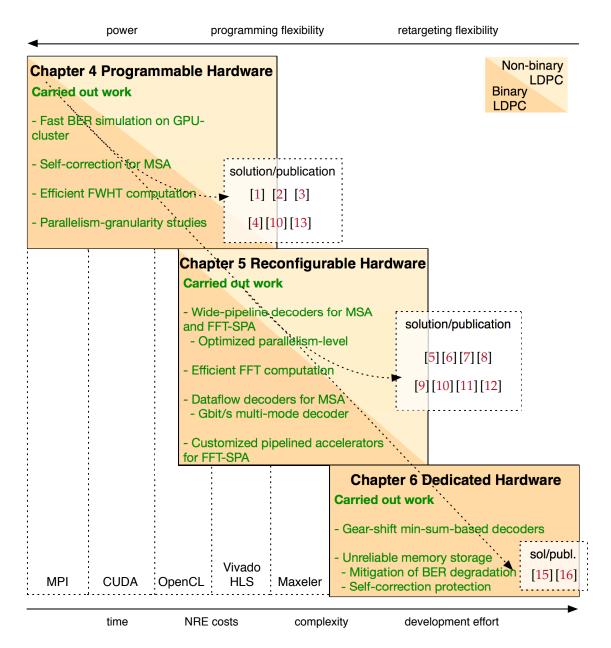

| 1.1<br>1.2 | Design space exploration methodology                                   | 5<br>9 |

|------------|------------------------------------------------------------------------|--------|

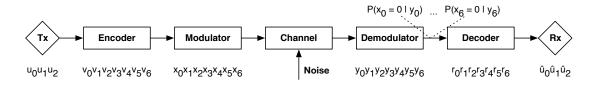

| 2.1        | Digital transmission system with forward error correction.             | 12     |

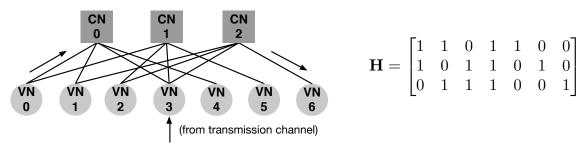

| 2.2        | LDPC code over GF(2) in matrix and Tanner graph representation.        | 17     |

| 2.3        | Factor graph extension to the Tanner graph.                            | 24     |

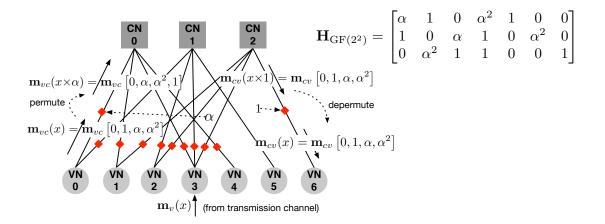

| 2.4        | Mixed-domain message-passing.                                          | 33     |

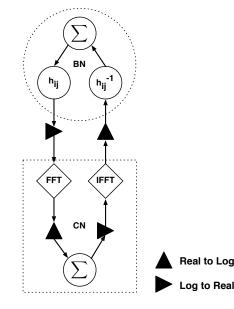

| 2.5        | TPMP decoding schedule                                                 | 37     |

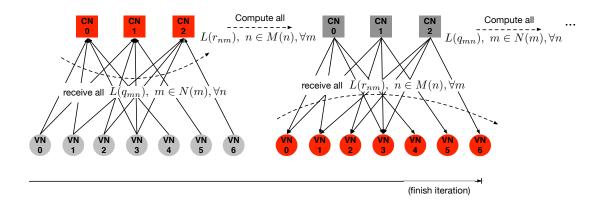

| 2.6        | TDMP decoding schedule                                                 | 38     |

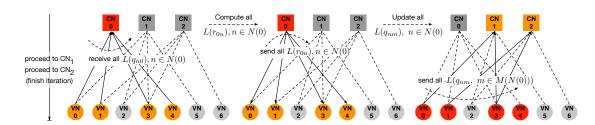

| 3.1        | Tanner graph isomorphic mapping on programmable architectures          | 44     |

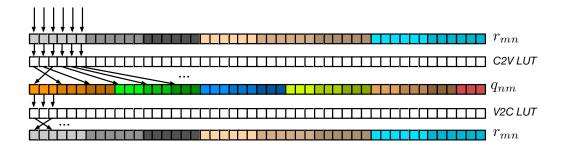

| 3.2        | Tanner graph indexing based on sparse matrix storage                   | 46     |

| 3.3        | LDPC-IRA Tanner graph indexing based on sparse matrix storage          | 47     |

| 3.4        | QC-LDPC Tanner graph indexing based on sparse matrix storage           | 48     |

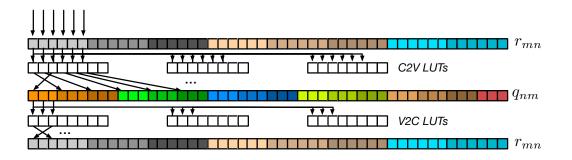

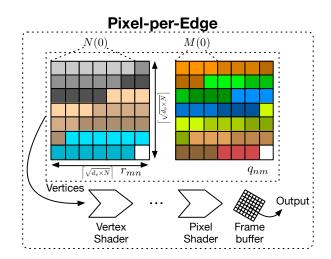

| 3.5        | Pixel-per-Edge LDPC decoder thread-parallelism.                        | 51     |

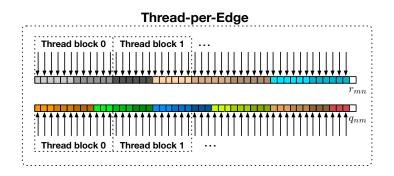

| 3.6        | Thread-per-Edge LDPC decoder thread-parallelism approach               | 52     |

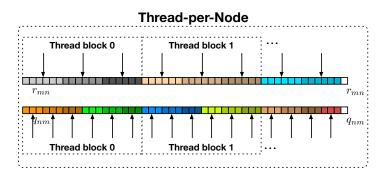

| 3.7        | Thread-per-Node LDPC decoder thread-parallelism approach               | 52     |

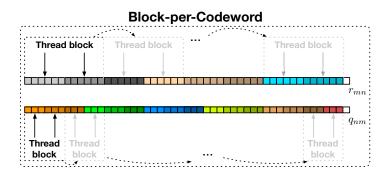

| 3.8        | Block-per-Codeword LDPC decoder thread-parallelism.                    | 54     |

| 3.9        | Thread-per-Codeword LDPC decoder thread-parallelism approach           | 56     |

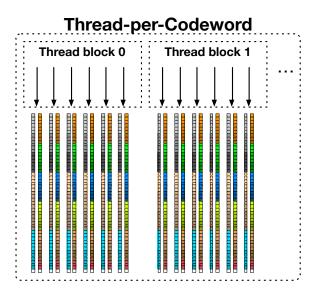

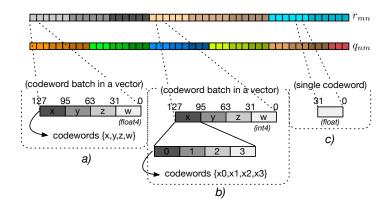

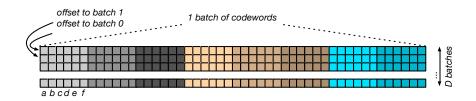

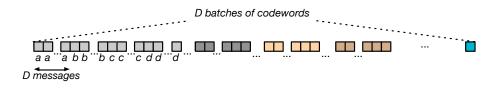

| 3.10       | Single codeword and codeword batch on a vector                         | 58     |

| 3.11       | Padded data-parallelism approach                                       | 58     |

|            | Interleaved data-parallelism approach                                  | 59     |

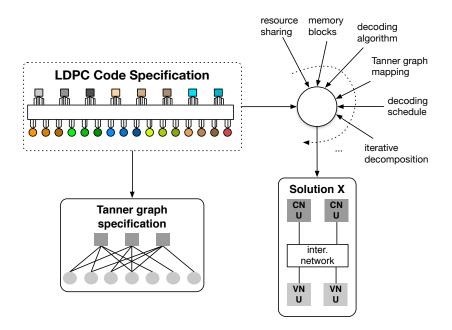

| 3.13       | Tanner graph isomorphic mapping                                        | 62     |

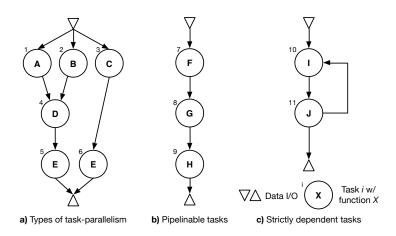

| 4.1        | Data-dependency graphs                                                 | 68     |

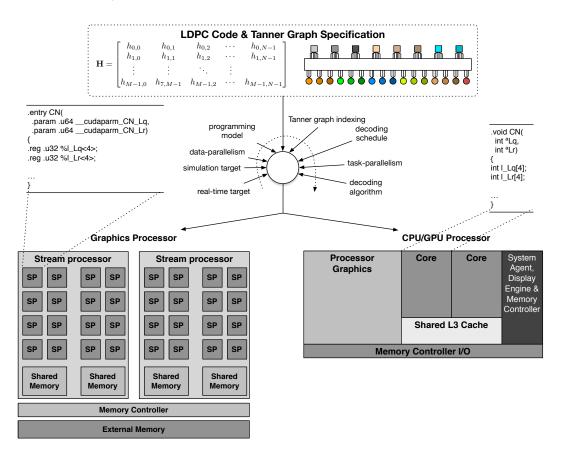

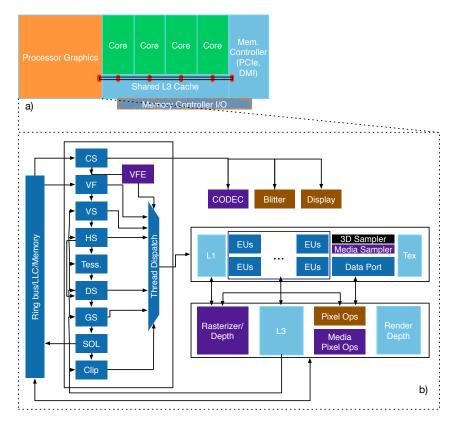

| 4.2        | Ivy bridge CPU/GPU hybrid architecture                                 | 71     |

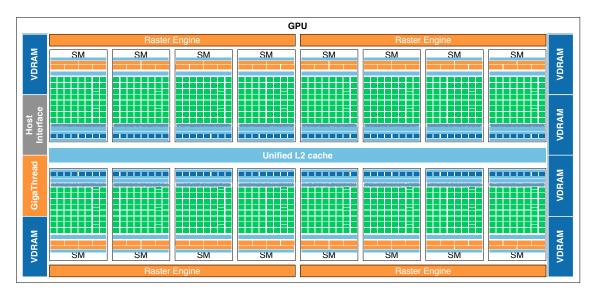

| 4.3        | Fermi GPU overview                                                     | 73     |

| 4.4        | SIMT GPU SM and CUDA core in detail                                    | 73     |

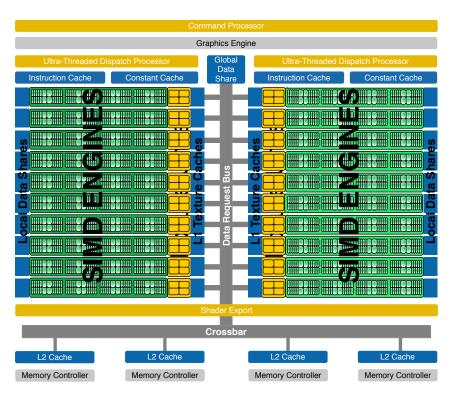

| 4.5        | SIMD GPU architecture in detail                                        | 75     |

| 4.6        | Dual-GPU cluster topology                                              | 77     |

| 4.7        | Execution grid                                                         | 78     |

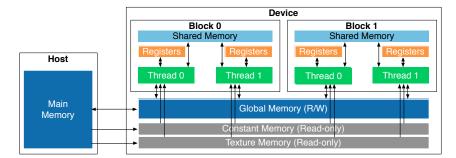

| 4.8        | GPU memory model                                                       | 79     |

| 4.9        | OpenCL abstraction model                                               | 80     |

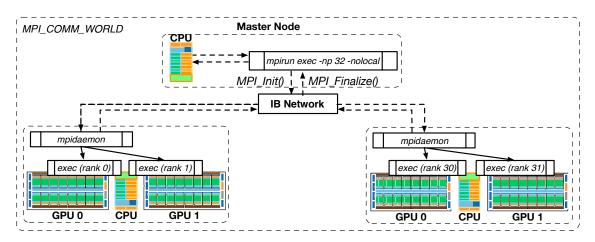

| 4.10       |                                                                        | 81     |

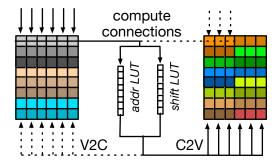

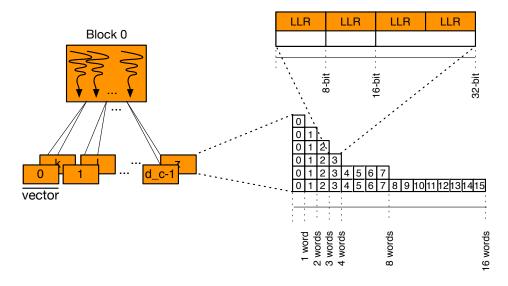

| 4.11       | Memory access to packed LLRs                                           | 86     |

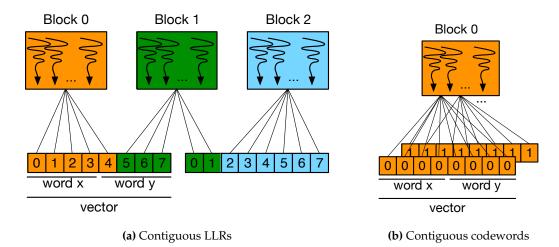

|            | Data-parallelism levels at the vector and execution grid granularities | 86     |

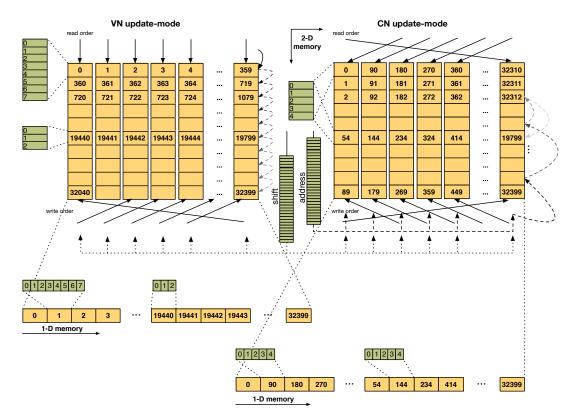

| 4.13       | Memory layout of the DVB-S2 LDPC-IRA codes in a 1-D memory             | 91     |

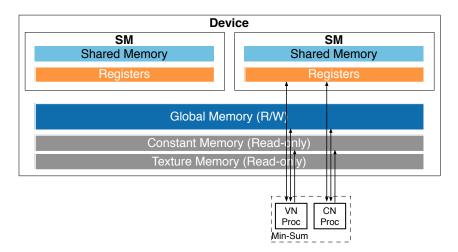

|            | MSA employment of the GPU memory hierarchy                             | 94     |

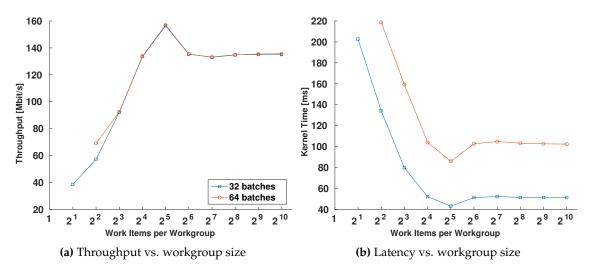

|            | Decoder performance vs. workgroup size                                 | 95     |

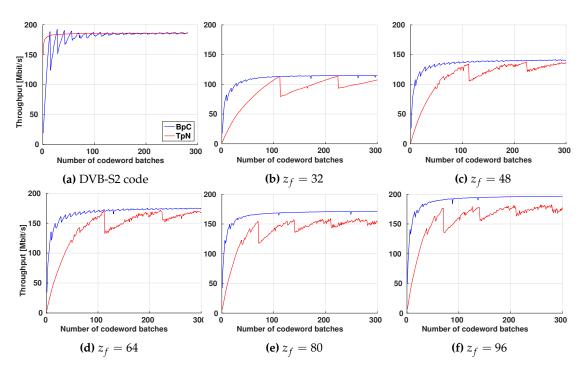

| 4.16       | Single-GPU TpN and BpC decoders throughput (I)                         | 96     |

|                                                                          | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

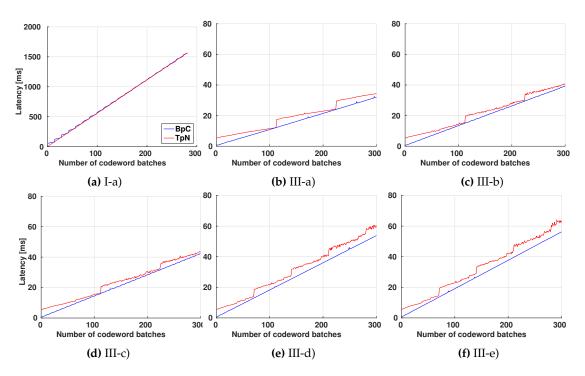

| Single-GPU TpN and BpC decoders latency                                  | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

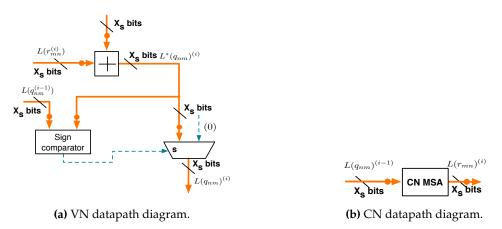

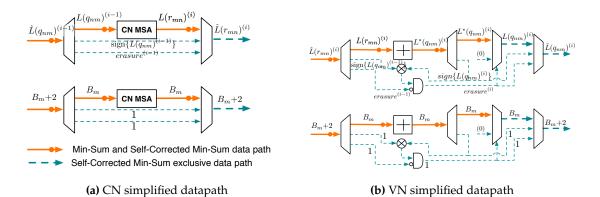

| Non-optimized SCMSA datapath compared to the MSA                         | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

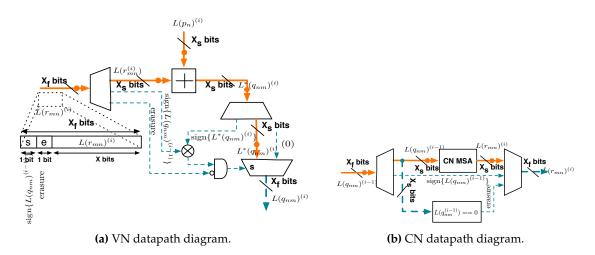

| Optimized SCMSA datapath compared to the MSA                             | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

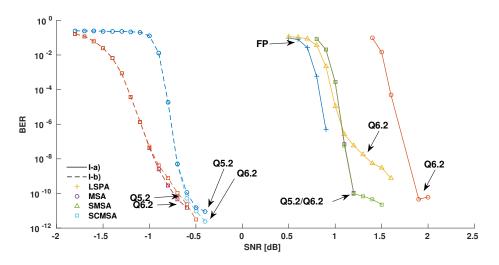

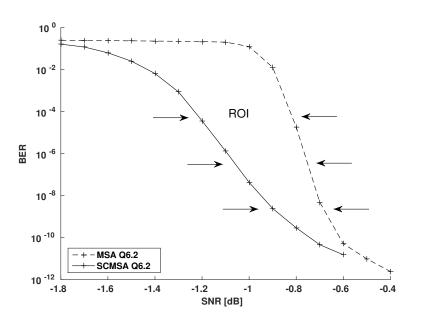

| BER performance comparison of LSPA and MSA-based algorithms              | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

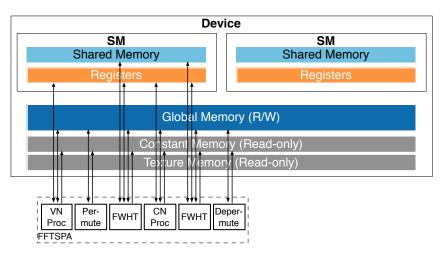

| FFTSPA employment of the GPU memory hierarchy                            | 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

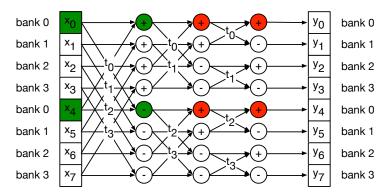

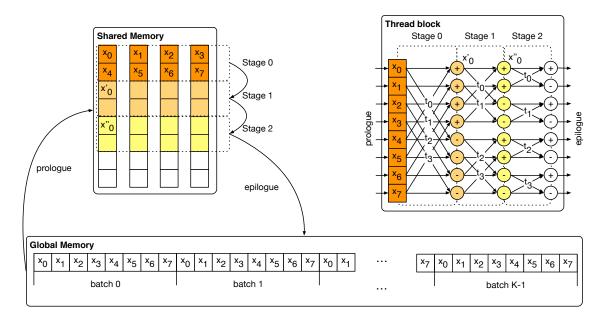

| Shared memory conflicts on the 8-point radix-2 FWHT                      | 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

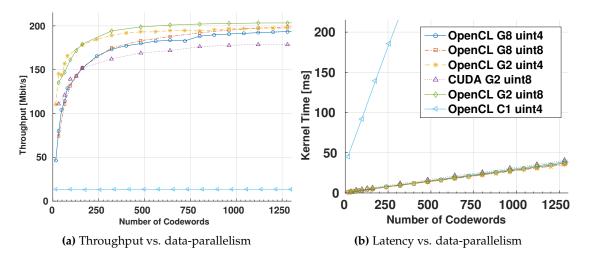

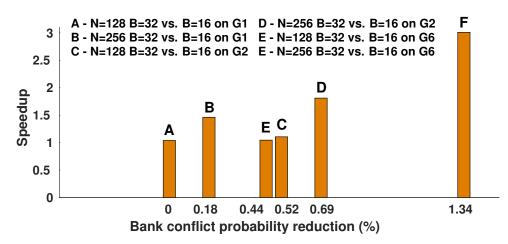

| · ·                                                                      | 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                          | 109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

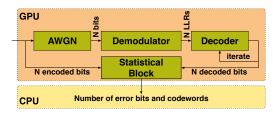

| BER simulation model                                                     | 113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

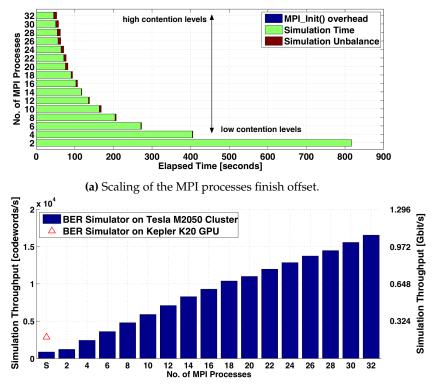

| Cluster BER simulator kernels relative occupancy                         | 117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

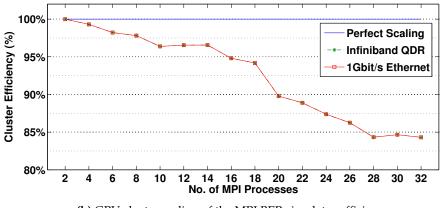

| Cluster MPI execution overhead and computational unbalancing scalability | 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

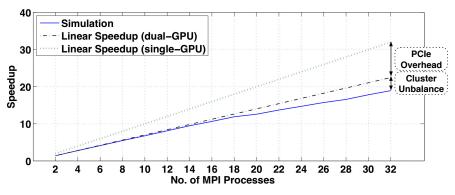

|                                                                          | 120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

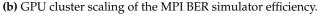

| Cluster simulation time scenarios                                        | 122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

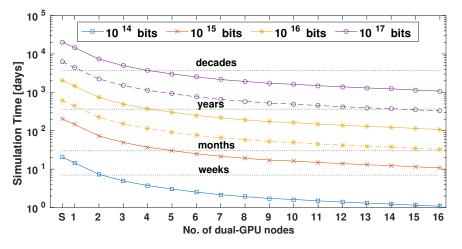

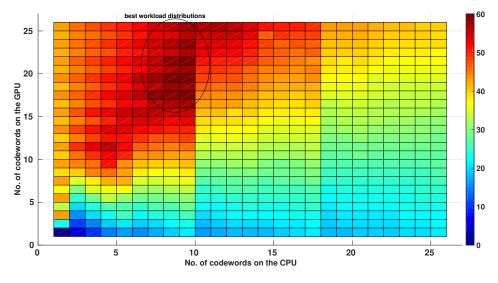

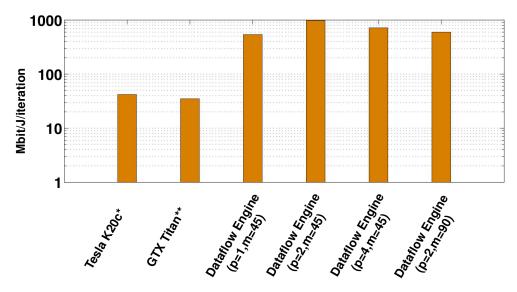

| CPU/GPU decoding throughput vs. workload configuration                   | 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CPU/GPU decoding throughput vs. workload configuration                   | 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

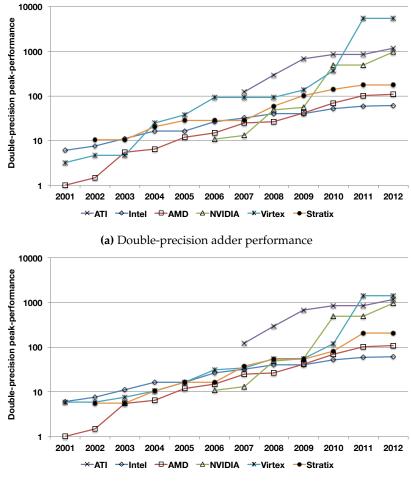

| Arithmetic performance comparison of CPU, GPU and FPGA devices           | 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

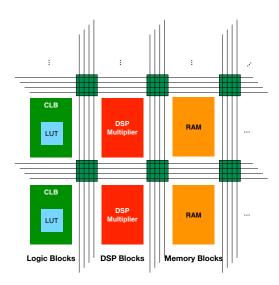

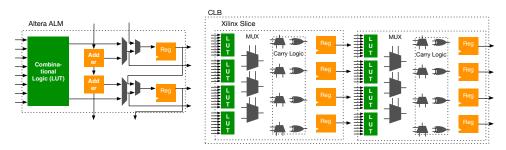

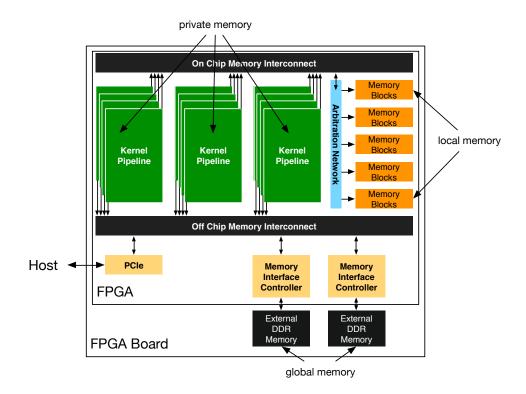

|                                                                          | 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                          | 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

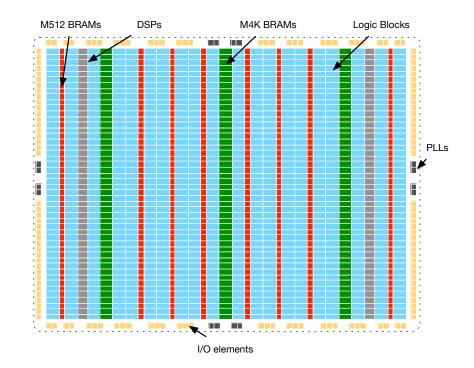

|                                                                          | 133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

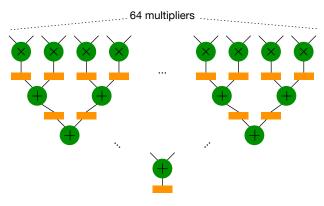

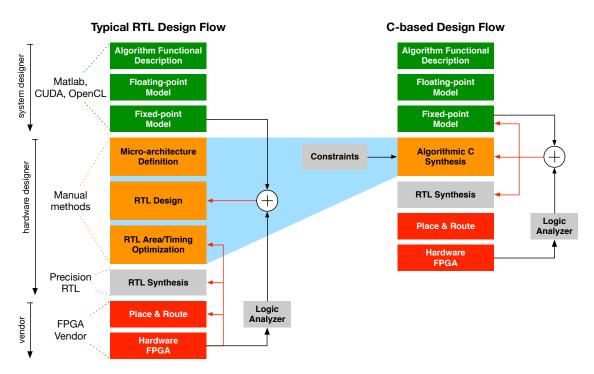

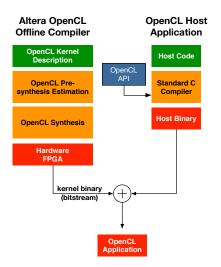

|                                                                          | 135                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

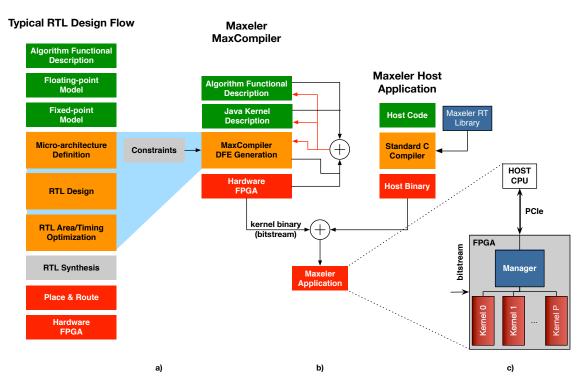

| 0                                                                        | 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

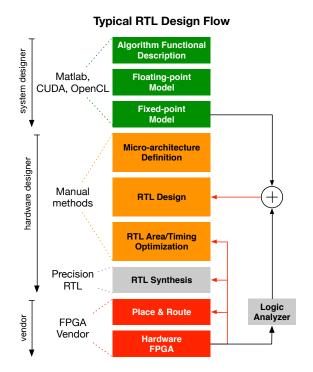

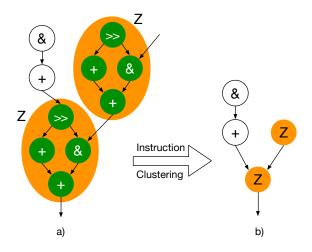

|                                                                          | 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

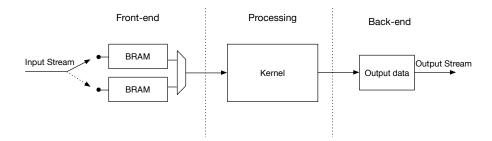

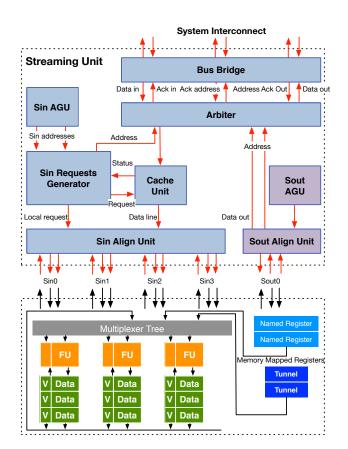

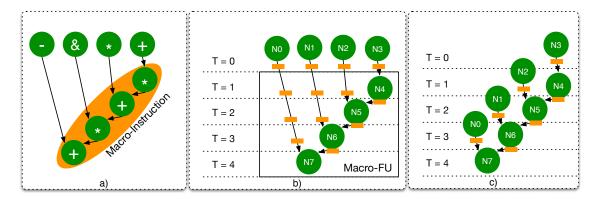

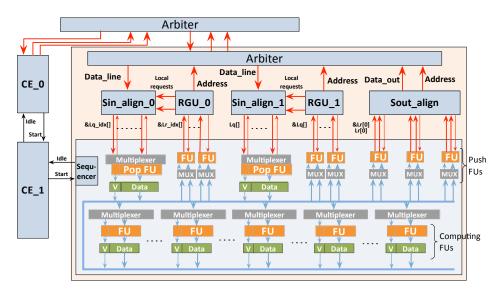

|                                                                          | 142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

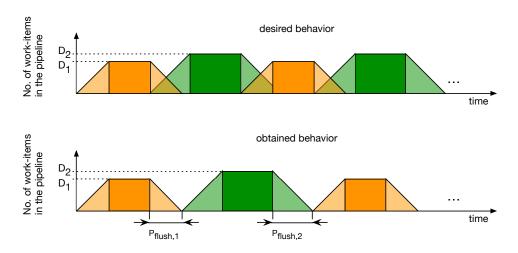

| 1 05                                                                     | 143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

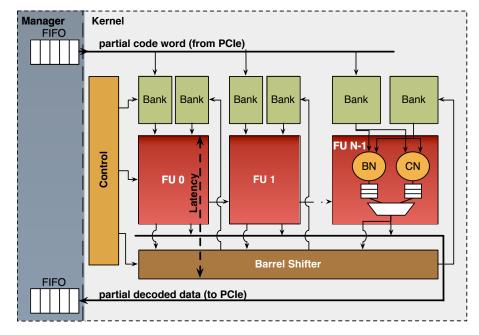

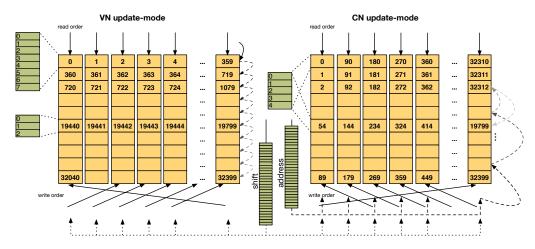

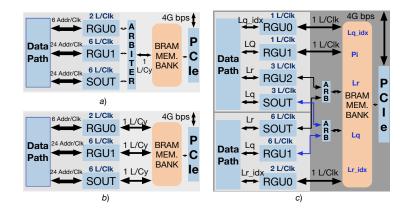

| <i>M</i> -modulo dataflow architecture                                   | 144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

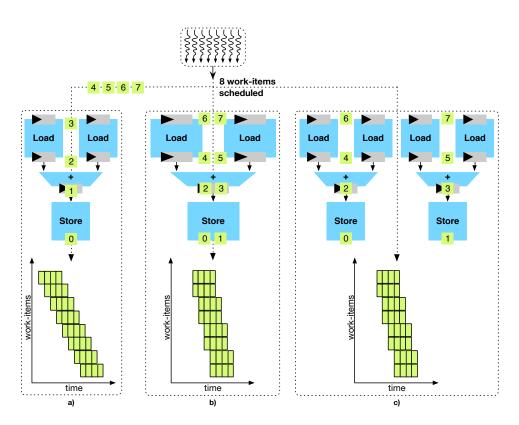

|                                                                          | 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

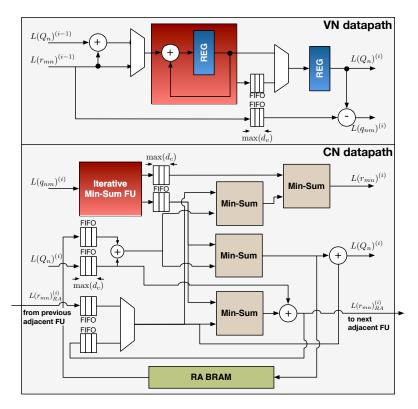

|                                                                          | 146                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

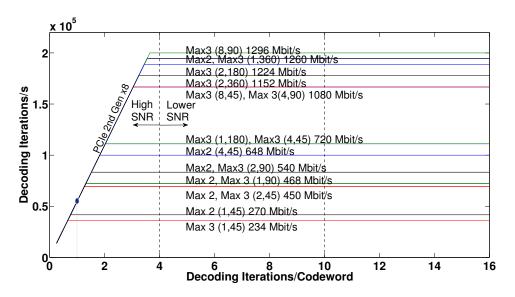

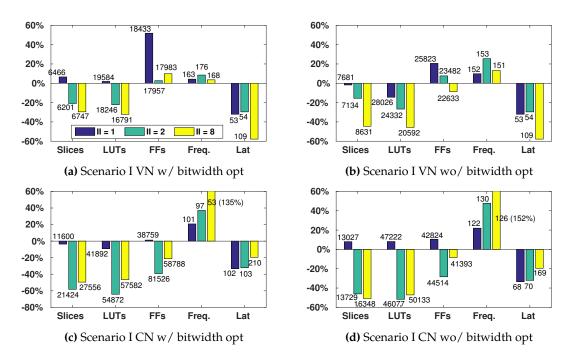

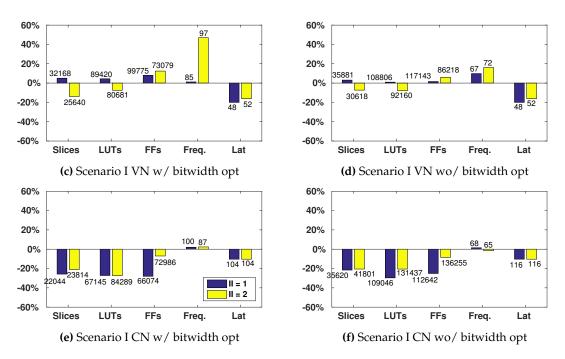

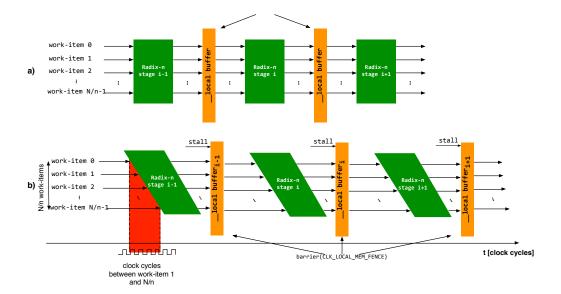

| 5                                                                        | 153                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                          | 154                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

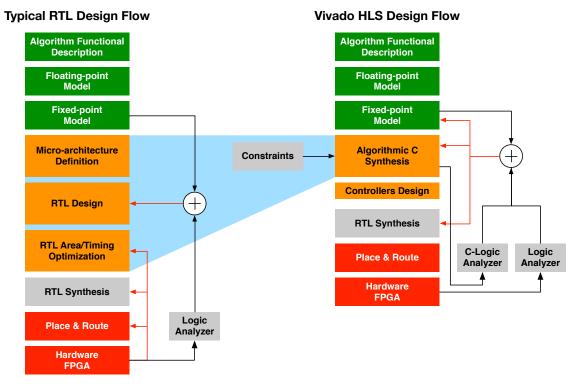

| Vivado HLS design flow for hardware development                          | 156                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

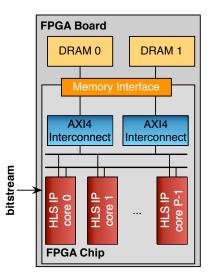

| Template architecture for the loop-annotated LDPC decoder                | 157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

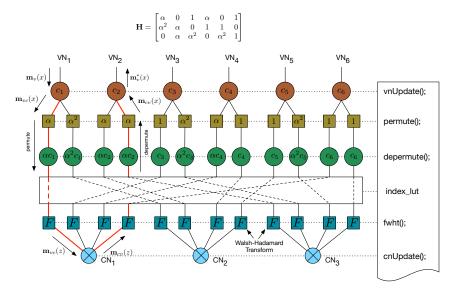

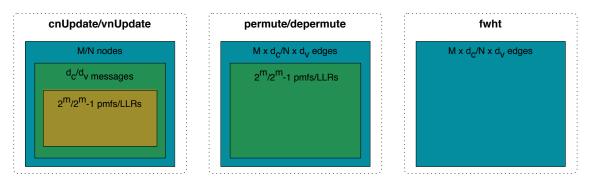

| Vivado HLS isomorphic mapping of the message-passing algorithms          | 158                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

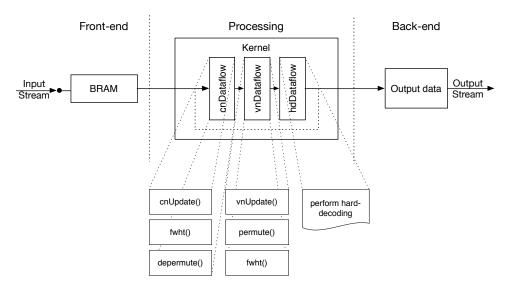

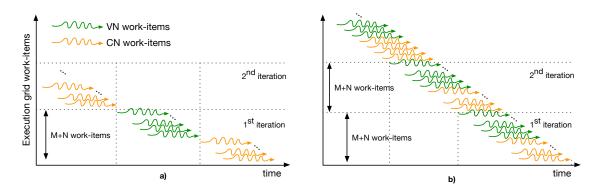

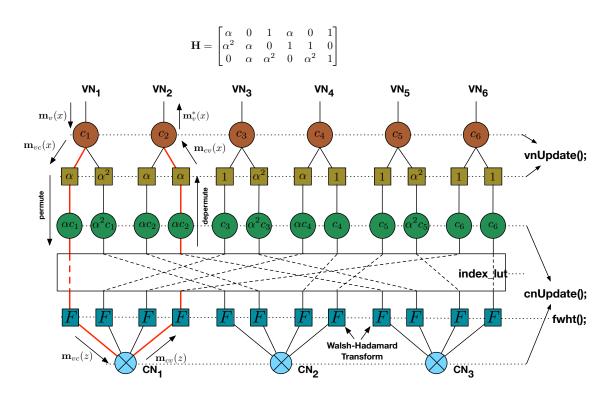

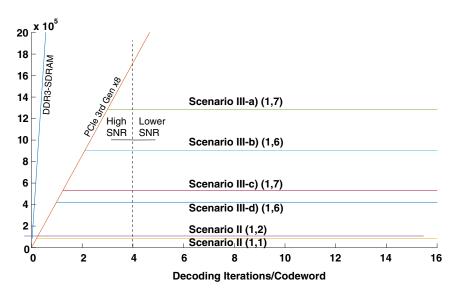

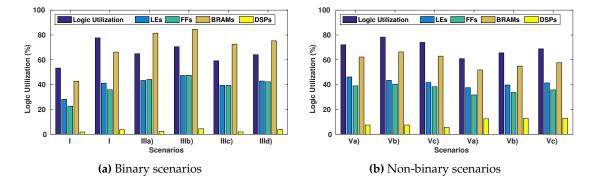

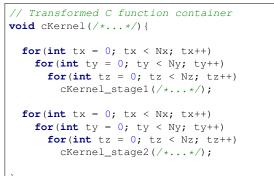

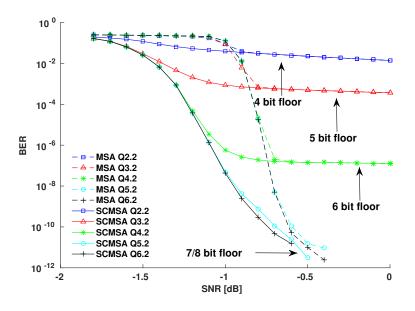

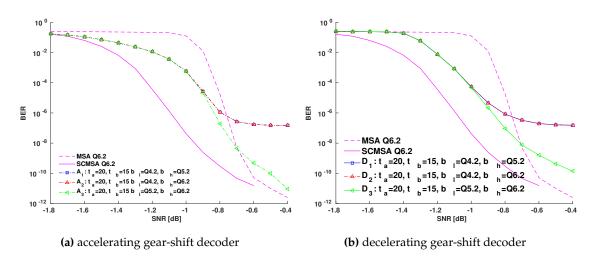

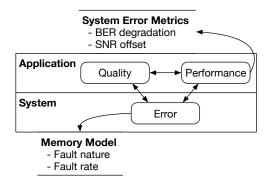

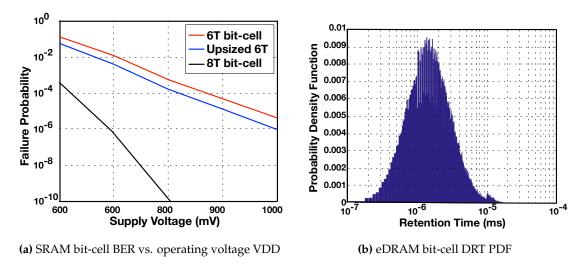

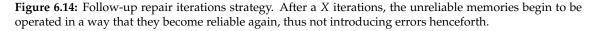

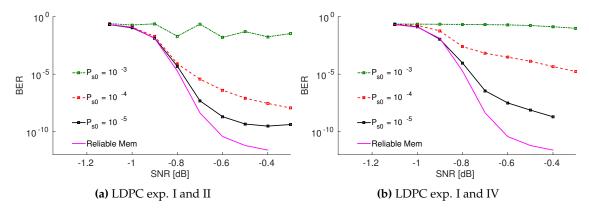

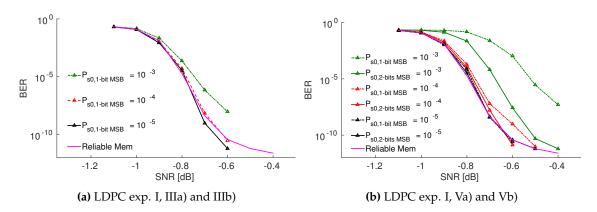

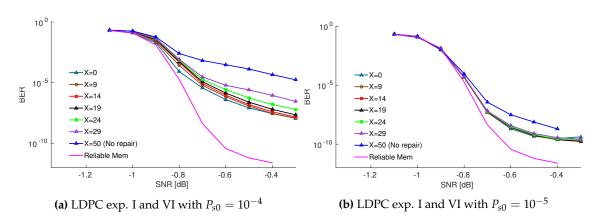

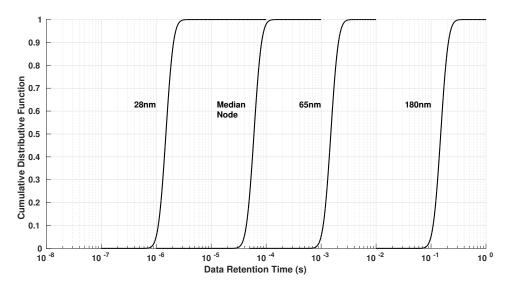

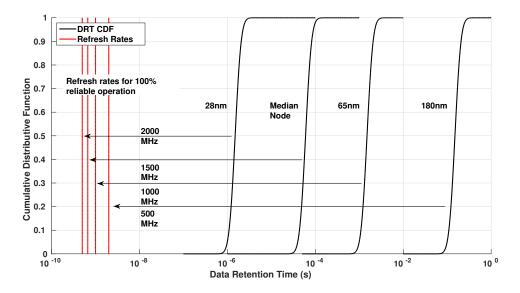

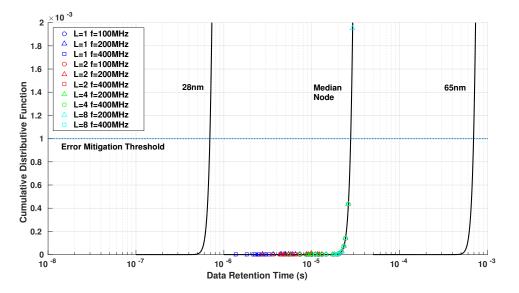

| Dataflow regions within the LDPC decoder accelerator                     | 159                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |