# Interactive Demonstration of a Remote Reconfigurable Logic Laboratory for Basic Digital Design

http://dx.doi.org/10.3991/ijoe.v8iS1.1886

Jorge Lobo

ISR - Institute of Systems and Robotics - University of Coimbra, Coimbra, Portugal

Abstract—In this interactive demonstration we show the usage of a remote reconfigurable logic laboratory for digital design students, presented in a full paper submitted to the conference. A very simple web based approach is used to enable the remote access to a FPGA (Field Programmable Gate Array) development and educational board. The board switches and keys are virtualised with an online web form, and a webcam is used to provide feedback to the user.

*Index Terms*—digital design, FPGA, reconfigurable logic, remote laboratory.

## I. INTRODUCTION

Although modern freely available digital design tools allow for flexible simulation vector editing and easy simulation, for first year students learning digital design the hands-on approach is much more rewarding, and less confusing. But lab class resources are limited, and without flexible working hours. The challenge is to transpose the physical interaction between the user and the equipment of the laboratory to an Internet application interface, as realistic as possible, so that students can interact with a real FPGA board at the lab from anywhere.

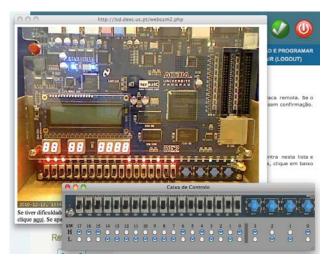

In our case we would like to connect to an ALTERA DE2 FPGA board over the Internet and use it as if the user is *in loco*, programming, testing and looking at it. This board has many switches, keys, LEDs, LCDs and 7-segment displays, and we need to look at it and use the switches and keys, remotely. This was accomplished by developing a webpage interface, with PHP dynamic functionalities that enabled the remote use of the DE2 boards, and a webcam for visual feedback. Fig. 1 presents the key concept.

In our work we take a very simple but effective approach described in the following sections, suitable for the introductory nature of the courses attended by first year students, but not limited to any fixed set of experiments.

In the full companion paper [1] the system is described in more detail and put in context with the current state of the art and the target digital design course.

# II. USING THE REMOTE FPGA LABORATORY

The implemented remote FGPA laboratory is online at <u>http://lsd.deec.uc.pt</u> and will be used for the interactive demonstration. To have access to the hardware a simple registration is required to have a user account. Fig. 2 shows the remote interaction with the DE2 FPGA board.

Figure 1. Basic concept of the reconfigurable logic remote lab: control the board switches and keys and look at the development board.

Figure 2. Screen shot of the remote laboratory interaction with the FPGA board.

A webcam conveys the realtime results, and the board switches and keys are virtualised. Students use a free webedition version of the Altera Quartus II digital design IDE, and just upload the final programmer file (.sof). The only change they have to perform to the project is to use a component that virtualises the board switches and keys.

The DE2 Web Server is located in our campus LAN and is accessible through the Internet, so that anyone from anywhere can remotely access the lab. The server is connected via USB to the FPGA JTAG port on the DE2 board, and the webcam connects to the server using another USB port.

### SPECIAL FOCUS PAPER

### INTERACTIVE DEMONSTRATION OF A REMOTE RECONFIGURABLE LOGIC LABORATORY FOR BASIC DIGITAL DESIGN

#### A. Adapting the Design to Run on the Remote Board

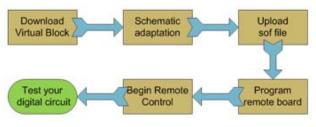

To test a digital circuit on the remote laboratory instead of directly on the DE2 board the project design needs to take into account the virtualized switches and keys, following the steps shown in Fig. 3.

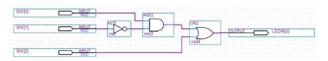

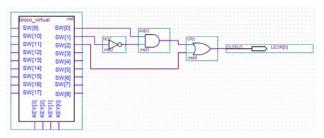

Before programming the remote board with the digital design compiled on Altera Quartus II, the user needs to modify the schematic in order to make the input pins liable to be changed via JTAG, instead of changed physically with the board switches and keys. In order for that, the user needs to download the virtual block and connect to it the input pins that corresponded to board switches and keys. This is shown for a simple combinational circuit on Fig. 4, the original circuit, and Fig. 5, the same circuit using the virtual block.

This is done in schematic design entry, and there is no limit on the design complexity, as long as the slow actuation of switches and keys, and visual feedback of the board is sufficient to test the circuit. If the project is in VHDL or Verilog, the top-level file needs to be encapsulated in a block and placed into a new top-level schematic file connected with the virtual block for the virtual inputs.

After this simple adaptation, the user can login and upload the compiled .sof file to the server, reconfigure the FPGA and begin the remote control.

#### B. Circuit Upload and Interaction with Remote Board

To have access to the hardware the user must register and have the request accepted by the administrator. For students attending the course this can be done in class with a batch auto-validation mode available to the administrator. The hardware access policy is single user time limited login, meaning that two or more users cannot access and control the remote board simultaneously. The license expires after 5 minutes, enough time to test the circuit, after which a new login is accepted on a first come first served basis. Users trying to login are informed of the remaining time when the hardware is already being used, and must try again later. This monitoring is an alternative to a queue system that is not yet implemented.

Once the .sof file is programmed in the remote board, the user can open the control box and the Webcam applet box. The control box has a total of twenty-two buttons, in which the eighteen switches and the four keys are simulated in the same way, since coding the keys in PHP was not practical. Fig. 2 shows a simple circuit that connects the switches to the red LEDs and the keys to the green LEDs, notice the pattern on the control windows buttons and the LEDs on the webcam image. One of the limitations of the current virtual control system is that it takes one second for the change on a button to take effect on the board. This limitation is due to the simple approach taken that only requires a minimal virtual block and no additional hardware.

#### III. SUMMARY

The demo will show a simple but effective implementation of a digital design laboratory. Depending on the interest of the exhibition visitors, simple designs or more complex ones can be uploaded and tested on the remote FPGA. The remote laboratory provides a reconfigurable logic device using an Altera DE2 FPGA board. The sys-

Figure 3. Diagram of the user required steps to test a digital circuit.

Figure 4. Simple combinational initial circuit.

Figure 5. Simple combinational circuit using virtual block.

tem is targeted at introductory courses of digital design where a simple webcam can provide the feedback from the FPGA board LEDs and displays, and the board switches are virtualised for remote web control. Its use can range from simple combinational circuits to more complexcontrollers and processors with datapaths. The only limit is on the interface provided by the virtualised switches input response time and visible elements in the webcam image.

#### ACKNOWLEDGMENT

The author would like to acknowledge the valuable contribution of João Soares in programming the remote laboratory server.

#### REFERENCES

Jorge Lobo, "A Remote Reconfigurable Logic Laboratory for Basic Digital Design". in Proceedings of the 1st Experiment@ International Conference - Remote & Virtual Labs - exp.at'11, Lisbon, Portugal, November 2011.

#### AUTHORS

**Jorge Lobo** is with the ISR - Institute of Systems and Robotics, DEEC - Dep. Electrical and Computer Eng., FCT - Faculty of Sciences and Technology, Polo II, University of Coimbra, 3030-290 Coimbra, Portugal (email: jlobo@isr.uc.pt).

This work is a description of a demonstration given during 1<sup>st</sup> Experiment@ International Conference, 17/18 November 2011 in Lisbon, Portugal.It was supported by Calouste Gulbenkian Foundation, Lisbon, Portugal. The work leading to these results was partially supported by the Portuguese Foundation for Science and Technology (FCT), with an undergraduate student research initiation scholarship for João Soares (BIL/UNI/0048/EEI/2009/B02), and by the Institute of Systems and Robotics at Coimbra University. Received 01 December 2011. Published as resubmitted by the authors 20 January 2012.